| cadence OrCAD原理图输出 | 您所在的位置:网站首页 › cadence网表导入pads › cadence OrCAD原理图输出 |

cadence OrCAD原理图输出

|

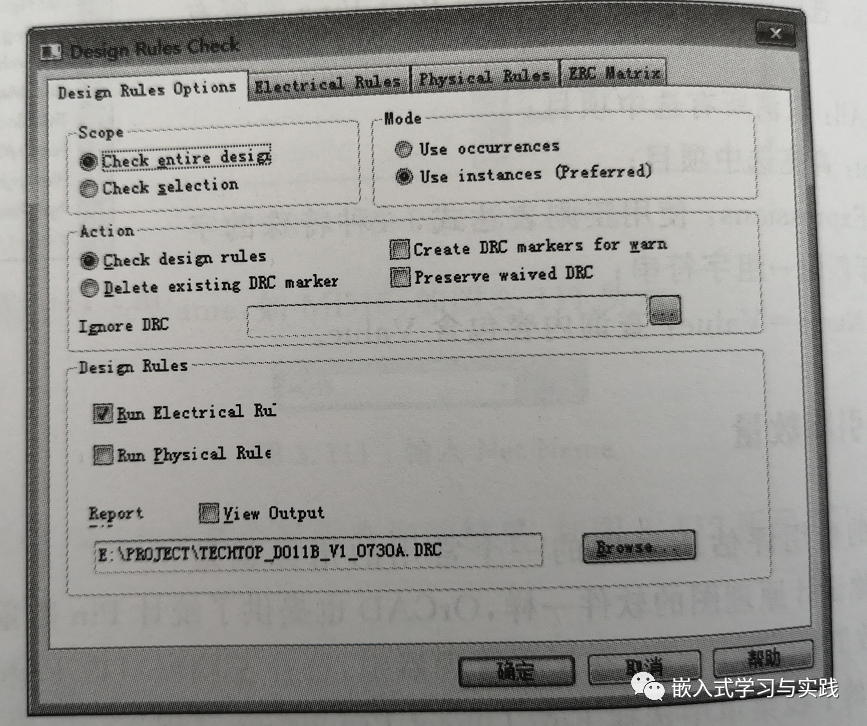

一、输出前DRC检查 使用orcad设计完原理图,进行网表输出前需要先DRC检查。DRC检查主要是对各种设计Rule的检查,查用的检查如原件的位号是否重复,以及是否有单网络(Single Net)等。 如果有错误,生成网表文件会失败!!! 在项目管理器中,选择dsn文件,在主菜单中选择Tools-Design Rules Check选项,出现Design Rules Check对话框,进行drc规则配置。共有四部分,如下图:

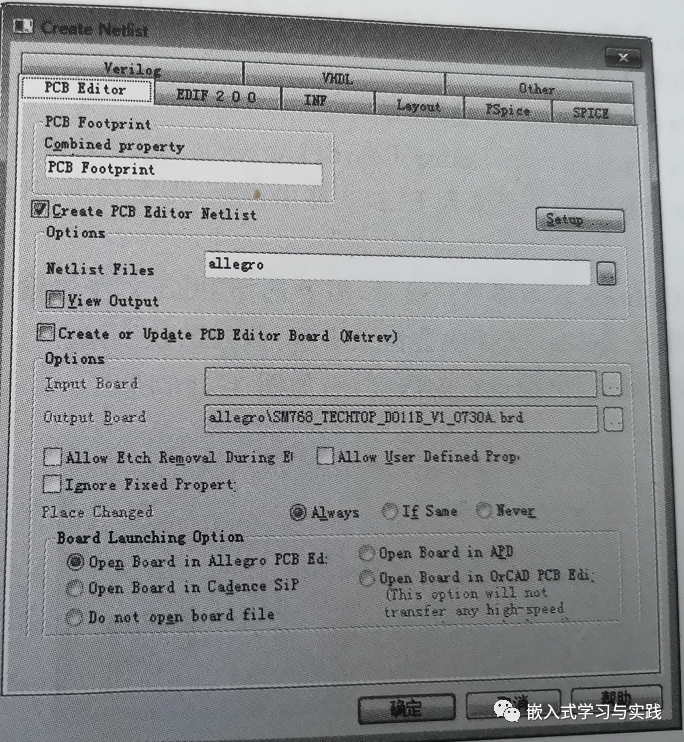

二、网表Netlist文件输出 在项目管理器中,选择dsn文件,在主菜单中选择Tools-Creat Netlist选项,弹出Creat Netlist对话框。一般情况下,配置PCB Editer部分即可。

配置好,选择确定会出现进度条,运行结束后,在Output内可以看到有3个扩展名为 dat 的Netlist文件。同时在 dsn 文件同目录下,新出现了allegro文件夹,打开也会看到这3个文件。 OrCAD的Netlist文件有3个,与其他软件生成的Netlist文件不同。这3个文件内容如下: pstxnet.dat-Net、Pin和位号的互联信息; pstxprt.dat-Part和位号的对应关系; pstchip.dat-Part的属性信息。 新人或不熟悉的还是要通过选择修改原理图来更新PCB文件,熟悉了之后可以直接修改Netlist文件来更新PCB文件。 欢迎关注公众号:嵌入式学习与实践 参考: drc规则:https://blog.csdn.net/wsq_666/article/details/118405328 网表:https://blog.csdn.net/wsq_666/article/details/118496374 Cadence高速PCB设计-基于手机高阶板的案例分析与实现 |

【本文地址】

公司简介

联系我们