| 东芝线阵CCD芯片TCD1305DG驱动时序设计 | 您所在的位置:网站首页 › c51驱动线性ccd › 东芝线阵CCD芯片TCD1305DG驱动时序设计 |

东芝线阵CCD芯片TCD1305DG驱动时序设计

|

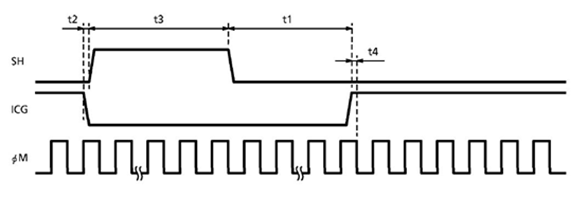

最近在做微型光谱仪,用到了东芝的CCD芯片TCD1305DG,该芯片是单行3648像素,输出信号是时间上离散的模拟信号,典型输出速率为0.5M,即每2000ns输出一个像素值(模拟信号),芯片内部集成了相关双采样电路,直接输出稳定的像元电压值,而不是传统的三阶梯信号。TCD1305DG需要三路驱动信号,分别是主时钟CLK,移位输出信号SH,积分清除信号ICG,芯片手册上给出的时序波形如下:

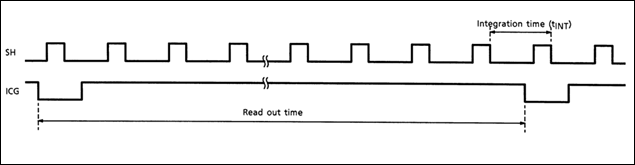

图1 TCD1305DG驱动时序 该CCD的基本工作原理如下:光敏元接收外部光信号并将其转换为电荷储存在光敏元下方的电子势阱中,当积分清除栅ICG为低电平时,如果检测到转移栅SH信号下降沿,就会将电子势阱中积累的电荷转移到模拟移位寄存器中,等待ICG回到高电平后,模拟移位寄存器中的电荷就在主时钟CLK作用下逐个的输出到OS管脚上,每四个主时钟周期输出一个像素电压值,所以ICG的高电平的持续时间需保证所有的像素电荷都已经输出,故ICG的高电平持续时间称为转移时间。而ICG低电平时SH的下降沿到SH的前一个下降沿之间的时间间隔称为积分时间(如图2所示),在这段时间里光敏元不断地积累电荷,线阵CCD的成像效果与积分时间有着密切的关系。

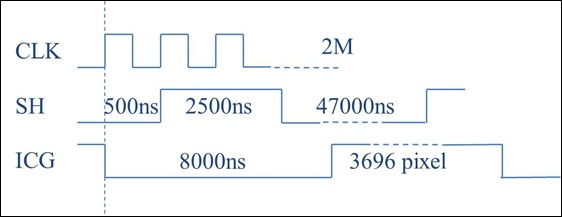

图2 积分时间示意图 一. TCD1305DG驱动时序设计 本设计中根据TCD1305DG芯片手册将积分时间设为50us,主时钟周期为500ns,取图1中的t2为500ns,t3为2500ns,ICG低电平持续时间为8000ns,ICG高电平期间输出3696个像素值(实际上只有3694个像素,此处取为3696是为了与SH信号同步:3696 X (500 X 4) + 8000 = N*50us)。三路驱动信号的波形图设计如下:

图3 驱动信号波形设计参数 下面分别介绍这三路信号的产生方法: 1. 主时钟CLK 主时钟CLK周期为2M,可以直接对晶振分频得到,此处采用100M晶振,对其50分频就可以得到2M的时序信号,设计verilog代码如下: //------------generate CCD_CLK, 2M------------------- reg [5:0] cnt_clk; always @ (posedge clk or negedge rst_n) if(!rst_n) cnt_clk |

【本文地址】