| 基于FPGA线性调频信号LFM的产生 | 您所在的位置:网站首页 › ad9379线性调频信号 › 基于FPGA线性调频信号LFM的产生 |

基于FPGA线性调频信号LFM的产生

|

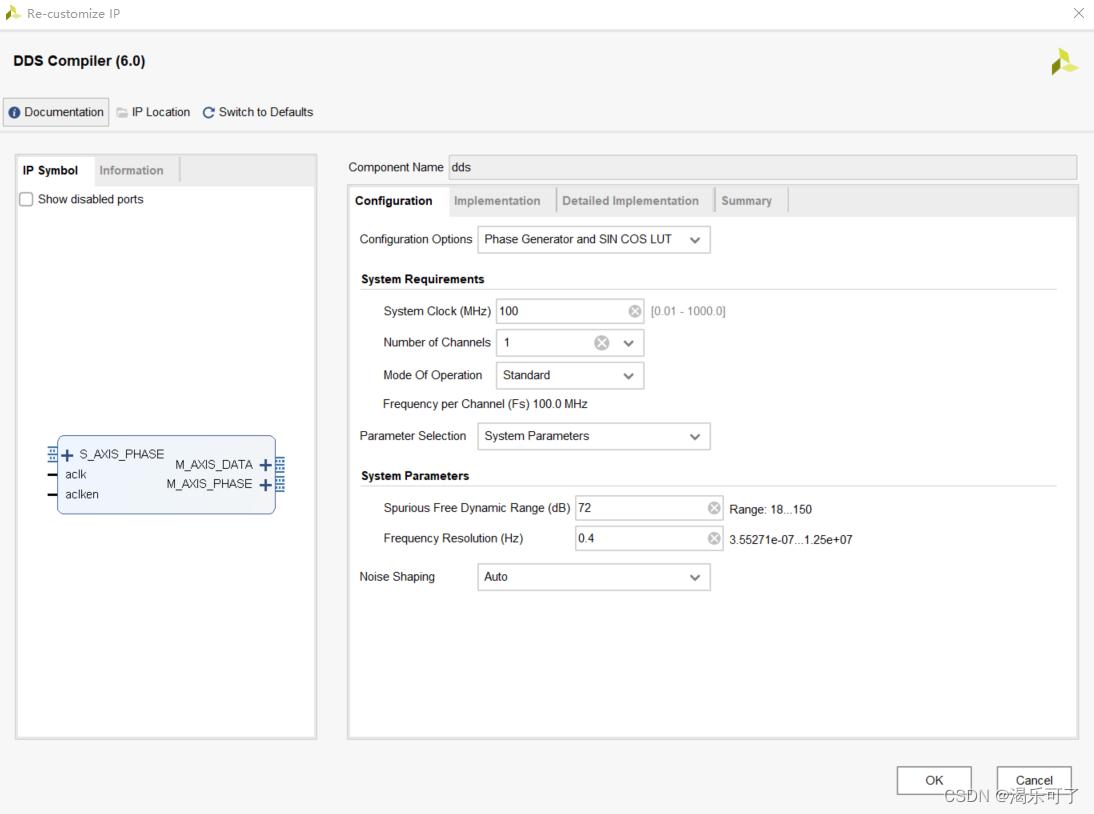

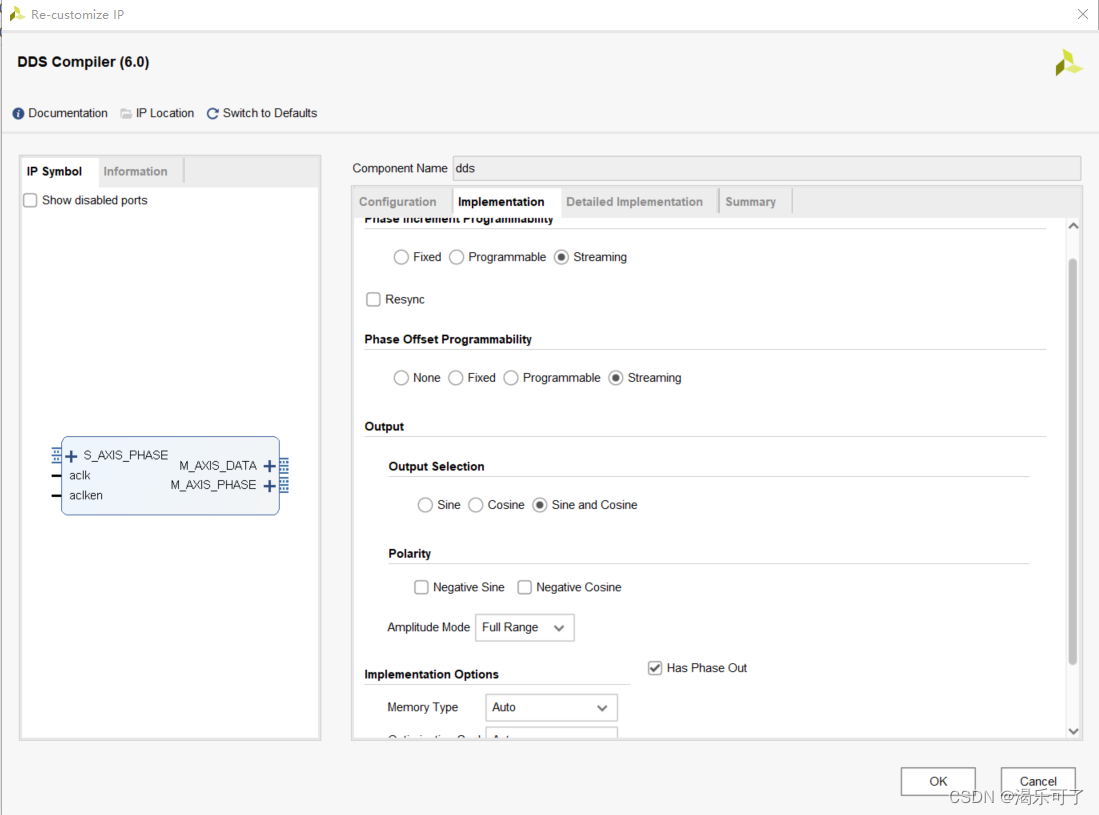

本文用了DDS来产生LFM信号,DDS的原理可以查看赛灵思的官方文档,这里不做赘述,同时对于LFM信号也不做赘述,直接上工程实现及其方法。 首先,我们要确定脉宽和PRI,在这里脉宽选取10us,PRI选取200us(fpga内部时钟用来100MHz),所以使用计数器去实现这两个信号的计数,当计数器计数到一定值的时候,使用使能信号来反应该计数状态,根据使能信号和成脉冲门信号,在脉冲门信号里面对DDS进行频率的步进,达到最后的输出效果。 DDS配置如下:

其余保持默认配置 `timescale 1ns / 1ps // // Company: xidian // Engineer: CC // // Create Date: 2023/04/29 20:03:54 // Design Name: // Module Name: lfm_gen // Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // // module lfm_gen #( parameter CNT_TAO_MAX = 10'd999, parameter CNT_PRI_MAX = 15'd19_999 //实际pri=(19999+1)*10ns*2=400us ) ( input wire sys_clk, input wire sys_rst_n, // output wire meng, // output wire [31:0]data, // output wire [15:0]sin_imag, // output wire [15:0]cos_real, output wire wr_en, output wire [13:0]data_out, output wire clk_125M ); reg pri_en; reg tao_en; reg cnt_ctrl1; //脉宽前沿检测 reg cnt_ctrl2; //脉宽后沿检测 reg cnt_ctrl3; //PRI后沿检测 reg [9:0]cnt_tao; reg [14:0]cnt_pri; reg [7:0]tao_reg; //一个周期内对脉宽的计数 reg freq_en; reg [31:0]dds_pinc_in; reg [31:0]dds_poff_in; wire [63:0]s_axis_phase_tdata; parameter FREQ_START = 32'd858_993_460; //起始频率为20MHz parameter FREQ_STEP = 32'd214_749; //步进频率为5KHz wire [31:0] data; wire meng; wire [15:0]sin_imag; wire [15:0]cos_real; wire [13:0]data_reg; //pri计数器,产生对应时间的脉冲间隔 always@(posedge sys_clk or negedge sys_rst_n) if (sys_rst_n == 1'b0) cnt_pri |

【本文地址】

公司简介

联系我们