| FPGA | 您所在的位置:网站首页 › abc到dq坐标变换原理 › FPGA |

FPGA

|

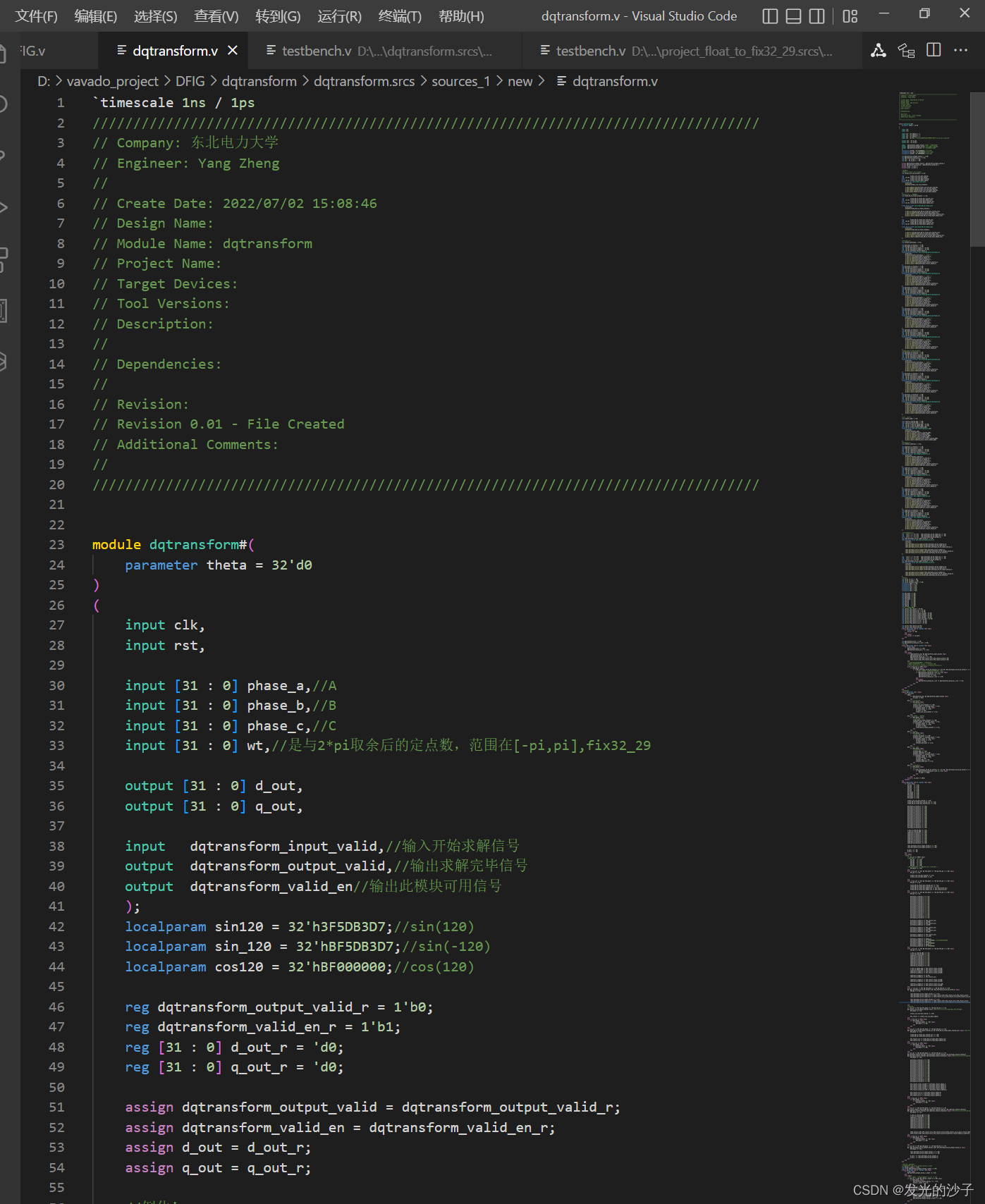

1、本人采用Verilog实现了abc-dq、dq-abc、极坐标与笛卡尔坐标、低通滤波器、取余函数、最大值、最小值、PI比例积分器的模块编写,接下来几篇会将测试代码与测试结果一一列出,大家有需要请查看我的个人资料。 下面链接是github上的一个开源科学函数(包含abc-dq,乘法、除法、三角函数、PI控制器),然而我不会用!https://github.com/hVHDL/hVHDL_math_library 2、实验任务:完成abc坐标系向dq坐标系的转换 实验软/硬件:vivado 2019.1、ZCU106 实验过程:

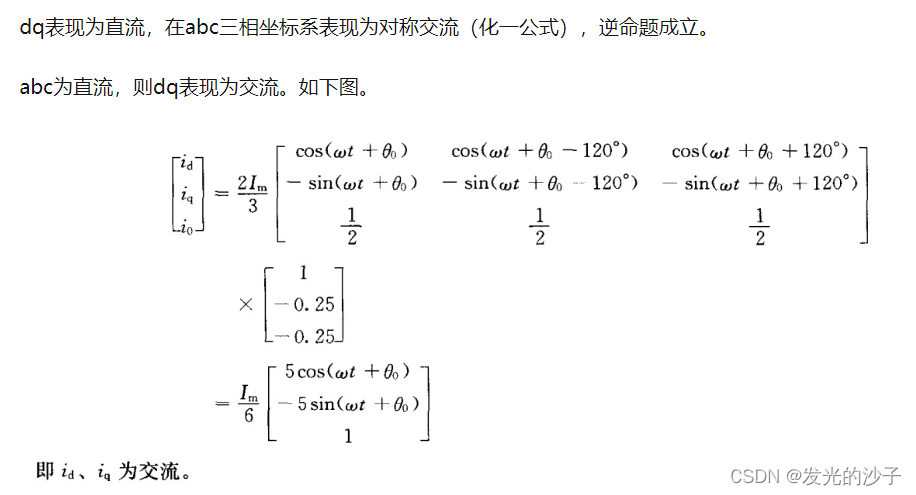

上图表示了一个abc坐标系通过park变换转到dq0坐标系的例子,由于我课题做的是电机类,因此默认对称不存在0轴,因此我的代码也只编写了abc-dq轴的部分。 实验代码截图: 需要请联系我的邮箱。 测试代码: `timescale 1ns / 1ps // // Company: 东北电力大学 // Engineer: Yang Zheng // // Create Date: 2022/07/02 22:12:30 // Design Name: // Module Name: testbench // Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // // module testbench( ); // dqtransform Parameters parameter PERIOD = 10 ; parameter theta = 32'd0; // dqtransform Inputs reg clk = 0 ; reg rst = 0 ; reg [31 : 0] phase_a = 0 ; reg [31 : 0] phase_b = 0 ; reg [31 : 0] phase_c = 0 ; reg [31 : 0] wt = 0 ; reg dqtransform_input_valid = 0 ; // dqtransform Outputs wire [31 : 0] d_out ; wire [31 : 0] q_out ; wire dqtransform_output_valid ; wire dqtransform_valid_en ; initial begin forever #(PERIOD/2) clk=~clk; end initial begin #(PERIOD*2) rst = 1; end dqtransform #( .theta ( theta )) u_dqtransform ( .clk ( clk ), .rst ( rst ), .phase_a ( phase_a [31 : 0] ), .phase_b ( phase_b [31 : 0] ), .phase_c ( phase_c [31 : 0] ), .wt ( wt [31 : 0] ), .dqtransform_input_valid ( dqtransform_input_valid ), .d_out ( d_out [31 : 0] ), .q_out ( q_out [31 : 0] ), .dqtransform_output_valid ( dqtransform_output_valid ), .dqtransform_valid_en ( dqtransform_valid_en ) ); always @(posedge clk or negedge rst) begin if (!rst) begin end else begin if (dqtransform_valid_en) begin dqtransform_input_valid |

【本文地址】

公司简介

联系我们