| 总线通信协议 | 您所在的位置:网站首页 › PCI总线特点 › 总线通信协议 |

总线通信协议

|

文章目录

1.简介1.1 总线特点1.2 总线接口1.3 拓扑模式

2. 传输协议3. 小结

1.简介

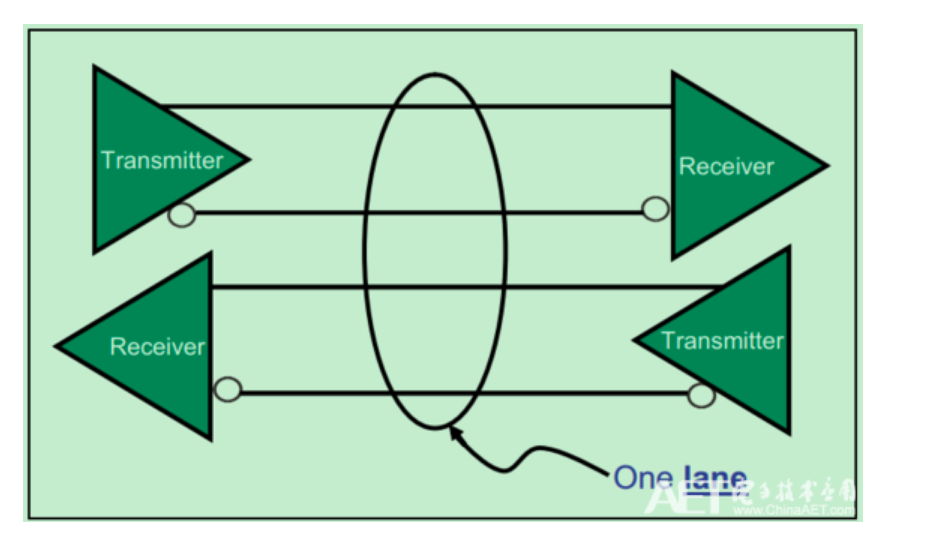

采用串行同步全双工的传输方式,工作频率可以达到2.5GHz。 1.1 总线特点 代表着传统并行总线向高速串行总线发展的时代的到来为了兼容之前的PCI总线设备,虽然PCIe是一种串行总线,无法再物理层上兼容PCI总线,但是在软件层上面却是兼容PCI总线的和很多的串行总线一样,PCIe采用了全双工的传输设计,即允许在同一时刻,同时进行发送和接收数据。 1.2 总线接口设备A和设备B之间通过双向的Link相连接,每个Link支持1到32个通道(Lane)。由于是串行总线,因此所有的数据(包括配置信息等)都是以数据包为单位进行发送的。采用了差分对进行收发,以提高总线的性能。 Rx(D+):接收端口高电平线 Rx(D-):接收端口低电平线 Tx(D+):发送端口高电平线 Tx(D-):发送端口低电平线

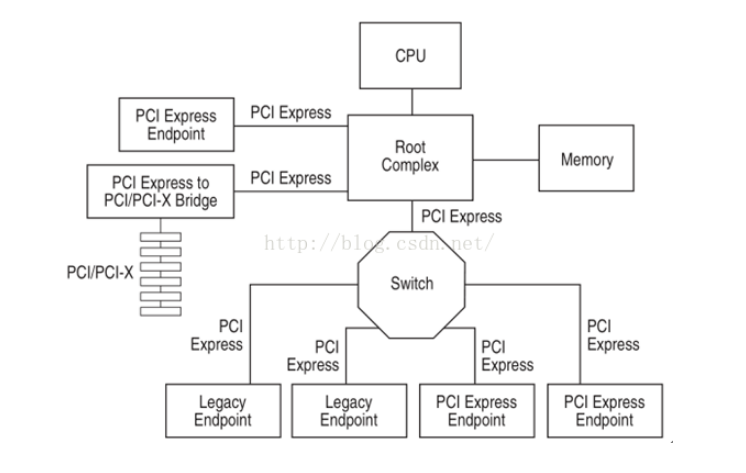

PCIe总线的基本结构包括根组件(Root Complex)、交换器(Switch)和各种终端设备(Endpoint)。根组件可以集成在北桥芯片中,用于处理器和内存子系统与I/O设备之间的连接,而交换器的功能通常是以软件形式提供的,它包括两个或更多的逻辑PCI到PCI的连接桥(PCI-PCI Bridge),以保持与现有PCI兼容。下图即为PCie总线的拓扑结构图。目前,几乎除了与内存的连接之外,其他的连接都是使用PCie总线的

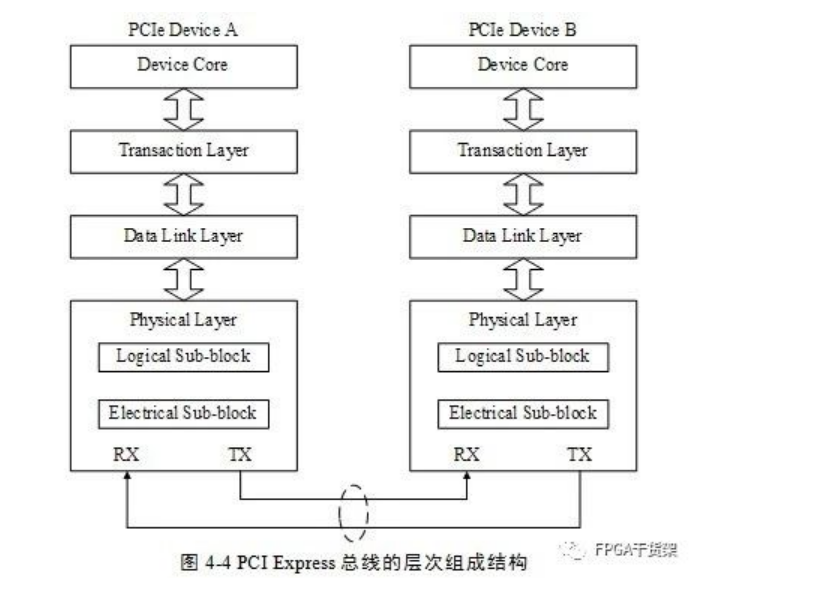

PCIe的连接是建立在一个单向的序列的(1-bit)点对点连接基础之上,这称之为通道(lane)。这一点上PCIe连接与早期PCI连接形成鲜明对比,PCI连接基于总线控制,所有设备共享双向32位并行总线。PCIe是一个多层协议,由事务层,数据交换层和物理层构成。为了便于跨平台使用,PCIe总线体系结构采用分层设计。PCIe体系结构如图2所示。它共分为四层,从下到上分别为:物理层(Physical Layer)、数据链路层(Link Layer)、处理层(Transaction Layer)和软件层(Software Layer) 参考链接: https://blog.csdn.net/chris_leeYC/article/details/47809285 |

【本文地址】

公司简介

联系我们