| 双脉冲测试 MOSFET 的功率损耗 | 您所在的位置:网站首页 › MOS的VDS计算 › 双脉冲测试 MOSFET 的功率损耗 |

双脉冲测试 MOSFET 的功率损耗

|

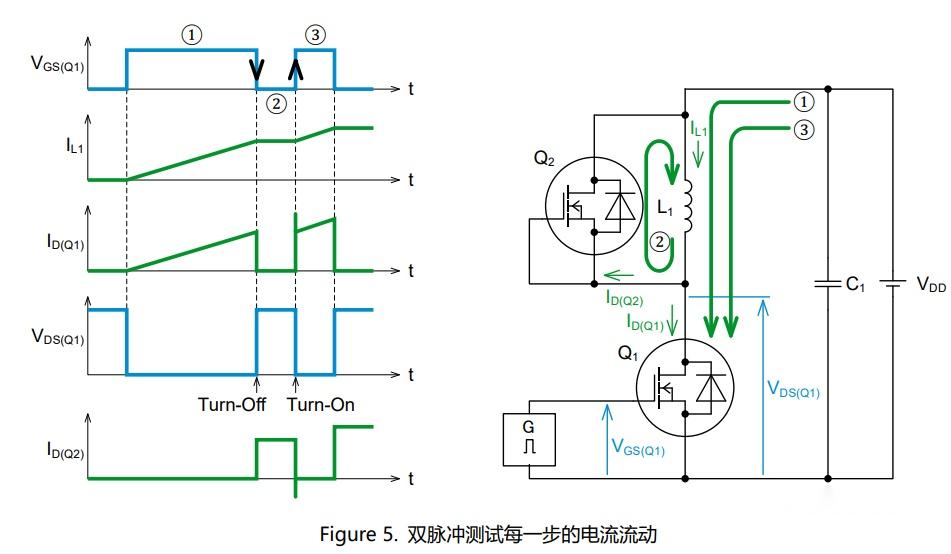

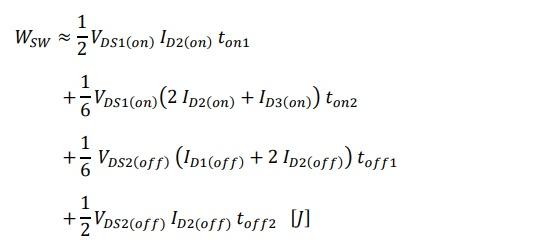

上图是双脉冲测试波形。 关断时间 toff:从 VGS 下降到 90%开 始,到 VDD 下降 10%为止。 延迟时间 td(off):Vgs的90%到VDS 下降到 VDD 的 10%为止。 下降时间 tf:VDS 从 90%到 10%的变化。 导通时间 ton:从 VGS 上升 10%到 VDD 下降 90%。 延迟时间 td(on):Vgs的10%到VDD 下降到 90%下。 上升时间 tr:VDS 从 10%到 90%变化的地方定义为上升时间 tr。 步骤①:第一步是第一次开启区间。低边 SiC MOSFET Q1 接 通后,电源将向电感器供电。这时流向电感器的电流产生磁场, 将电能转换成磁能,并储存在电感器中。由于电感器电流与时 间成比例地增加,为了达到所需测试电流(ID),调整该区间的 脉冲宽度。 步骤②:第二步是第一次的关断区间。Q1 关断后,电感器中累积的磁能量会作为电流释放出来。电流通过续流二极管再次回 流到电感器。这种情况下的续流二极管是高边 SiC MOSFET Q2 的体二极管。该区间的脉冲宽度尽量缩短,使负载电流尽可能 接近一定。此外,还需要确保 Q1 的关机时间,因此设置满足 两个条件的时间。 步骤③:第 3 步是第 2 次导通区间。Q1 导通后,在 ID 波形中 观察到过冲,这是直到前不久,在 Q2 的体二极管中顺向电流 导通的电流切换为反阻挡状态时,短时间反向导通的逆恢复电 流。这是通过高边 SiC MOSFET 的 ID(Q2)测量的。Q1 接通后, 电源再次向电感器供电。然后 ID从步骤②回流的电流值再次开 始增加。脉冲宽度要比第一脉冲短,以免设备因过电流和热量 而损坏。此外,因为 Q1 必须确保一定的导通时间,所以设定 满足两个条件的时间。 SiC MOSFET 产生的损失有开关损失和导通损失。理想的开关波形中,如 VDS(Q1)和 ID(Q1)不会延迟,电压和电流会垂直变化。这种状态下 不会产生多余的电压和电流,所以不会发生损失。实际上由于 寄生电阻和寄生容量的影响会产生延迟,电压和电流波形会像以 ton、toff 的倾斜变化。这个倾斜部分的电压和 电流重叠的部分是开关损失。在实际电路中,导通和关断时的过渡期电压和电流会呈指数变 化,但是观测到的波形很难用指数函数表示,所以用直线近似 来计算。计算每个区间用 Q1 消耗的电力量。首 先,在导通 ton 及关断 toff 时间(开关时间)中消耗的电力量 WSW 可以近似于式(1)。 接着计算导通时消耗的功率。因为 Figure 6 在 TON 的区间 Q1 导通,所以 VDS 成为 Q1 的导通电阻和 ID 的积。导通电阻的值 参照数据表。功率 WON可通过式(2)近似。 其中,Ron(Q1):Q1 的导通电阻[Ω] TON:Q1 的开启时间[s] 接下来是 Q1 关断时的功率。Figure 6 是 TOFF 的区间,Q1 OFF 时 ID变为零,功率 WOFF变为零(式 3) Q1 的全部功率可以通过式(4)求出,成为式(1)到(3)的 总和。 另外,Q1 的功率损失可以用公式(5)计算。 其中,T:切换周期[s] f:开关频率[Hz] 如上所述,损失是通过对电压和电流重叠的部分进行积分近似来计算的。 -End- 我是54攻城狮 感谢你的阅读, 欢迎一键三连,点赞·在看·评论,您的支持是我日更最大的动力! 关注这个公众号,日拱一卒功不唐捐,一起成长。 推荐阅读 几种不同IGBT结温测试方法小结 IGBT驱动电路的设计 |

【本文地址】