| 浮点数加法器设计 | 您所在的位置:网站首页 › 8位浮点数 › 浮点数加法器设计 |

浮点数加法器设计

|

一.设计内容及其要求

内容

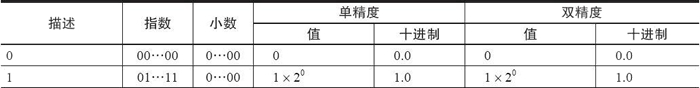

根据浮点数的运算规则和IEEE754标准,实现浮点数的加法运算器。 要求: 浮点数格式:符号位1位,阶码8位,尾数23位要求该实验能完整的体现浮点数的运算的五个步骤:对阶、尾数求和、规格化、舍入(要求使用对偶舍入)、溢出判断。 二.基本要素 浮点数浮点数即实数,实数是所有有理数和无理数的集合。它之所以被称作浮点数,是因为小数点在数中的位置并不是固定的。一个浮点数值分为两部分存储:数值以及小数点在数值中的位置。 计算机中的浮点运算的计算结果一般是不确定的,一块芯片的浮点运算结果可能和另一块芯片的运算结果是不一样的。 科学计数法科学计数法用来表示很大或很小的数。 十进制浮点数可以表示为: 尾 数 × 1 0 指 数 , 如 1.23456 × 1 0 20 尾数×10^{指数},如1.23456×10^{20} 尾数×10指数,如1.23456×1020 二进制浮点数可以表示为: 尾 数 × 2 指 数 , 如 1.00011 × 2 5 尾数×2{指数},如1.00011×2^{5} 尾数×2指数,如1.00011×25 IEEE 754浮点数标准提供3中浮点数表示:32位单精度浮点数、64位双精度浮点数、128位四精度浮点数。这里设计浮点加法器主要用32位单精度浮点数,想要实现64位或者128位浮点数的加法,它们的原理和32位单精度浮点数的加法器是类似的。 规格化浮点数IEEE 754浮点数的尾数总是规格化的,其范围为 1.000...0 × 2 e − 1.111...1 × 2 e 1.000...0×2^e - 1.111...1×2^e 1.000...0×2e−1.111...1×2e,e为指数。 规格化浮点数的最高位总是1,规格化使尾数的所有位都是有效的,因而尾数精度更高。 如: 0.10... × 2 e 规 格 化 为 1.10... × 2 e − 1 10.1... 2 e 规 格 化 为 1.01... × 2 e + 1 0.10...×2^e规格化为1.10...×2^{e-1}\\10.1...2^e规格化为1.01...×2^{e+1} 0.10...×2e规格化为1.10...×2e−110.1...2e规格化为1.01...×2e+1 尾数规格化充分利用了可用的最大精度。如,一个8位非规格话的尾数0.0000101只有4位有效位,而规格化后的8位尾数1.0100011则有8位有效位。 偏置指数IEEE 754浮点数的尾数被表示为符号及值的形式,即用一个符号位表示它是正数还是负数。它的指数则用偏置方式表示,即给真正的指数加上一个常数。 已知32位单精度浮点数的指数部分是8位,则偏置值为127。如果一个数的指数为0,则被保存为 0 + 127 = 127 0+127=127 0+127=127。如果指数为-2,则被保存为 − 2 + 127 = 125 -2+127=125 −2+127=125。 实数1010.1111规格化的结果为 1.010111 × 2 3 1.010111×2^3 1.010111×23,指数为3,将被保存为 3 + 127 = 130 3+127=130 3+127=130。 这种用偏置表示指数的方法优点在于:最小的负指数被表示为0,如果不采用这种方法,0的浮点表示为

0.0...0

×

2

最

小

负

指

数

0.0...0×2^{最小负指数}

0.0...0×2最小负指数 。采用偏置指数。0就可以用尾数0和指数0表示: 一个32位IEEE 754单精度浮点数可以被表示为下面的二进制串: S EEEEEEEE 1.MMMMMMMMMMMMMMMMMMMMMMM S为符号位,指明这个数是正数还是负数E为8位偏置指数,指出了小数点的位置M为23位尾数

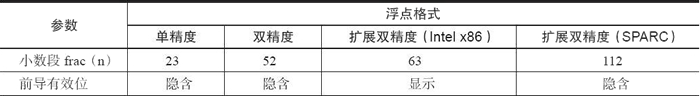

S作为符号位,决定了数的符号,若S=0,则为正数,若S=1,则为负数。指数E将浮点数的尾数扩大或缩小 2 E 2^E 2E 倍,并且偏置值为127。 如浮点数 1.11001...0 × 2 12 1.11001...0×2^{12} 1.11001...0×212的指数为 12 + 127 = 13 9 10 = 1000101 1 2 12+127=139_{10}=10001011_2 12+127=13910=100010112 IEEE浮点数的尾数总是规格化的,其值范围在 1.0000..00 − 1.1111..11 1.0000..00-1.1111..11 1.0000..00−1.1111..11 ,除非这个浮点数是0,此时尾数为 0.000..00 0.000..00 0.000..00。 由于尾数总是规格化的,且最高位总是为1,因此将尾数存入存储器时没有必要保存最高位的1。所以,一个非0的IEEE 754浮点数可被定义为: X = ( − 1 ) S × 2 E − B × 1. F X=(-1)^S×2^{E-B}×1.F X=(−1)S×2E−B×1.F ,其中: S符号位E:偏置量为B的指数F:尾数的小数部分(实际的尾数为1.F,有个隐含的1)ps:浮点数0被表示为S=0,E=0,M=0(即浮点数0用全0表示) 格式IEEE 754标准定义了基本的和扩展的浮点数格式,以及一组数量有限的算术运算的规则(加、减、乘、除、平方根、求余和比较)。 非数(Not a Number,NaN)是IEEE 754标准提供的一个专门的符号,表示IEEE 754标准格式所不能表示的数。

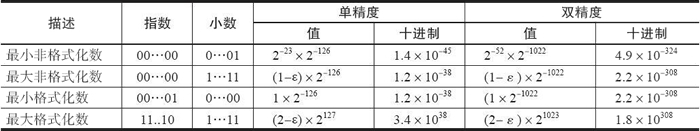

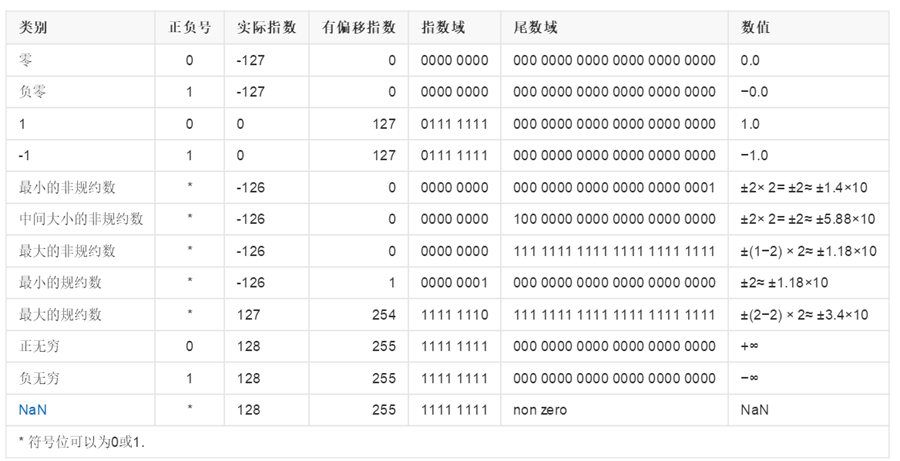

在32位IEEE 754单精度浮点数格式中,最大指数 E m a x E_{max} Emax为127,最小指数 E m i n E_{min} Emin为-126,而不是 − 127 至 128 -127至128 −127至128。 E m i n − 1 ( 即 − 127 ) E_{min-1}(即-127) Emin−1(即−127)用来表示浮点0, E m a x + 1 ( 即 128 ) E_{max}+1(即128) Emax+1(即128)用来表示正/负无穷大或NaN数。 下图,描述了IEEE单精度浮点数格式,指数E=0和E=255等特例分别被用于表示浮点0,非规格化效数、正/负无穷大、以及NaN:

(1)浮点数接近0时的特点,下图描述了一个指数2位,尾数为2位的浮点数系统。浮点数0表示00 000,下一个规格化的正数表示为00 100(即

2

−

b

×

1.00

2^{-b}×1.00

2−b×1.00,b为偏置常数): 浮点数0附近有一块禁止区,其中的浮点数都是非规格化的,因此无法被表示为IEEE标准格式。这个数的指数和起始位都是0的区域,也可用来表示浮点数。但是这些数都是非规格化的,其精度比规格化的精度低,会导致渐进式下溢。 (2)IEEE标准规定,缺省的舍入技术应该向最近的值舍入。 (3)IEEE标准规定了4种比较结果,分别是等于、小于、大于和无序,无序用于一个操作数是NaN数的情景。 (4)IEEE标准规定了5种异常: 操作数不合法:使用了一些不合法的操作数:NaN数、无穷大数、求负数的平方根(这里不必考虑)。除数为0(这里是加法器,所以不需要考虑)上溢:当结果比最大浮点数还大时,处理上溢的方法有终止计算和饱和运算(用最大值作为结果)等下溢:当结果比最小浮点数还小时,处理下溢的方法有将最小浮点数设为0或用一个小于 2 E m i n 2^{E_{min}} 2Emin的非规格化数表示最小浮点数等方式处理。结果不准确:当某个操作产生舍入错误时。 运算浮点数不能直接运算。 以一个简单的8位尾数和一个未对齐的指数为例说明浮点运算, A = 1.0101001 × 2 4 A=1.0101001×2^4 A=1.0101001×24, B = 1.1001100 × 2 3 B=1.1001100×2^3 B=1.1001100×23。若要计算两个数的成绩,应将尾数相乘,指数相加: A ⋅ B = 1.010100 × 2 4 × 1.1001100 × 2 3 = 1.0101001 × 1.1001100 × 2 3 + 4 = 1.000011010101100 × 2 8 A·B=1.010100×2^4× 1.1001100×2^3\\~~~~~~~~~=1.0101001×1.1001100×2^{3+4}\\~~~~~~~~~=1.000011010101100×2^8 A⋅B=1.010100×24×1.1001100×23 =1.0101001×1.1001100×23+4 =1.000011010101100×28 由于IEEE标准下的浮点操作数已被表示为规格化形式,计算机在进行浮点加法时,为了对齐指数,计算机必须执行下面步骤: 第一步,找出指数较小的数第二部,使两个数的指数相同第三步,尾数相加第四步,如果有必要,将结果规格化所以得到A+B的运算

注意: (1)因为IEEE754标准的32位单精度浮点数的指数与尾数位于位于同一个字中,所以在加法过程开始之前必须将它们分离开。 (2)如果两个指数的差大于p+1,p为尾数的位数,这里p=23,较小的数由于太小而无法影响较大的数,结果实际就等于较大的数。 (3)结果规格化时检查指数范围,以分别检测指数下溢或上溢。指数下溢会导致结果为0,而指数上溢出会造成错误。 浮点加法运算的流程图

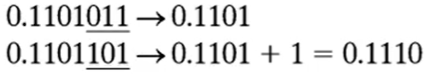

浮点运算可能引起尾数位数的相加,需要保持尾数位数不变的方法。最简单的技术叫作截断。 比如将0.1101101截断为4位尾数的结果为0.1101。截断会产生诱导误差(即误差是由施加在数上的操作计算所引起的),诱导误差是偏差的,因为截断后的数总比截断钱小。 舍入是一种更好的减少数的尾数的技术。如果舍弃的位的值大于剩余数的最低位的一半,将剩余数的最低位+1。 比如: (1)最简单的舍入机制是截断或向0舍入。 (2)向最近的数舍入:选择距离该数最近的那个浮点数作为结果。 (3)向正或负无穷大舍入:选择正或负无穷大方向上最近的有效浮点数作为结果。 (4)向偶数舍入:当要舍入的数位于两个连续浮点数的正中时,IEEE舍入机制选择最低位为0的点(即向偶数舍入)

舍入机制将在后面基本原理与设计部分重点解释。 三.基本原理与设计定义接口部分:时钟信号clk,复位信号rst,输入[31:0]宽的加数x和被加数y,输出[31:0]宽的结果z,[1:0]宽的溢出标志overflow。 其中overflow=2’b00:没有溢出; overflow=2’b01:上溢; overflow=2’b10:下溢; overflow=2’b11:输入不是规格化数 定义[24:0]宽的尾数部分m_x,m_y,m_z:IEEE 754标志的32位单精度浮点数的尾数本身是23位宽的,但是再尾数相加的时候要考虑到隐含的1,并且还需要考虑进位,所以设定为25位宽的数组来存储的尾数。 定义[7:0]宽的指数部分exponent_x,exponent_y,exponent_z。 定义符号部分sign_z,sign_x,sign_y。 这里实现的是多周期的单精度浮点加法器,所以考虑到需要状态机,所以设定[2:0]宽的state_now,state_next分别表示当前状态和下一个状态,并且设定start = 3’b000(start是初始化阶段),zerocheck = 3’b001(zerocheck是检查x=0或y=0阶段),equalcheck = 3’b010(equalcheck对阶阶段),addm = 3’b011(addm是尾数相加阶段),normal = 3’b100(normal是规格化尾数阶段),over = 3’b110(over是判断溢出阶段,此阶段同时输出结果部分); 由于需要进行对偶数舍入所以这里设定[24:0]宽的尾数移出部分out_x,out_y来存储x与y右移出尾数的部分(相对顺序不变),设定[24:0]宽的最低位的一半的部分mid_x,mid_y来存储x与y尾数的最低有效位的一半,设定[2:0]宽的大小标志bigger(如果exponent_x>exponent_y,则bigger=2’b01;如果exponent_xexponent_y)begin ...//y的尾数右移动阶段,并且记录移出的部分 if(m_y==24'b0)begin//如果x和y的节码差距过大,就不需要考虑太小的 sign_z |

【本文地址】