| 74LS161计数器+cd4046锁相环 | 您所在的位置:网站首页 › 74ls161实现16进制 › 74LS161计数器+cd4046锁相环 |

74LS161计数器+cd4046锁相环

|

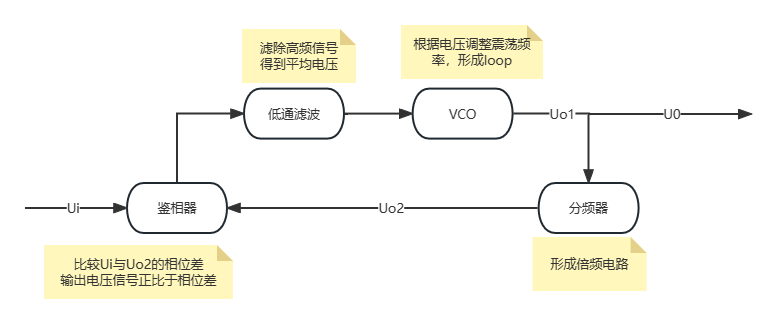

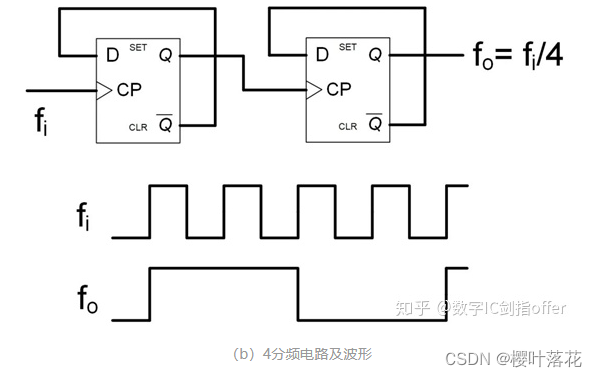

目录 前言 一、整体电路结构介绍 二、74LS161介绍 三、分频电路实现 3.1相关知识 3.2 74ls161仿真实现 3.2.1 4位二进制计数基本功能演示 3.2.2 预置数实现分频 3.2.3 清零实现分频 3.2.3 级联实现50%占空比分频 3.2.4 分频总结 四、cd4046介绍 五、锁相环实现 前言本篇文章主要是记录使用cd4046锁相环与74ls161构成倍频电路。 一、整体电路结构介绍众所周知,锁相环(PLL)的实现一般包括压控振荡器(VCO)、分频器、鉴相器、低通滤波器和压控震荡器构成的环路而成。结构如下:

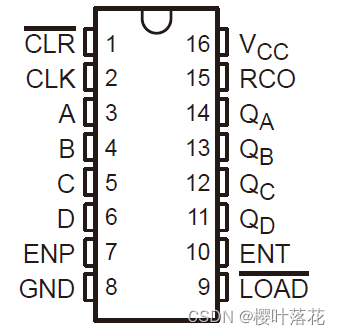

其中分频器分频倍数决定了锁相环最终产生的信号频率,即N倍频需要分频器进行N分频。 接下来我们逐步实现倍频。 二、74LS161介绍首先进行分频电路的实现,我们选择74ls161。 了解芯片先从datasheet开始!进入芯片官网下载datasheet,对于74ls161,可以进入TI官网搜索,这里放上文档直链。  TOP VIEW

TOP VIEW

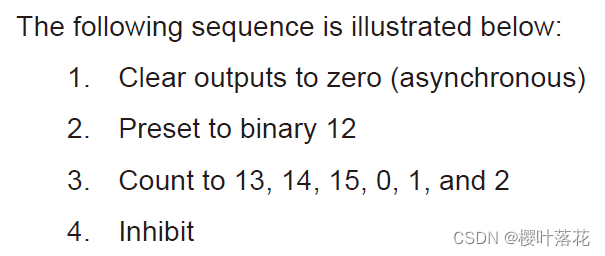

我们先认识一下这款芯片,从datasheet可以知道,这是一款4位同步二进制计数器,更多的细节可以在datasheet里找到。 简要介绍一下引脚信息: 引脚名功能#CLR异步置零,不管clk或者其他控制引脚处于什么状态,低电平时直接拉低所有输出。CLK时钟信号,计数基准A~D预置数输入Qa~Qd 计数输出ENP同步计数使能,高电平时允许计数ENT同步计数使能,高电平时允许计数,使能RCOVCC GND 电源#LOAD同步预置数,下一个clk上升沿时读取A~B赋给Qa~Qd,不管使能引脚状态RCO进位脉冲,计数到15时,Qa~Qd和RCO同为高电平,下一个上升沿时全恢复为低电平。用于级联。数据手册提供了一个设计参考,可以更清晰地认识芯片工作流程:

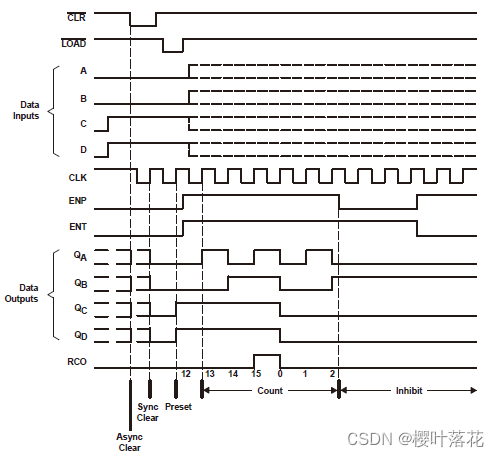

在这之前我们复习一下怎么实现分频器。这里可以参考原作者的详细介绍:分频电路 ①D触发器,即一个D触发器实现2^1分频,两个级联实现2^2分频······ 原理很简单,参见下图:

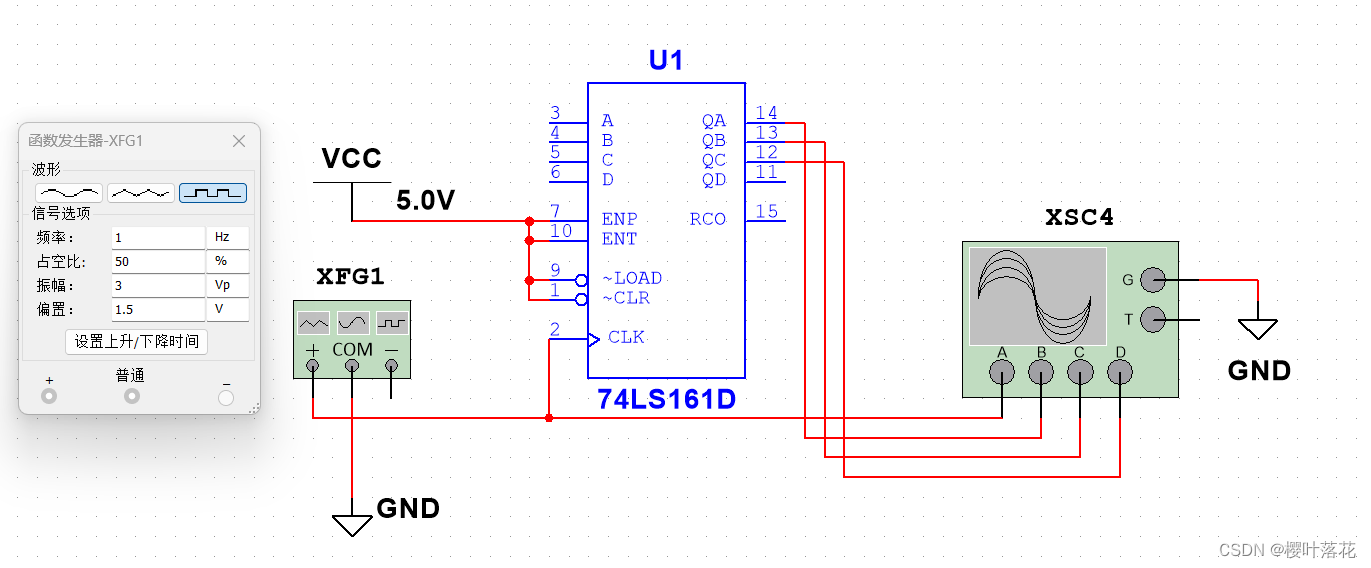

②今天的主角——计数器实现N分频 (详细内容参考原作者) 偶数倍分频,占空比D=0.5上升沿计数 N/2-1清零 到N/2-1时翻转 奇数倍分频,占空比D!=0.5上升沿计数 N-1清零 (N-1)/2或者0时翻转 奇数倍分频,占空比D=0.5上升沿计数 N-1清零 (N-1)/2或者0时翻转,信号P 下降沿计数 N-1清零 (N-1)/2或者0时翻转,信号N P|N 接下来我们根据以上内容使用74ls161实现,借助NI Multisim平台仿真演示。 3.2 74ls161仿真实现 3.2.1 4位二进制计数基本功能演示方便演示,选用1Hz方波信号,控制信号全部拉高,接入clk和低三位信号观察。  仿真电路连接

仿真电路连接

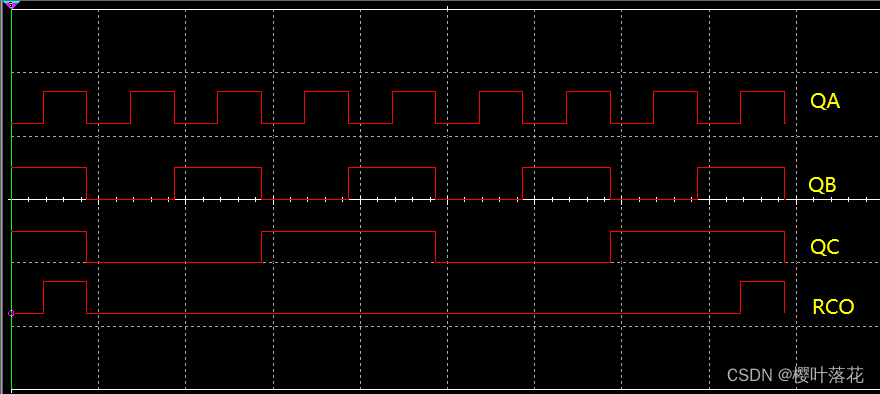

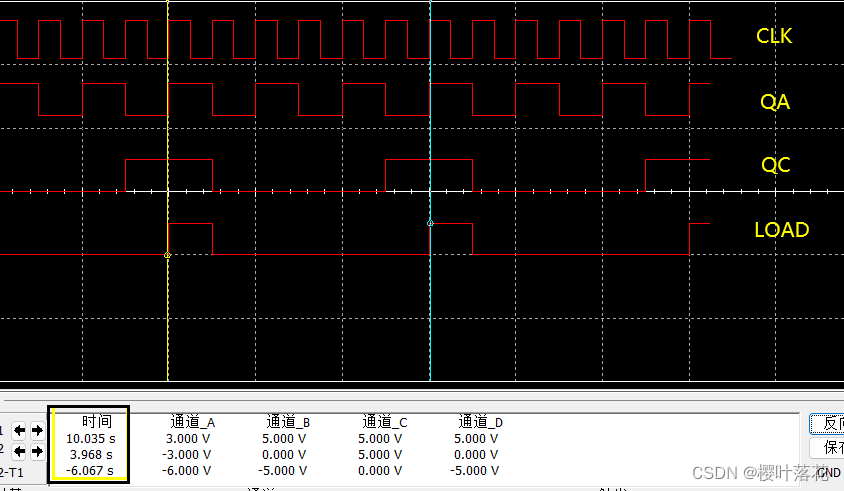

示波器结果

示波器结果

这里我们可以明显察觉到,计数器的四位即可视为4个级联的D触发器,那么可以直接得到2^n分频,这是一种最简单的方法: QA~QD即D触发器的级联,QA~QD即为clk的2、4、8、16倍分频,且D=0.5 接下来我们观察RCO信号,这会给我们什么启示呢?

确实,RCO与QA~QD一同到高电平,下一个上升沿时全部降到低电平,而这个RCO脉冲接入非门后即可成为#LOAD信号,采用初始置数实现分频。这样一计满即可读取置数,根据想达到的分频数设置预置数。 3.2.2 预置数实现分频我们先置数1110,即A为0,BCD为1。将RCO输出经过非门后进入#LOAD,其他控制信号拉高使能。

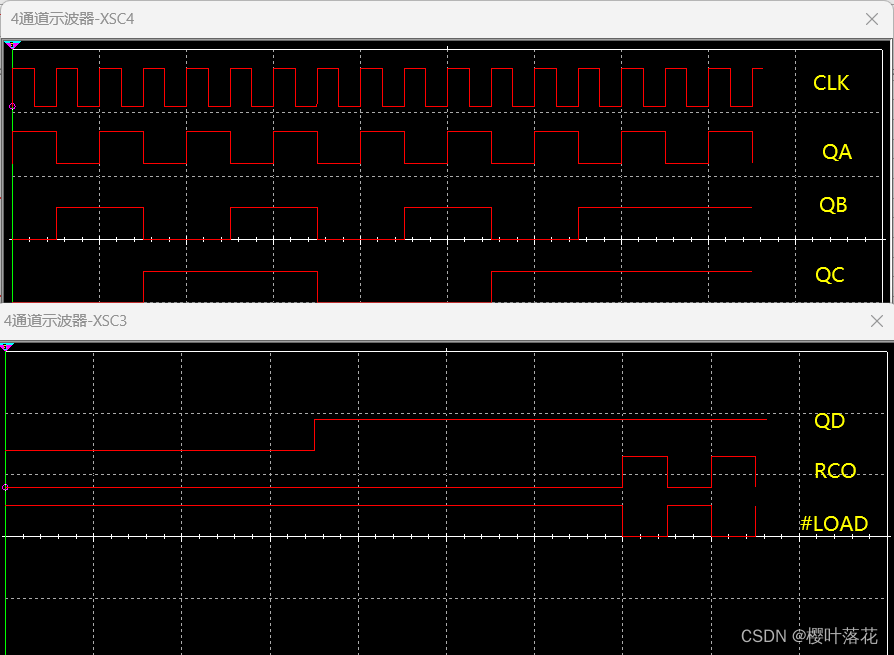

我们可以看到,由于一开始#LOAD为高电平,在第一个周期时需要计满才能进入计数环节。

在进入计数环节后,会发现由于初始置数(1110)的原因只需要一个上升沿就会让RCO溢出,实现RCO作为输出信号,即2分频。 很显然,当我们把初始置数调节后,即可实现2~17分频。但占空比不会是50%。 例如,我们将初始置数设置为(1100),再次观察示波器的RCO信号,观察信号容易知道实现了非50%占空比的四分频:

通过预置数,将RCO取反后接入#LOAD信号,即可在一个周期后实现非50%占空比奇偶倍分频。 3.2.3 清零实现分频回顾之前提到的计数器分频相关知识,当我们想靠清零实现分频时,需要确定分频数、清零时间与翻转时间。 对于偶数占空比50%分频,在上升沿计数 N/2-1清零 到N/2-1时翻转,也就是说要实现6分频,在2(xx10)时清零,2时翻转,我们先搭建这个电路: 简单逻辑门的组合让出现(xx10)时才能给#CLR一个低信号。

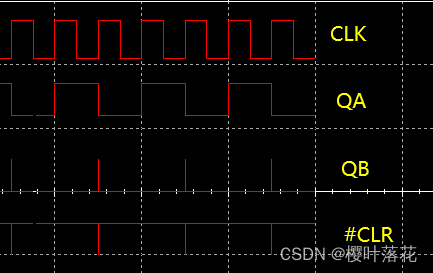

我们发现和我们想的不一样,当QB一达到高电平,与门马上输出逻辑1,非门随之给出0进入#CLR引脚,异步置零导致了出现了一个很短时间的脉冲,不会等待下一个上升沿的到来,这不是我们想得到的。 那,我们采取置数(0000)得到同步置零,放弃这个异步置零控制。将ABCD接低,逻辑信号给到#load,再次观察:

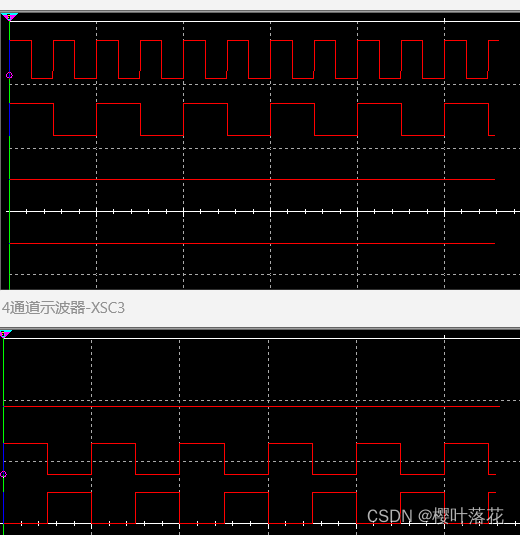

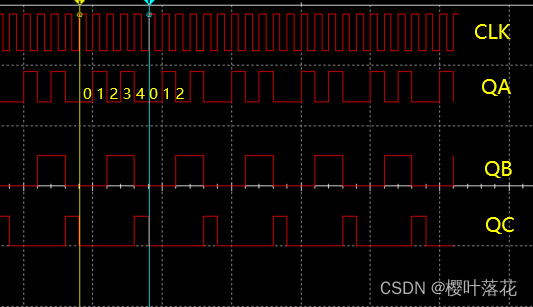

已经看到,实现了计数0、1、2、0、1、2······ 接下来实现在2时翻转,其实,再看刚才那个电路,刚才那个逻辑电路产生的信号,在2时变低,其他时候为高,也就是在2或者0时翻转,这不是我们想要的六分频,0时翻转带来的恰好是分频数折半——3分频。 这也和刚才提到的奇数分频:上升沿计数 N-1清零 (N-1)/2或者0时翻转,效果类似,只是翻转时间点变为了N-1或者0翻转。总之: 实现非50%占空比的奇数倍分频,即上升沿计数 N-1清零 在一个周期里翻转两次即可 我们回到刚才的目的, 刚才3分频在2清零,实现6分频, 我们便可以将清零数设置为5(x101),可以看出信号得到了6分频:

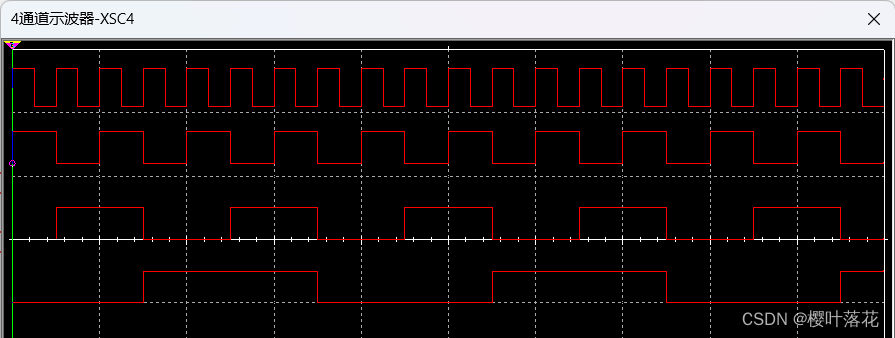

搞了这么多,占空比都不是最理想的0.5,我们回到刚才提过的实现方法,就是利用clk的“延时半个周期”带来翻转的错位,最后利用取或操作得到50%占空比:

说干就干,用两个计数器AB实现,由于74ls161是上升沿触发,那么A计数器使用CLK触发,B计数器使用#CLK触发,即可。 我们以5倍频为例,即4(x100)清零,两路信号取或。但是我们注意到,如果仍然在N-1或0翻转时虽然能得到5倍频,但是取反操作不是在相对中间,而是相近(类似于QC),不会得到50%占空比。我们当然可以根据(N-1)/2或者0翻转,无疑是增加了更多的逻辑期间;但仔细观察(x100)中的QB,一个周期翻转两次,占空比恰好和(N-1)/2或者0一样,于是我们得到以下电路:

观察取或信号,即可得到5倍频50%占空比信号。

上升沿触发器A在N-1置零,下降沿触发器在N-1置零,将有效Q信号取或,得到50%占空比信号。这对奇偶数分频都有效。 3.2.4 分频总结其实,3.2.2提到的预置数分频,是控制计数器在x~15之间,而3.2.3提到的置零计数,是控制计数器在0~x之间计数——都是在一个周期内翻转两次得到分频信号。 3.2.3提到的级联置数,是利用clk的上升下降沿的不同,带来的半个时钟周期“延时”,最后取或得到50%占空比的分频信号。 当然,也可以使用单个计数器得到偶数50%占空比分频,这里不再赘述。 四、cd4046介绍接下来我们介绍一下通用的CMOS锁相环集成元件cd4046,这里放上TI的官方数据手册:cd4046_datasheet, 2003年的,年龄比较大嘿嘿~  来自2003年的TOP VIEW

来自2003年的TOP VIEW

来自2003年的block diagram

来自2003年的block diagram

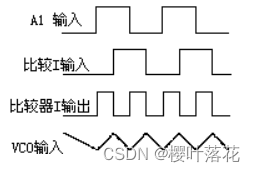

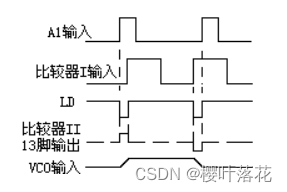

详情请参考数据手册,这里只简要介绍部分引脚作用: 引脚名作用Phase Pulses环路入锁时为高电平,环路失锁时为低电平Phase Comp I OUT相位比较器I的输出端Phase Comp II OUT相位比较器II的输出端Conparation In比较器输入端,一般接输出信号Signal In比较器输入端,一般接外部输入信号VCO OUTVCO产生信号的输出端,一般直接或分频后接入接入Conparation In,INHIBIT低电平禁止VCO工作C1 C2外接震荡电容VDD VSS电源输入 ZENER内部齐纳二极管R1 to VSS R2 to VSS 外接震荡电阻Demodulated OutFM解调VCO INVCO控制电压信号我们再仔细观察这个框图,会发现cd4046内部提供了一个VCO,两个相位比较器,一个源跟随器,以及其他必要元件。这里主要参考原作者:锁相环CD4046应用介绍 - 搜档网 对于相位比较器,可以看到信号输入均经过了运放,可以将微弱输入信号变成方波或脉冲信号送至两相位比较器。而两者的差异是比较逻辑不同—— 相位比较器I:异或门。当信号电平不同时,异或门输出高电平,反之输出高电平,经过低通滤波器后VCO输入波形类似下左图。而这也提示我们相位比较器I的输入信号需要均为50%占空比方波信号方可实现最大跟踪范围。 相位比较器II:上升沿控制的数字存储网络。它对输入信号占空比的要求不高,允许输入非对称波形,它具有很宽的捕捉频率范围,而且不会锁定在输入信号的谐波。当达到锁定时,在相位比较器Ⅱ的两个输人信号之间保持0°相移。 当输入信号较比较信号频率低时,输出为逻辑“0”;反之则输出逻辑“1”。如果两信号的频率相同而相位不同,当输人信号的相位滞后于比较信号时,相位比较器Ⅱ输出的为正脉冲,当相位超前时则输出为负脉冲。在这两种情况下,从1脚都有与上述正、负脉冲宽度相同的负脉冲产生。从相位比较器Ⅱ输出的正、负脉冲的宽度均等于两个输入脉冲上升沿之间的相位差。而当两个输入脉冲的频率和相位均相同时,相位比较器Ⅱ的输出为高阻态,则1脚输出高电平。 相位比较器I逻辑图

相位比较器I逻辑图

相位比较器II逻辑图

相位比较器II逻辑图

对于其他主要有: CD4046锁相环采用的是RC型压控振荡器,必须外接电容C1和电阻R1作为充放电元件。当PLL对跟踪的输入信号的频率宽度有要求时还需要外接电阻R2。由于VCO是一个电流控制振荡器,对定时电容C1的充电电流与从9脚输入的控制电压成正比,使VCO的振荡频率亦正比于该控制电压。VCO振荡频率的范围由R1、R2和C1决定。由于它的充电和放电都由同一个电容C1完成,故它的输出波形是对称方波。其他请阅读数据手册~

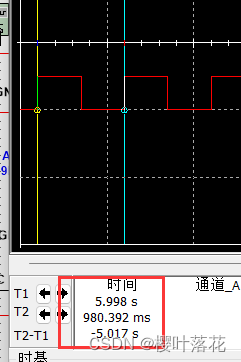

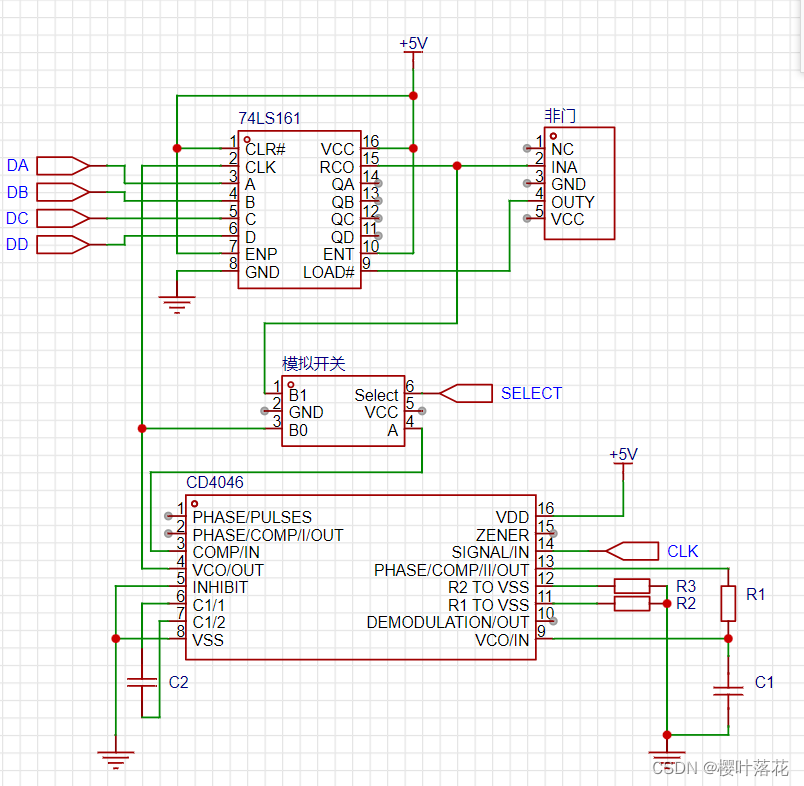

五、锁相环实现 想要实现单个电路按需倍频,那么需要引入模拟开关控制信号的连接,这里我们选用二选一模拟开关控制电气连通。 若要实现1~5倍频,cd4046的相位比较器I需要50%占空比信号输入,这无疑增加我们设计复杂度,故采用单片计数器利用清零实现非50%占空比分频。整体结构如下:

电气连接如下:

通过单片机预置DA~DD四位数,以及控制SELECT信号选择1倍频或者多倍频,根据实际频率选择参数并完善电气连接即可。 如有错误,欢迎指正! 参考链接: 常用电路设计——“分频电路” - 知乎 锁相环CD4046应用介绍 - 搜档网 |

【本文地址】