| 数字逻辑基础实验二 | 您所在的位置:网站首页 › 74ls138译码器逻辑功能验证 › 数字逻辑基础实验二 |

数字逻辑基础实验二

|

实验目的

(1)掌握中规模集成寄存器构成的时序逻辑电路的设计方法。 (2)掌握中规模集成计数器设计N进制计数器的方法。 (3)学会用时序功能器件构成综合型应用电路。 实验电路

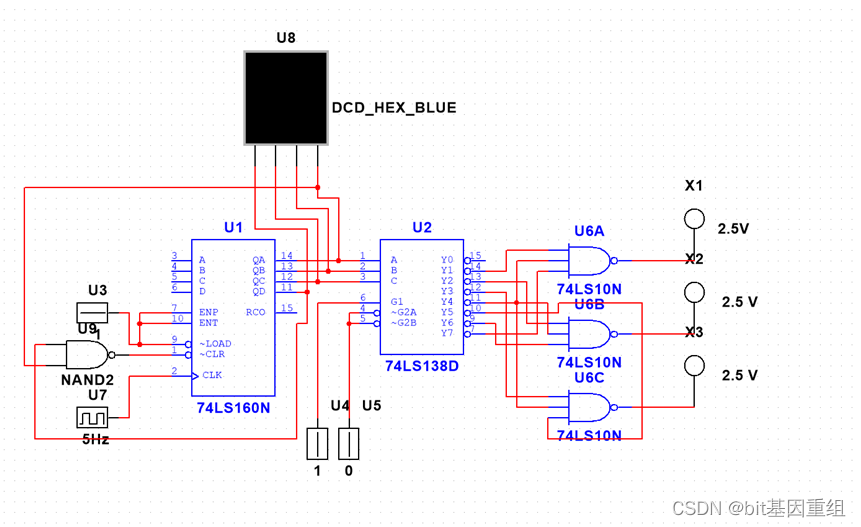

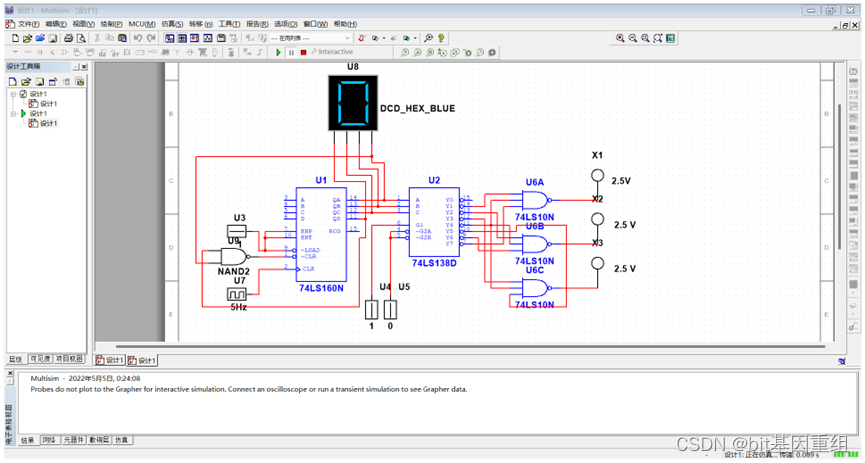

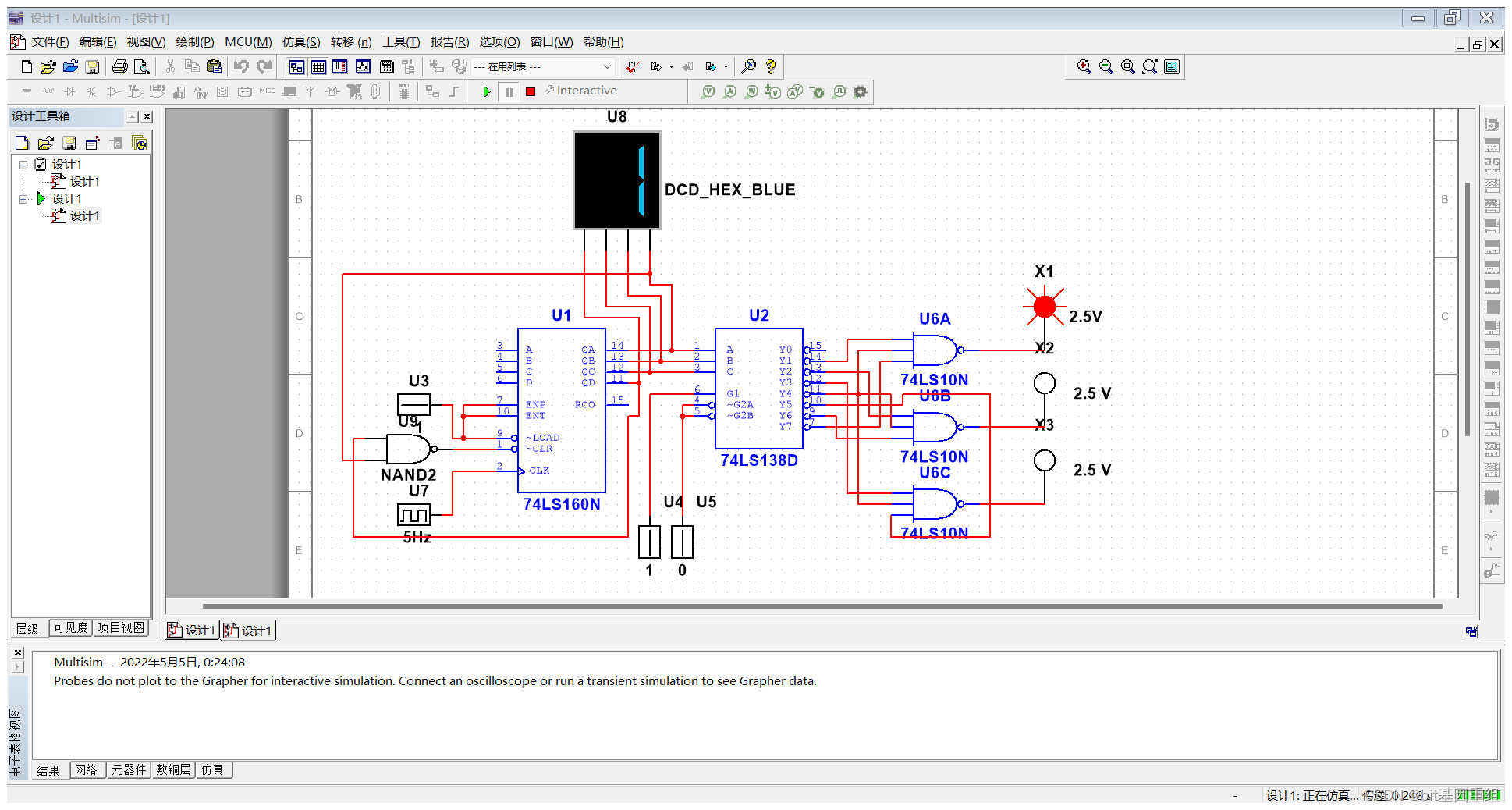

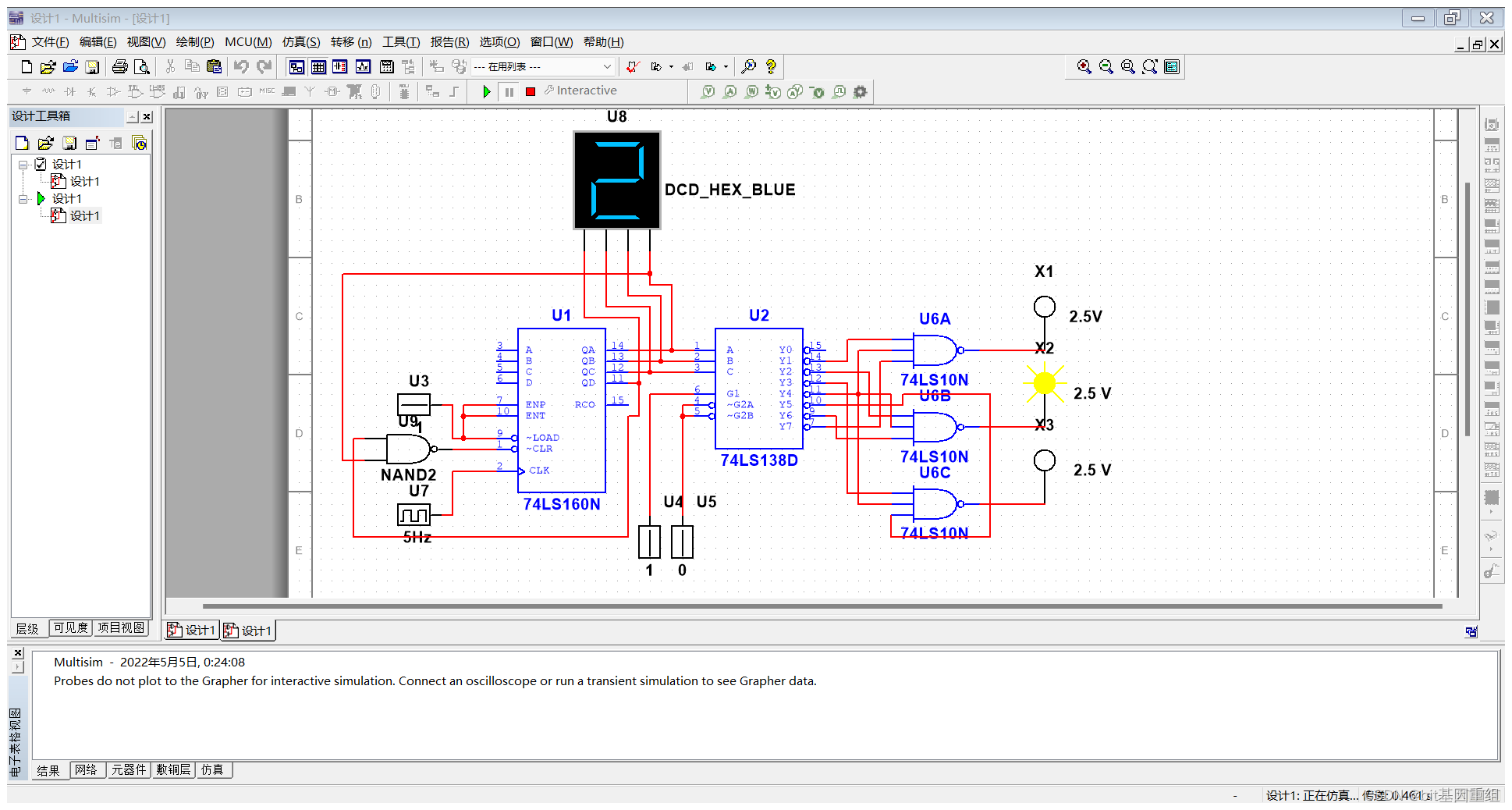

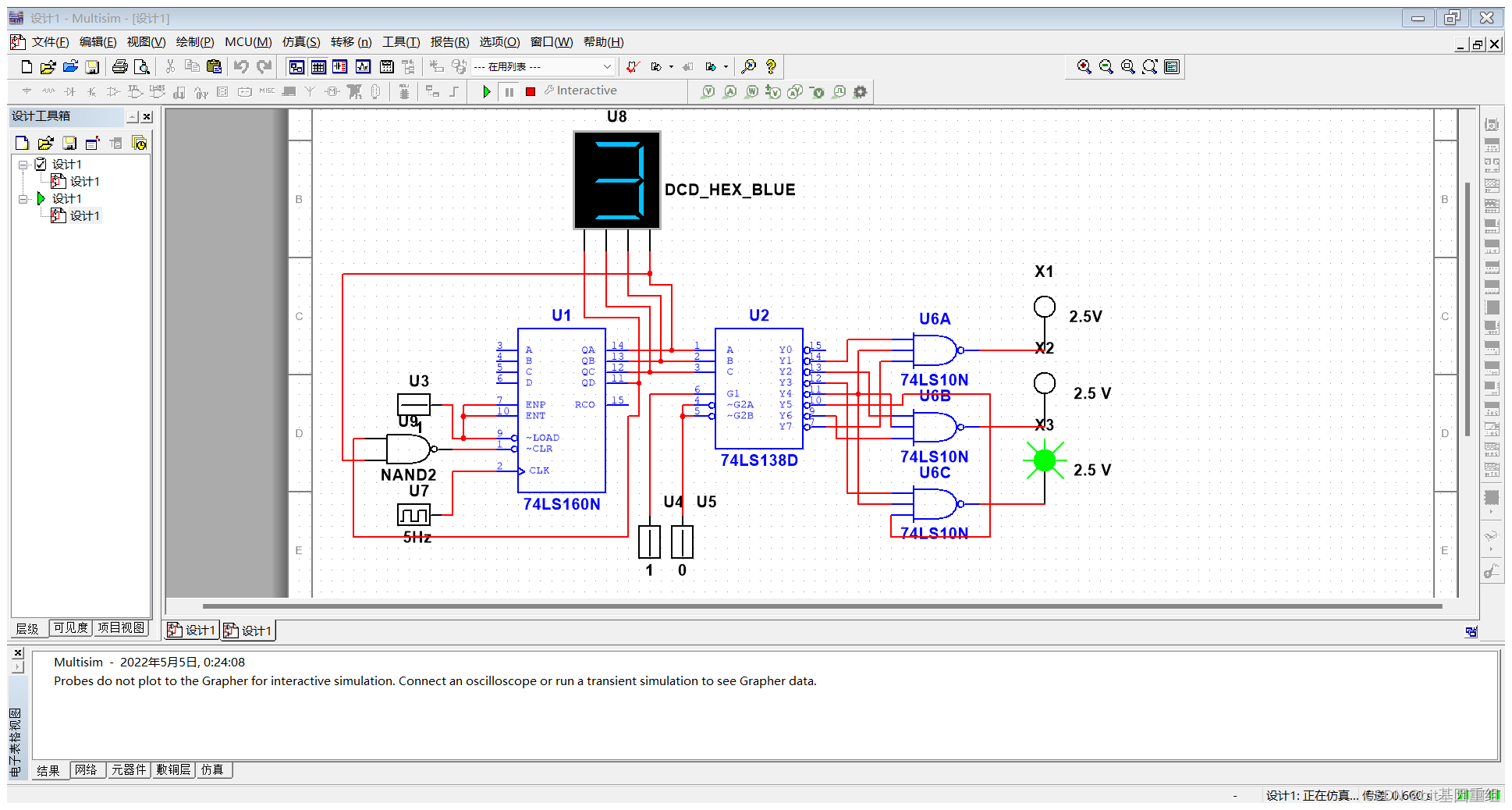

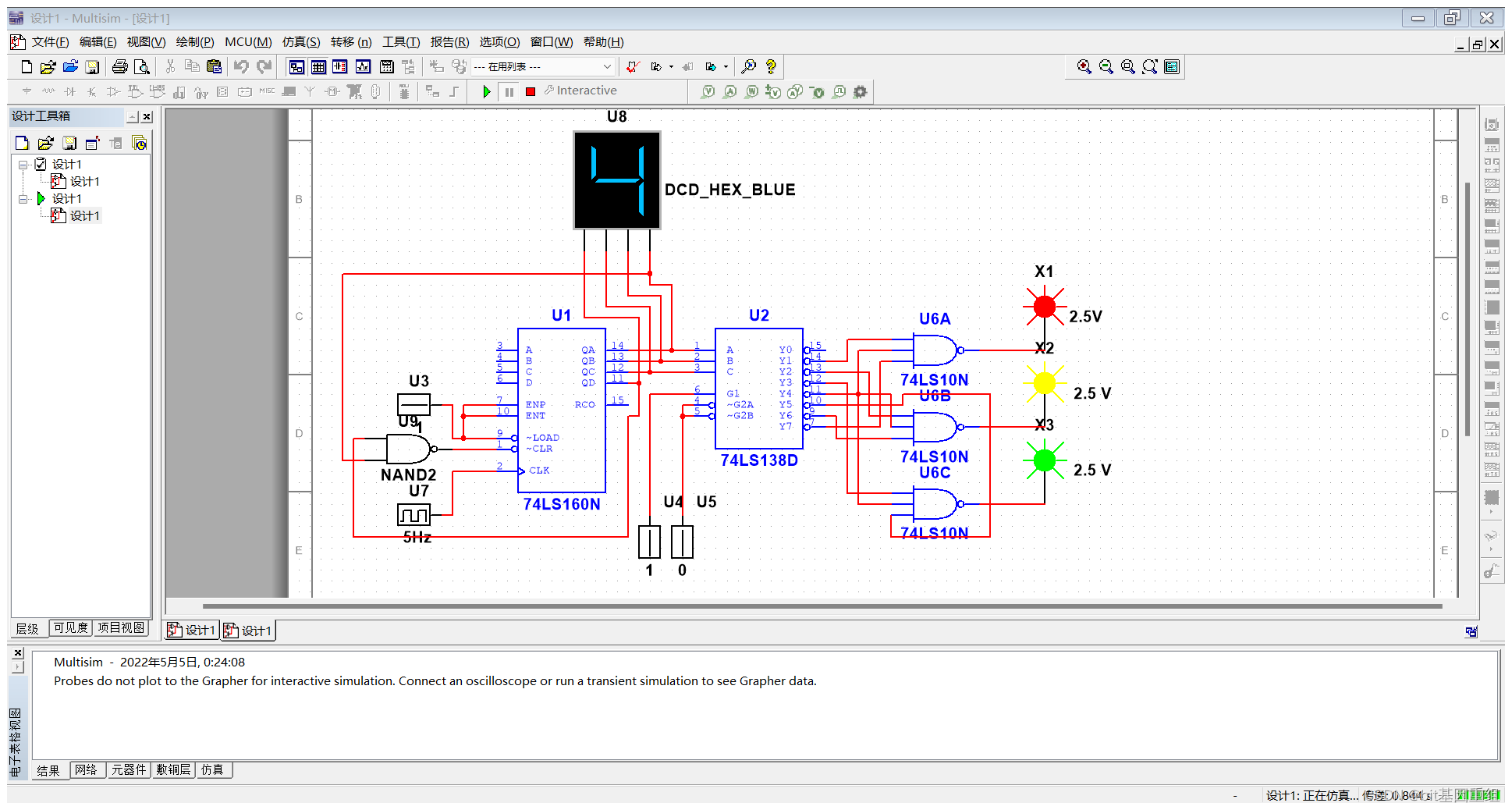

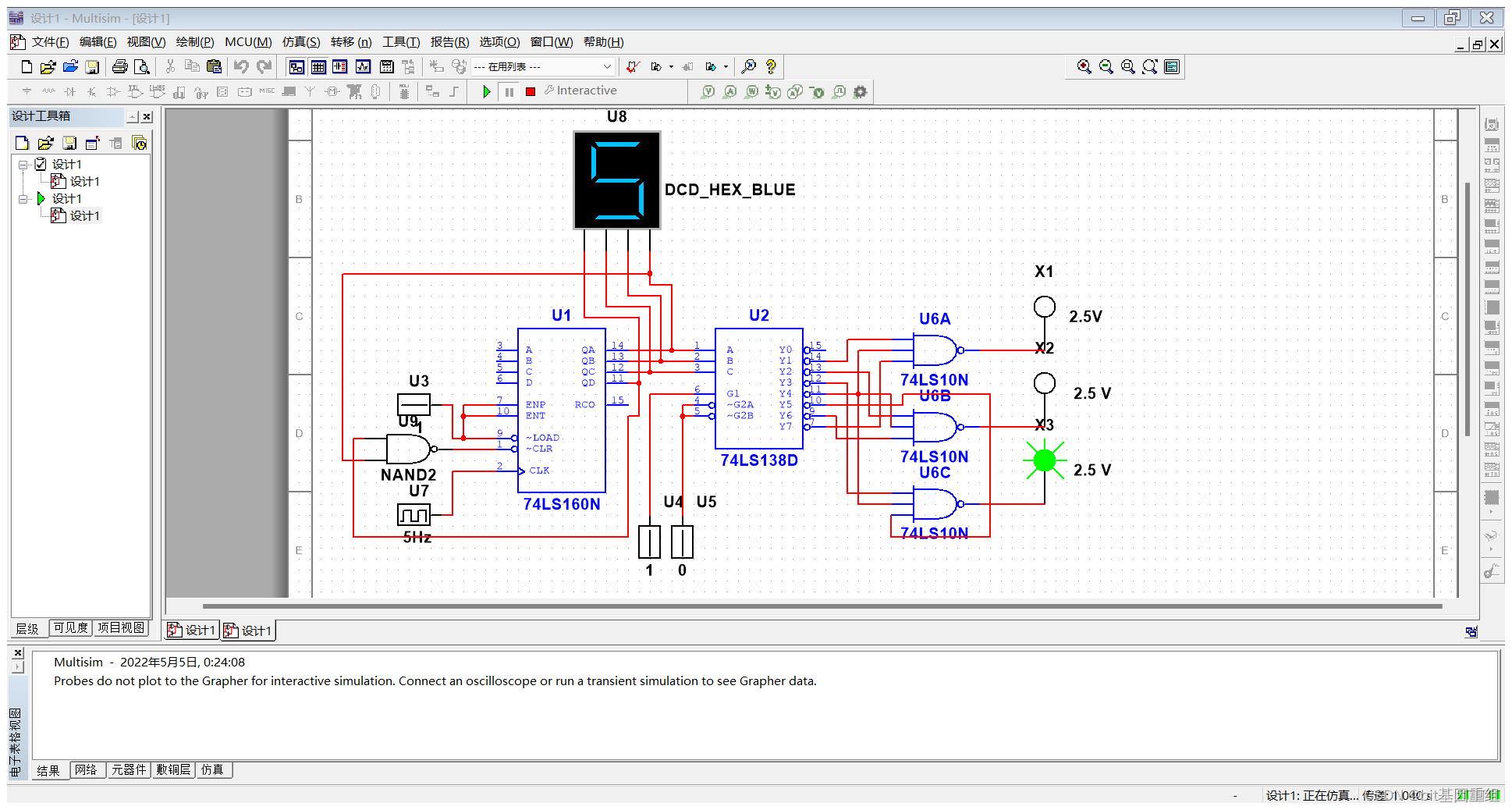

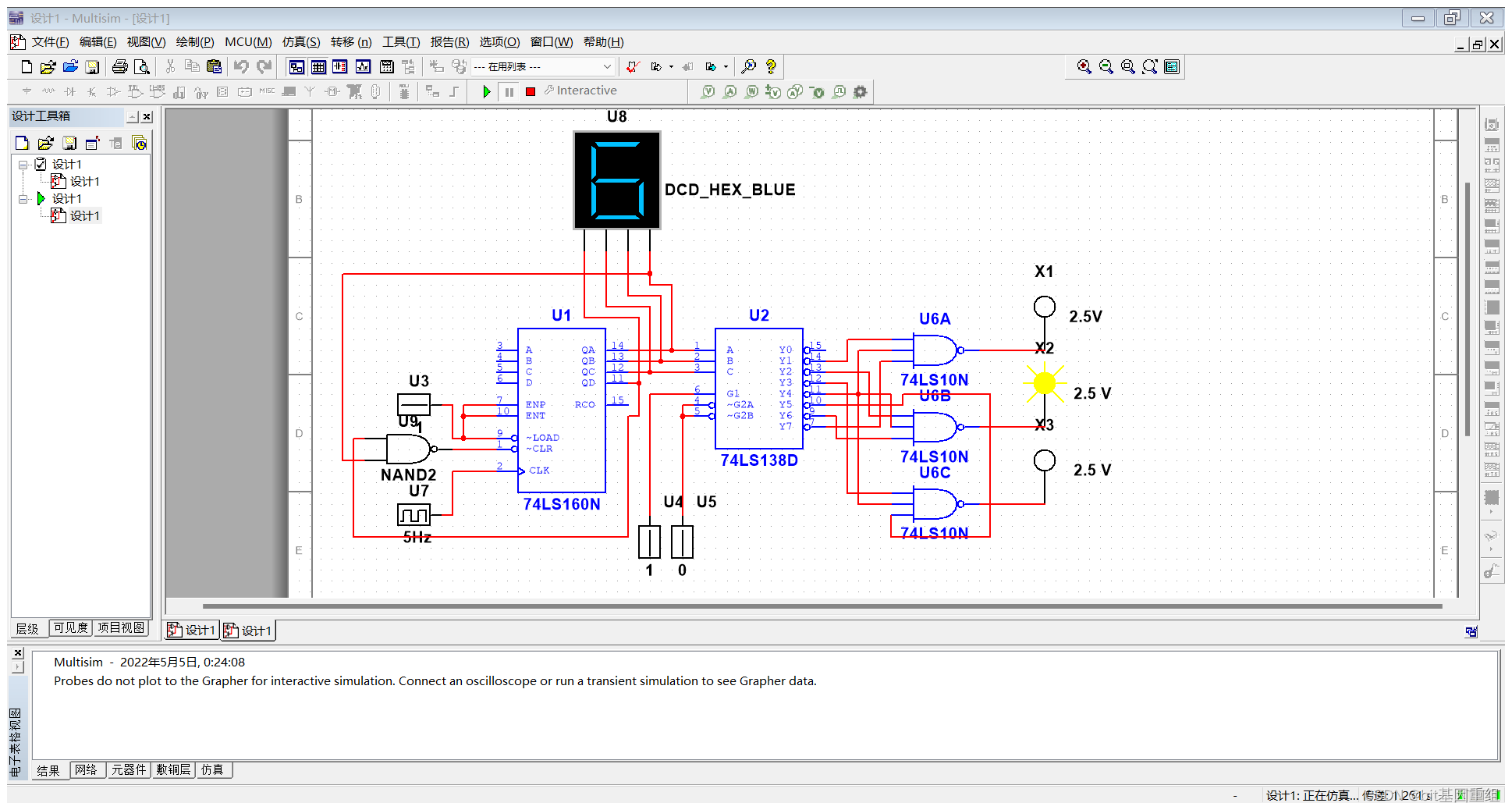

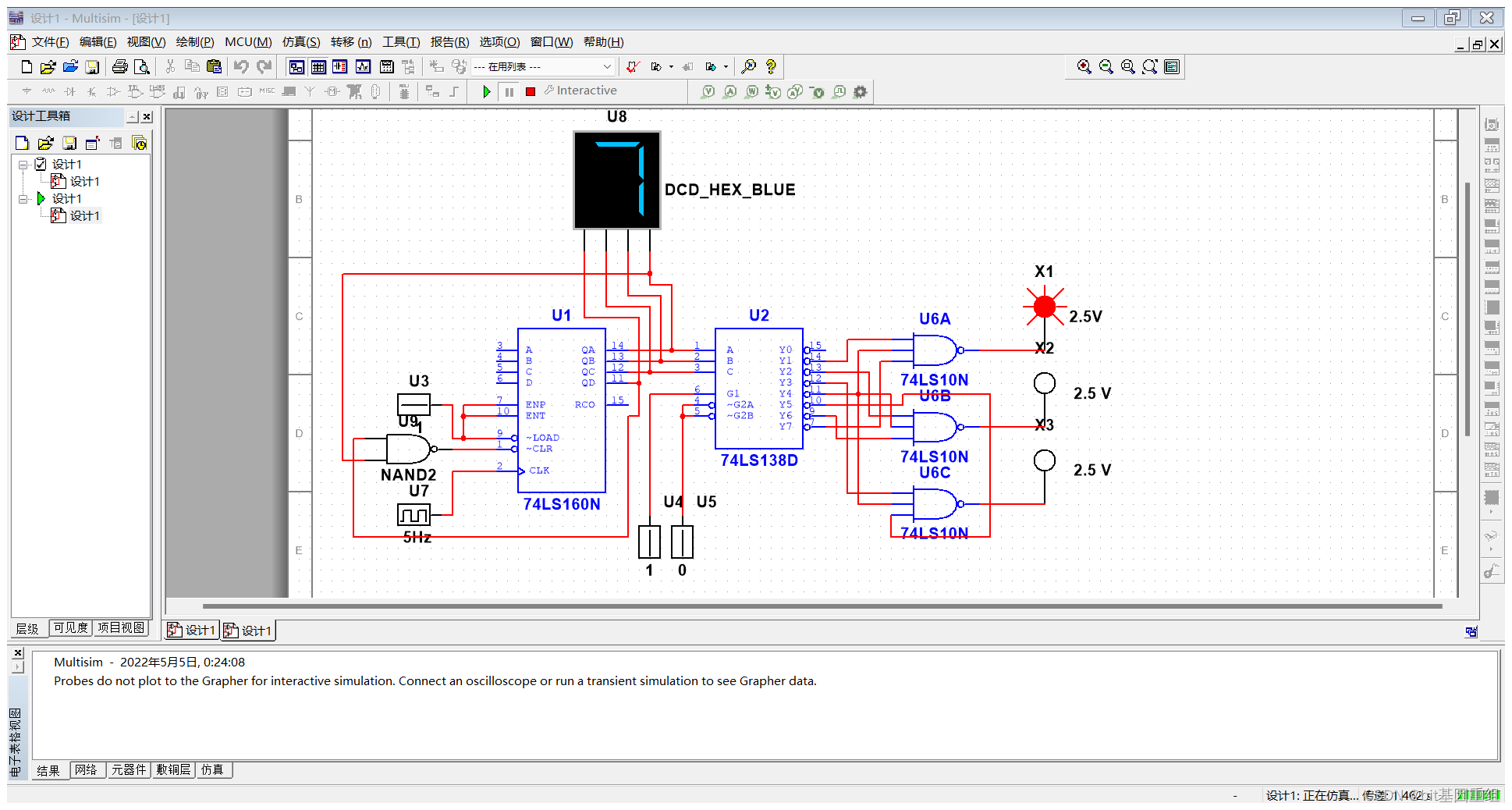

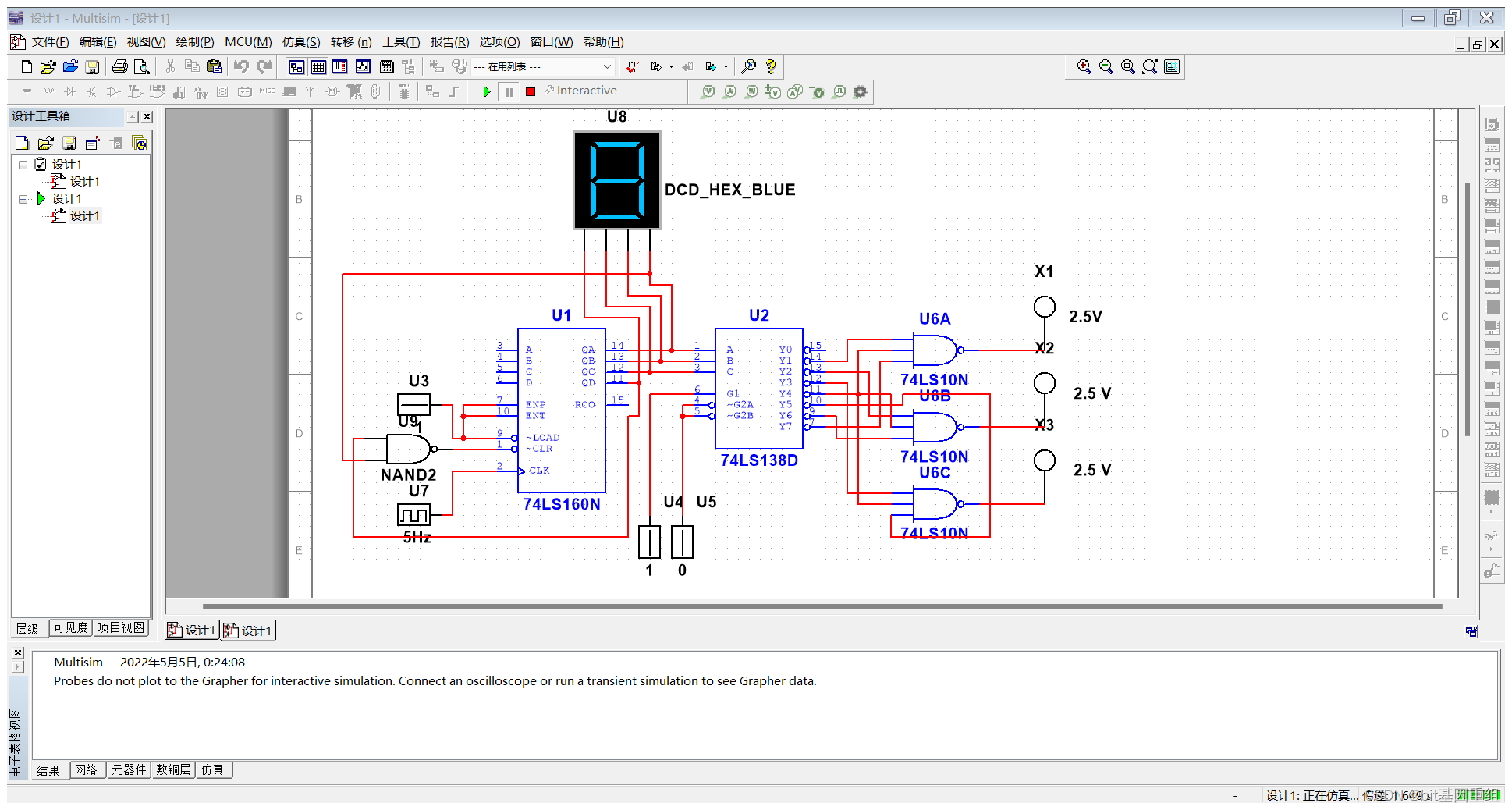

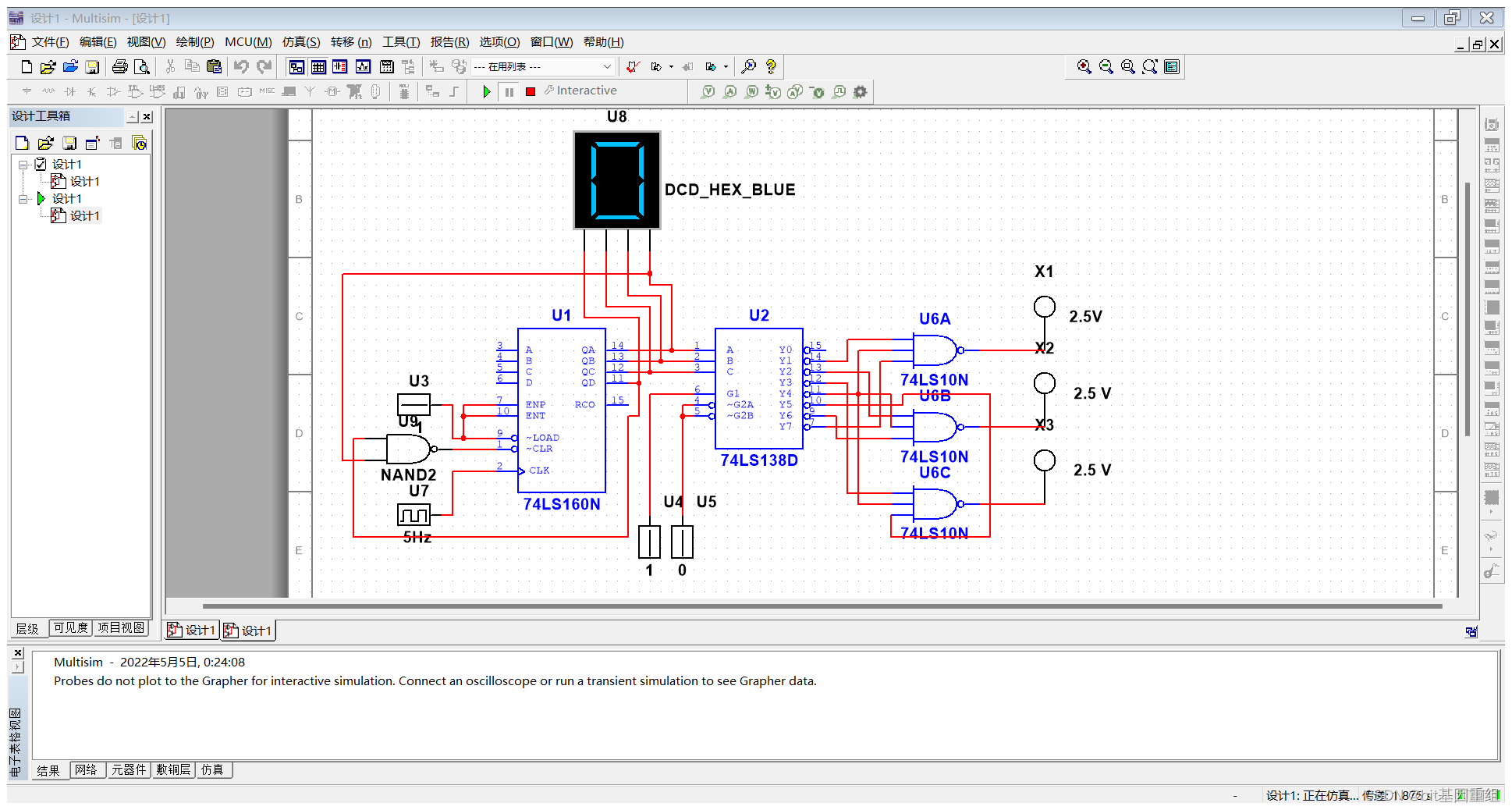

图 2-1红绿灯电路 实验软件与环境软件 Multisim 14.2 环境 Windows 11 专业版21H2 设备名称 DESKTOP-RHF1A50 处理器 AMD Ryzen 7 5800H with Radeon Graphics 3.20 GHz 机带 RAM 32.0 GB (31.9 GB 可用) 设备 ID 1FF45BCA-F318-4B49-8B8B-855EA1F13783 产品 ID 00330-80000-00000-AA096 系统类型 64 位操作系统, 基于 x64 的处理器 实验内容与步骤实验内容:用74LS160和74LS138(3线—8线译码器)和必要的门电路设计一个灯光控制逻辑电路。 要求红、绿、黄三种颜色的灯在时钟信号作用下按下表规定的顺序转换状态。表中的1表示“亮”,0表示“灭”。要求电路能自启动。三个灯接到LED上进行显示。首先写出状态转换表: CP顺序 R G B 0 1 2 3 4 5 6 7 8 0 1 0 0 1 0 0 1 0 0 0 1 0 1 0 1 0 0 0 0 0 1 1 1 0 0 0 由于输出为8个状态循环,因此考虑将74LS160采用到清零法接成九进制计数器。即在QD QC QB QA=1001时给CR一个低电平信号将其清零,接法如电路图所示。 写出计数器输出真值表: CP 74LS160 74LS138 color QD QC QB QA Y 0 0 0 0 0 0 x 1 0 0 0 1 1 R 2 0 0 1 0 2 Y 3 0 0 1 1 3 G 4 0 1 0 0 4 ALL 5 0 1 0 1 5 G 6 0 1 1 0 6 Y 7 0 1 1 1 7 R 8 1 0 0 0 0 x 观察发现QC QB QA共为八个不同的状态,结合到74ls138的逻辑功能将其结合到电路中。 通过真值表得到逻辑关系式为: 根据该表达式设计出的四舍五入判别电路,电路图如下。

按照真值表进行测试,功能完全符合。

实验收获、体会与建议 加深了设计时序逻辑电路的设计过程的熟练程度,掌握了multisim软件的基本操作和功能。比用纸笔做题有更直观的反馈效果能知道电路的正误和具体的运行过程。 通过本实验,加深了译码器应用的理解,对计时器的具体应用有了初步体会。 |

【本文地址】