| 数电 | 您所在的位置:网站首页 › 74LS162功能真值表 › 数电 |

数电

|

六十进制计数器设计

实验目的

掌握时序逻辑电路的分析和设计方法,以及仿真测试方法。 实验原理电路由两个74160N计数器、两个74LS47D七段显示译码器、一个与非门及两个数码显示器组成 实验内容(一)、六十进制计数器介绍和原理 1. 电路原理分析 六十进制计数器组成由计数器、译码器、显示器三个部分组成。工作过程:由一个1kHz的电源输出秒脉冲信号,再把秒脉冲信号送入计数器进行计数,并把累计的计数结果以以数字显示出来。显示由计数器和译码器组成六十进制计数器电路来实现。 (二)六十进制计数器的工作原理 六十进制计数器由一个模6的计数器和一个模10的计数器组成,模10的计数器完成一个周期时输出信号给模6计数器,当模10计数器计数到达10时则清零,同时给模6计数器一个信号,开始新一轮计数,模6计数器达到6时则清零,模6计数器选择QB,QC端做反馈端,经过与非门输出控制清零端CLR,形成6进制计数形式。

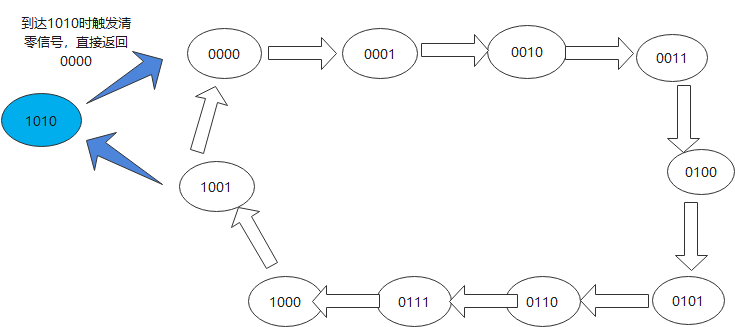

(三)六十进制计数器的设计方案 1.十进制计数器 十进制计数器功能表 十进制 计数状态 D3 D2 D1 D0 0 0 0 0 0 1 0 0 0 1 2 0 0 1 0 3 0 0 1 1 4 0 1 0 0 5 0 1 0 1 6 0 1 1 0 7 0 1 1 1 8 1 0 0 0 9 1 0 0 1 十进制计数器状态图

以上循环状态图使用的是反馈清零法构造的模10计数器。 当第十个脉冲上升沿到达时,输出1010时,通过一个与非门译码后,反馈给异步清零输入端一个清零信号,立即使得状态从1010返回到0000状态,实现不断循环的状态且只有10个状态。 2.六进制计数器 六进制计数器功能表 十进制 计数状态 D3 D2 D1 D0 0 0 0 0 0 1 0 0 0 1 2 0 0 1 0 3 0 0 1 1 4 0 1 0 0 5 0 1 0 1 六进制计数器状态图

3.七段显示译码器实现 七段显示译码器是由七段数字管组成,a,b,c,d,e,f,g各控制一段发光管。 七段显示译码器

七段显示译码器功能真值表 十进制 输入 输出 字形 D3 D2 D1 D0 a b c d e f g 0 0 0 0 0 1 1 1 1 1 1 0 0 1 0 0 0 1 0 1 1 0 0 0 0 1 2 0 0 1 0 1 1 0 1 1 0 1 2 3 0 0 1 1 1 1 1 1 0 0 1 3 4 0 1 0 0 0 1 1 0 0 1 1 4 5 0 1 0 1 1 0 1 1 0 1 1 5 6 0 1 1 0 0 0 1 1 1 1 1 6 7 0 1 1 1 1 1 1 0 0 0 0 7 8 1 0 0 0 1 1 1 1 1 1 1 8 9 1 0 0 1 1 1 1 1 0 1 1 9 显示器由abcdefg共7个数码管组成,译码器的那些输出Y,就是显示器的输入,每一个输出Y对应每一个abcdefg中的一个,当译码器的Y=1时,对应的数码管点亮,也就形成了数字的效果。 (四)总电路设计图

当点击开始时,右边的十进制计数器开始计数,一旦达到9的时候就清零重新开始计数,达到9的那一刻十进制计数器输出信号给左边的六进制数,六进制数开始计数,一旦六进制达到6时,六进制计数器清零开始重新计数。 |

【本文地址】

| 今日新闻 |

| 推荐新闻 |

| 专题文章 |