| 【精选】从零开始的FPGA学习(2)(用三八译码器实现一位全加器) | 您所在的位置:网站首页 › 73ls138译码器 › 【精选】从零开始的FPGA学习(2)(用三八译码器实现一位全加器) |

【精选】从零开始的FPGA学习(2)(用三八译码器实现一位全加器)

|

从零开始的FPGA学习(2)

第二个任务:用三八译码器实现一位全加器基础任务和提高任务三八译码器源文件三八译码器仿真

拓展任务 (含封装IP核)IP核封装一位全加器源文件一位全加器仿真最终实现

第二个任务:用三八译码器实现一位全加器

基础任务和提高任务

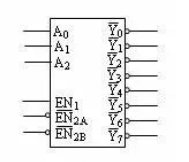

(1)基础任务:设计一个带有使能端的三八译码器,要求使能端输入由三个,一个高电平输入有效,两个低电平输入有效,输入端是高电平输入有效,输出端是低电平输出有效,即74LS138,拨码开关作为输入,发光二极管作为输出。 (2)提高任务:在基础任务的基础上,输出用一位数码管显示输出是第几位。 首先第一步:我们需要实现一个三八译码器 什么是三八译码器?数电的知识,稍微复习一下。 下图便是一个常见的三八译码器,和基础任务相对应其中A0,A1,A2三个输入端,Y0-7为八位输出端,EN1,EN2A,EN2B为三位使能端后两个端口和八位输出低电平有效(既:为 0 时有效) 接下来实现三八译码器 1.源文件:(包括提高任务中的输出数码管) module Decoders(A,E1,E2_low,E3_low,Y_low,sem); input [2:0] A; //3位输入 input E1; //高电平有效使能端 input E2_low; //低电平有效使能端 input E3_low; //低电平有效使能端 output reg[7:0] Y_low; //8位输出,低电平有效 output reg[6:0] sem; //一位数码管显示输出是第几位 7段数码管 //在always模块中的被赋值变量均为寄存器类型! always @ (A or E1 or E2_low or E3_low) //行为语句模块,敏感信号 begin if(E1 && ~E2_low && ~E3_low) //使能输入有效 case(A) 3'b000 : Y_low = 8'b11111110; 3'b001 : Y_low = 8'b11111101; 3'b010 : Y_low = 8'b11111011; 3'b011 : Y_low = 8'b11110111; 3'b100 : Y_low = 8'b11101111; 3'b101 : Y_low = 8'b11011111; 3'b110 : Y_low = 8'b10111111; 3'b111 : Y_low = 8'b01111111; default : Y_low = 8'b11111111; endcase //case模块结束 else //使能端无效情况 Y_low = 8'b11111111; end //if模块结束 always @ (A or E1 or E2_low or E3_low) //7段数码管显示哪一位输出 begin if(E1 && ~E2_low && ~E3_low) case(A) 3'b000 : sem = 7'b0111111; 3'b001 : sem = 7'b0000110; 3'b010 : sem = 7'b1011011; 3'b011 : sem = 7'b1001111; 3'b100 : sem = 7'b1100110; 3'b101 : sem = 7'b1101101; 3'b110 : sem = 7'b1111101; 3'b111 : sem = 7'b0000111; default : sem = 7'b0111111; endcase end endmodule 三八译码器仿真2.仿真 检查结果: module sim1(); //声明模块 reg [2:0] A; reg E1; //输入端用寄存器类型声明 reg E2_low; reg E3_low; wire [7:0] Y_low; //输出端用网线类型声明 wire [6:0] sem; //7段数码管 Decoders text(.A(A), .E1(E1), .E2_low(E2_low), .E3_low(E3_low),.Y_low(Y_low),.sem(sem)); //调用设计模块 initial begin //变量初始化 E1 = 0; E2_low = 0; E3_low = 0; //使能无效 A = 3'b000; #100 //延时100ns E1 = 1; E2_low = 0; E3_low = 0; //使能有效 A = 3'b001; #100 A = 3'b010; #100 A = 3'b011; #100 A = 3'b100; #100 A = 3'b101; #100 A = 3'b110; #100 A = 3'b111; end endmodule仿真后波形图: 一切顺利下面将写好的三八译码器封装成IP核 ⬇ 拓展任务 (含封装IP核)拓展任务:将所设计三八译码器封装成IP核,并用它和相应的门电路设计一位全加器,输出结果由发光二极管显示。 IP核是什么?个人理解IP核类似于以前我们学过的自定义函数,封装成一个IP核后,我们可以直接用传入参数使用IP核,类似于调用函数。 IP核封装IP核封装步骤: 1 .Tools中找到并点击Create and Package New IP 然后NEXT Si(Ai,Bi,Ci-1)=∑m(1,2,4,7)=m1+m2+m4+m7 Ci(Ai,Bi,Ci-1)=∑m(3,5,6,7)=m3+m5+m6+m7 一位全加器源文件源文件: module adder(A,E1,E2_low,E3_low,Si,Ci,sem,an ); //(A,E1,E2_low,E3_low,Y_low,sem) input [2:0]A; //Ai Bi 两位输入 Cin表示进位 input E1,E2_low,E3_low; output Si,Ci; //Si 表示求和 Ci 表示进位 output [6:0] sem; //段选信号 output reg an=1'b1 ; //位选信号 wire [7:0]m; //38译码器 8位输出 Decoders_0 u1(A,E1,E2_low,E3_low,m,sem);//调用38译码器IP核 assign Si = ~m[1] | ~m[2] | ~m[4] | ~m[7]; assign Ci = ~m[3] | ~m[5] | ~m[6] | ~m[7]; endmodule 一位全加器仿真仿真文件:(没有加位选信号 仿真用不上 上面源文件有位选信号) module sim_adder(); reg [2:0] A; reg E1,E2_low,E3_low; wire Si,Ci; wire [0:6] sem; adder f1(A,E1,E2_low,E3_low,Si,Ci,sem); initial begin //变量初始化 E1 = 0; E2_low = 0; E3_low = 0; //使能无效 //Ai = 1'b0; Bi = 1'b0 ; Cin = 1'b0 A = 3'b000; #100 //延时100ns E1 = 1; E2_low = 0; E3_low = 0; //使能有效 //Ai = 1'b0 ; Bi = 1'b0 ; Cin = 1'b1; A = 3'b001; #100 //Ai = 1'b0 ; Bi = 1'b1 ; Cin = 1'b0; A = 3'b010; #100 //Ai = 1'b0 ; Bi = 1'b1 ; Cin = 1'b1; A = 3'b011; #100 //Ai = 1'b1 ; Bi = 1'b0 ; Cin = 1'b0; A = 3'b100; #100 //Ai = 1'b1 ; Bi = 1'b0 ; Cin = 1'b1; A = 3'b101; #100 //Ai = 1'b1 ; Bi = 1'b1 ; Cin = 1'b0; A = 3'b110; #100 //Ai = 1'b1 ; Bi = 1'b1 ; Cin = 1'b1; A = 3'b111; end endmodule仿真波形图: 电路原理图: 添加约束文件 跑板子喽(我选的型号xc7a35tcsg324-1) set_property -dict {PACKAGE_PIN R1 IOSTANDARD LVCMOS33} [get_ports {A[0]}] set_property -dict {PACKAGE_PIN N4 IOSTANDARD LVCMOS33} [get_ports {A[1]}] set_property -dict {PACKAGE_PIN M4 IOSTANDARD LVCMOS33} [get_ports {A[2]}] set_property -dict {PACKAGE_PIN R2 IOSTANDARD LVCMOS33} [get_ports {E1}] set_property -dict {PACKAGE_PIN P2 IOSTANDARD LVCMOS33} [get_ports {E2_low}] set_property -dict {PACKAGE_PIN P3 IOSTANDARD LVCMOS33} [get_ports {E3_low}] set_property -dict {PACKAGE_PIN G4 IOSTANDARD LVCMOS33} [get_ports {Ci}] set_property -dict {PACKAGE_PIN F6 IOSTANDARD LVCMOS33} [get_ports {Si}] set_property -dict {PACKAGE_PIN G2 IOSTANDARD LVCMOS33} [get_ports {an}] set_property -dict {PACKAGE_PIN B4 IOSTANDARD LVCMOS33} [get_ports {sem[0]}] set_property -dict {PACKAGE_PIN A4 IOSTANDARD LVCMOS33} [get_ports {sem[1]}] set_property -dict {PACKAGE_PIN A3 IOSTANDARD LVCMOS33} [get_ports {sem[2]}] set_property -dict {PACKAGE_PIN B1 IOSTANDARD LVCMOS33} [get_ports {sem[3]}] set_property -dict {PACKAGE_PIN A1 IOSTANDARD LVCMOS33} [get_ports {sem[4]}] set_property -dict {PACKAGE_PIN B3 IOSTANDARD LVCMOS33} [get_ports {sem[5]}] set_property -dict {PACKAGE_PIN B2 IOSTANDARD LVCMOS33} [get_ports {sem[6]}]下面八个按键中 右边三个为三位输入,从右往左数4 5 6为三位使能端 图中为0 0 1 ,两位低电位一位高电位,输出用最左边的两个二极管作为输出 第一种情况参考上面真值表第二行 输入为 0 0 1 输出为 1 0

|

【本文地址】

***三八译码器真值表:***

***三八译码器真值表:***

2.选择我们当前写好的三八译码器源文件封装NEXT后确定地址

2.选择我们当前写好的三八译码器源文件封装NEXT后确定地址  3.导入IP核 Settings —— IP —— Repository 点击 + 找到上面IP所在地址 点击OK

3.导入IP核 Settings —— IP —— Repository 点击 + 找到上面IP所在地址 点击OK  4.找到IP核并右键点击找到customize IP ( 客户化IP核,IP核的调用)

4.找到IP核并右键点击找到customize IP ( 客户化IP核,IP核的调用)  点击Generate

点击Generate  接下来,调用IP核实现一位全加器:

接下来,调用IP核实现一位全加器:  化简可得 Si和 Ci的表达式:

化简可得 Si和 Ci的表达式:

参考真值表第六行 输入 1 0 1 输出 0 1

参考真值表第六行 输入 1 0 1 输出 0 1  参考真值表最后一行,输入为 1 1 1 输出为1 1

参考真值表最后一行,输入为 1 1 1 输出为1 1