| Quartus手动生成波形图(以38译码器为例)VHDL | 您所在的位置:网站首页 › 3-8译码器代码if › Quartus手动生成波形图(以38译码器为例)VHDL |

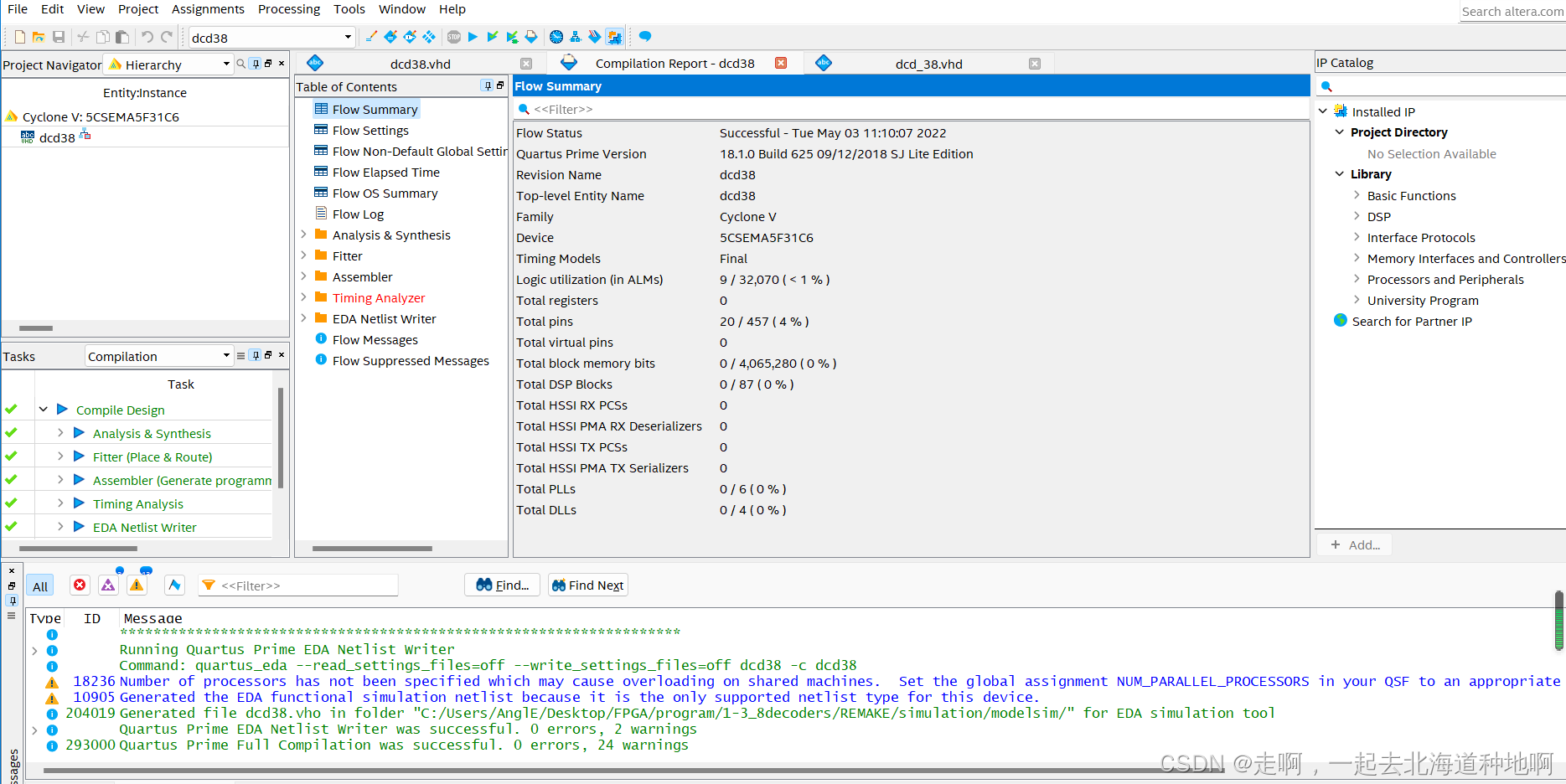

Quartus手动生成波形图(以38译码器为例)VHDL

|

1.新建工程输入代码并运行 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY dcd_38 IS PORT(A:IN STD_LOGIC_VECTOR(2 DOWNTO 0); --输入端 LED8S1:OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); --输出端 END dcd_38; ARCHITECTURE behave OF dcd_38 IS --实现CASE语句 BEGIN PROCESS(A) --顺序执行 BEGIN CASE A IS WHEN "000" =>LED8S1LED8S1LED8S1LED8S1LED8S1LED8S1LED8S1LED8S1NULL; END CASE; END PROCESS; END behave;

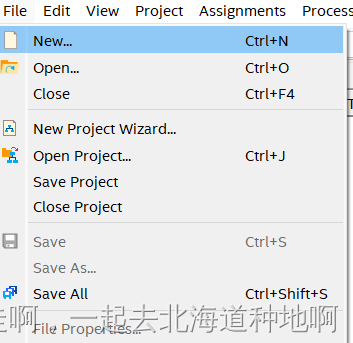

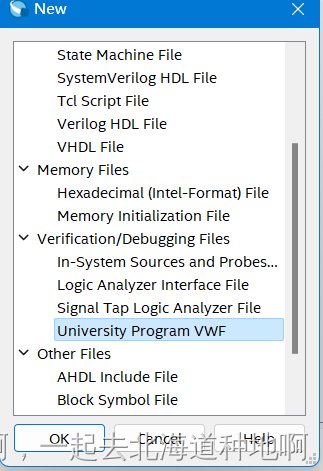

2.建立波形图文件 file-new-University Program VMF-OK

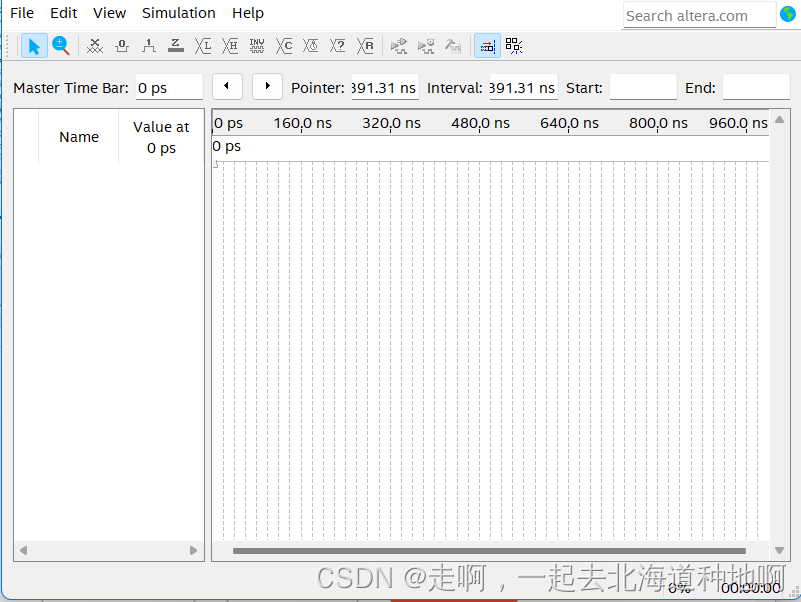

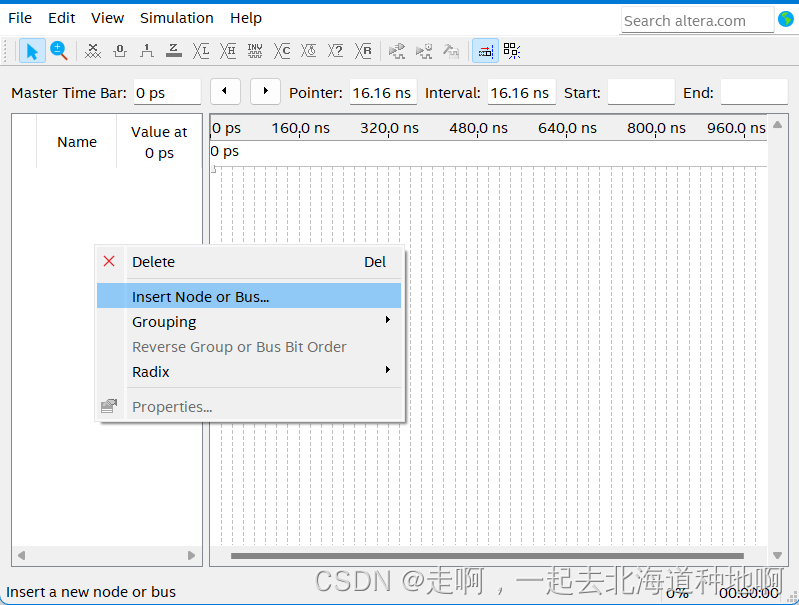

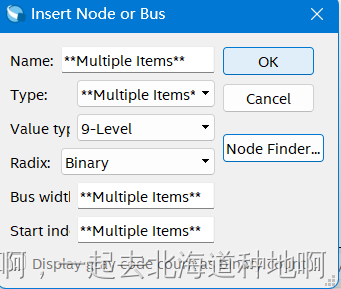

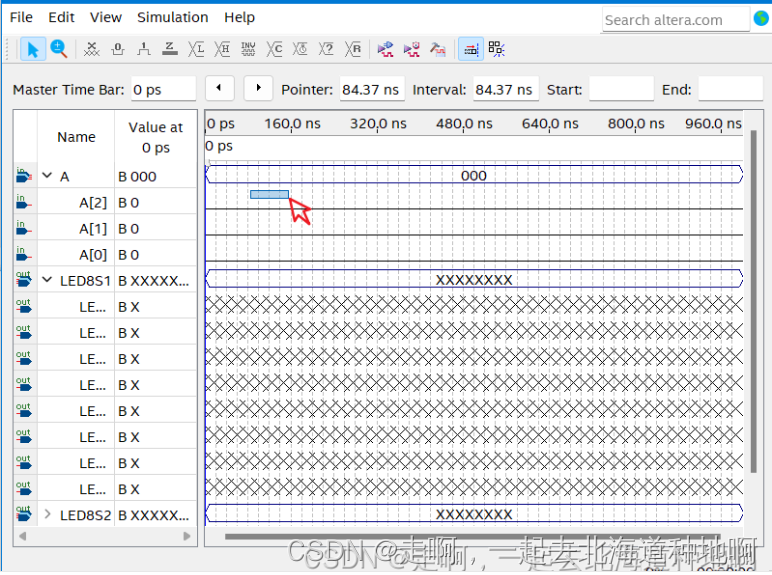

3.节点设置、绘制输入端波形 右击左边空白框,选择insert node...

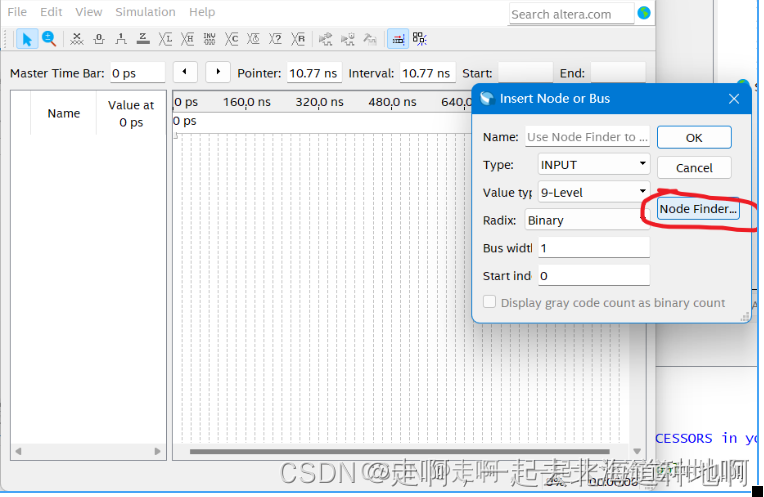

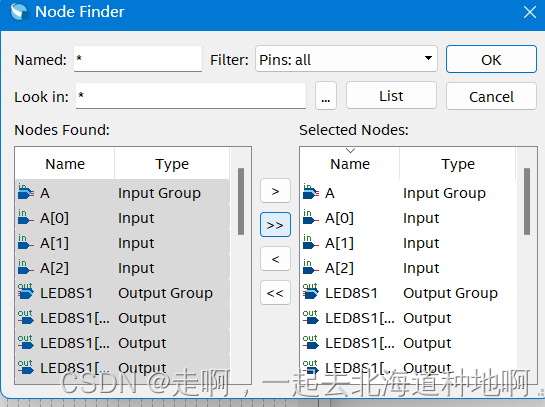

单击node finder

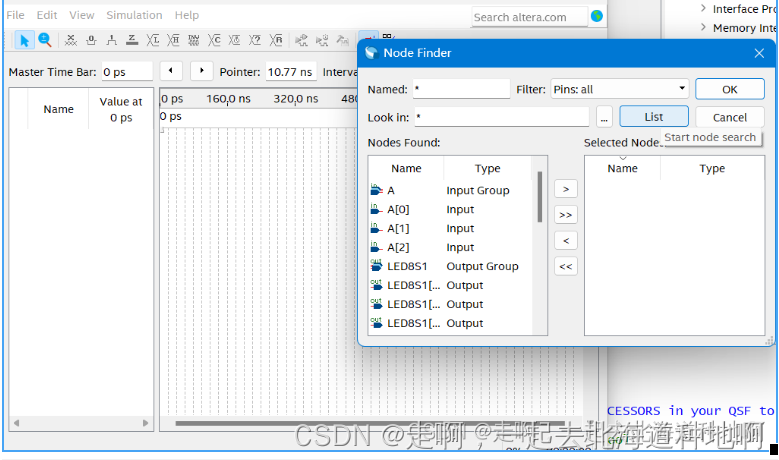

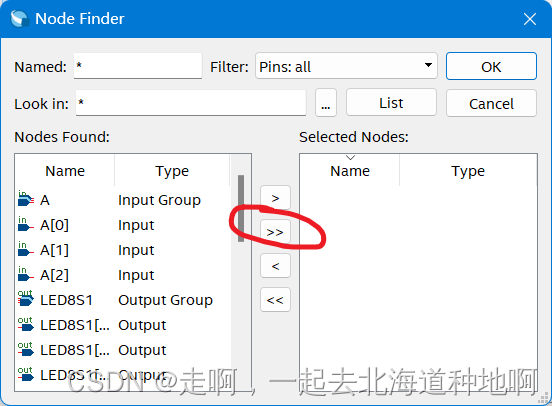

点击list

点击红圈内,将节点全部导入-OK-OK

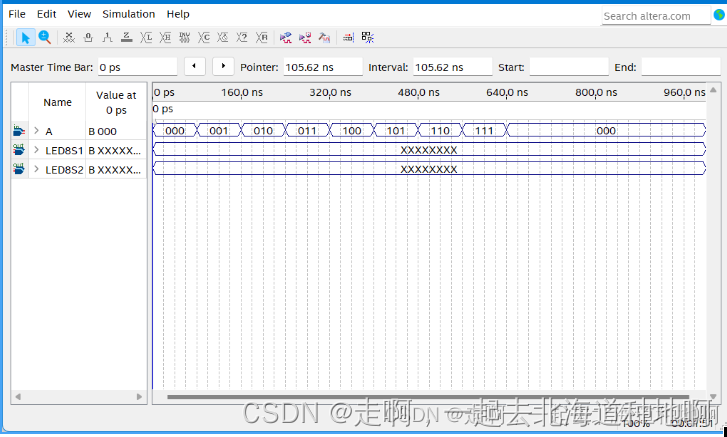

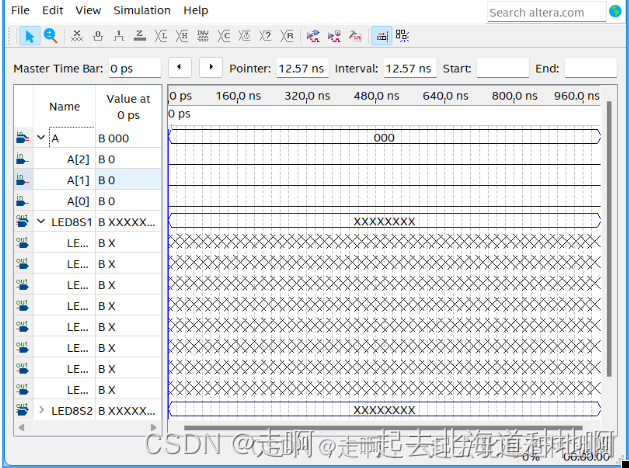

展开

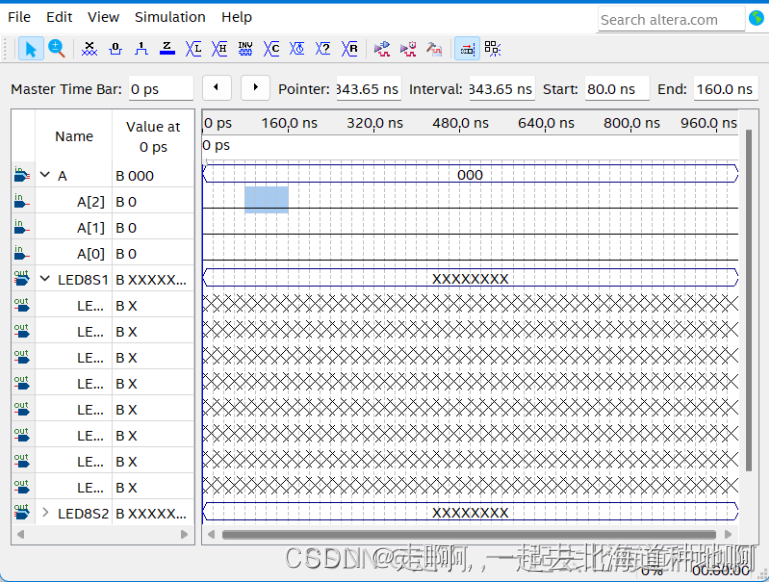

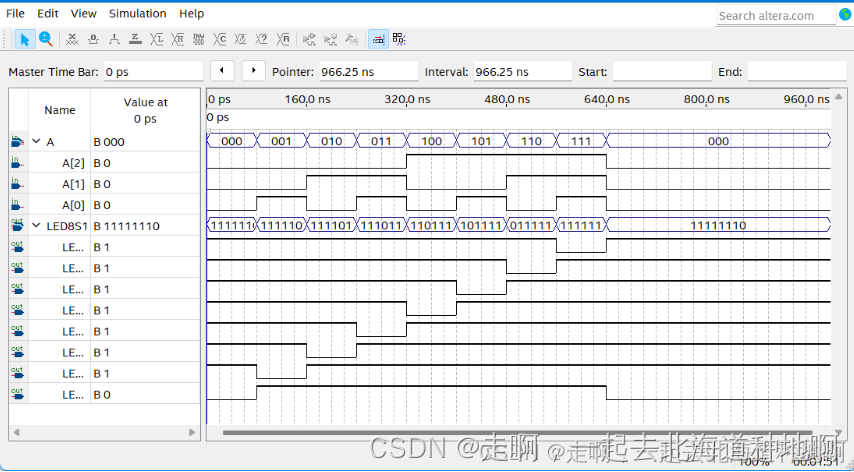

A为38译码器输入端,LED为输出端。 鼠标滑动选择40ms

松开鼠标左键,已选中

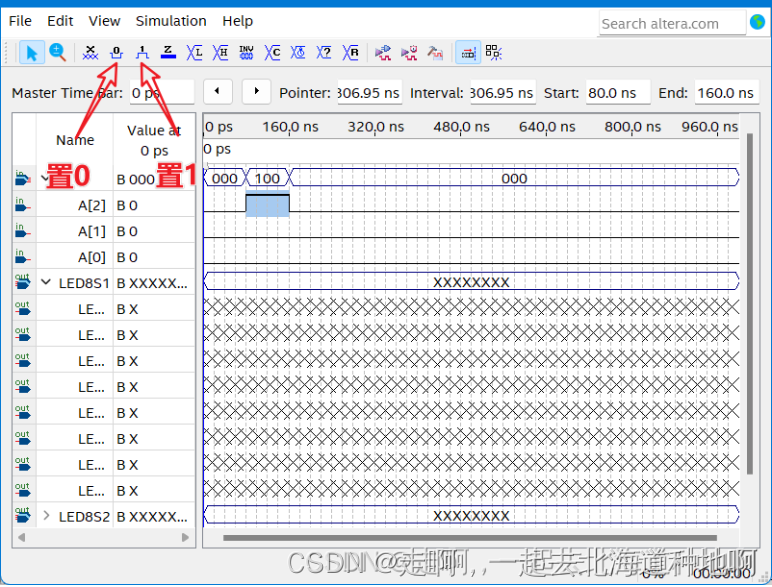

置数完毕

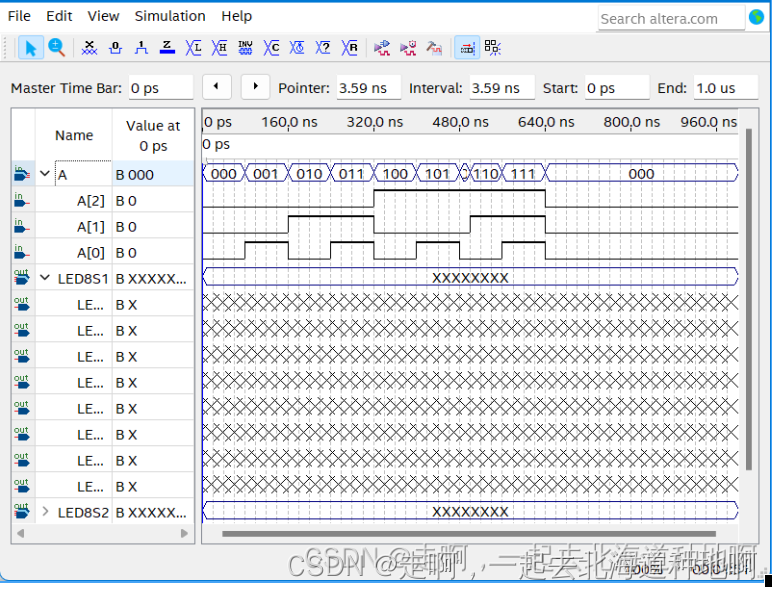

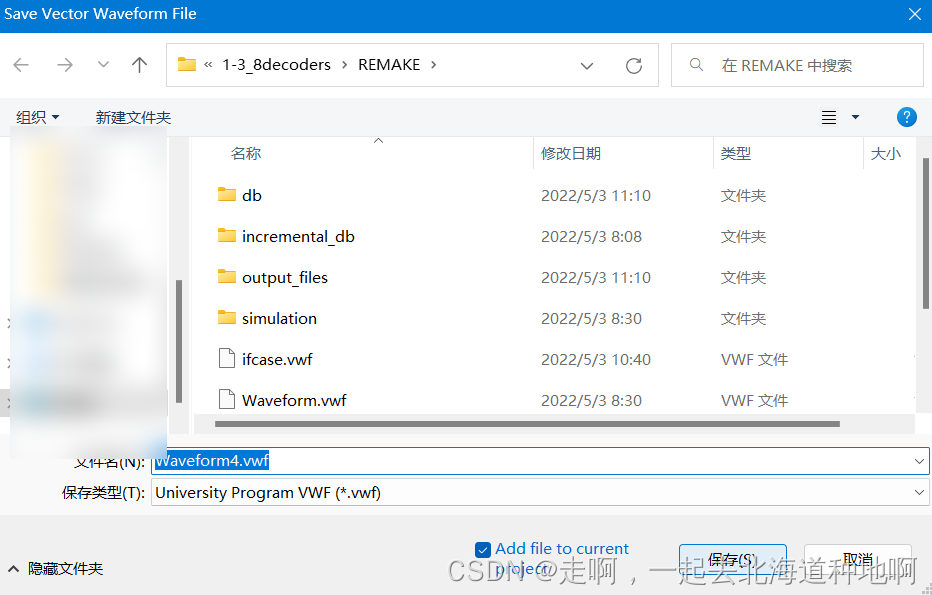

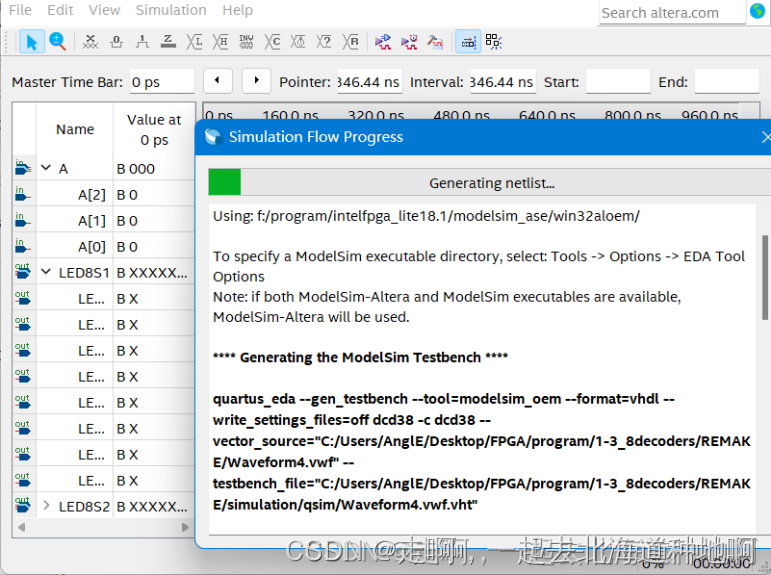

4.仿真 simulation-run functional simulation-yes-保存

仿真完成!

|

【本文地址】

公司简介

联系我们