| GPIO口有关上拉电阻和下拉电阻&推挽输出&开漏(OD)和开集(OC) | 您所在的位置:网站首页 › 2092芯片输出需要加电阻吗 › GPIO口有关上拉电阻和下拉电阻&推挽输出&开漏(OD)和开集(OC) |

GPIO口有关上拉电阻和下拉电阻&推挽输出&开漏(OD)和开集(OC)

|

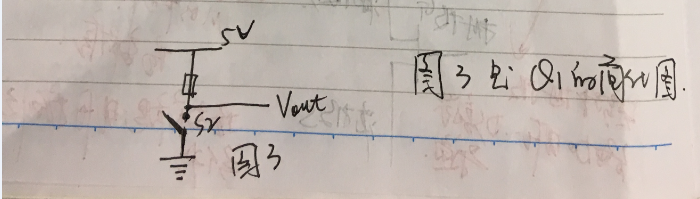

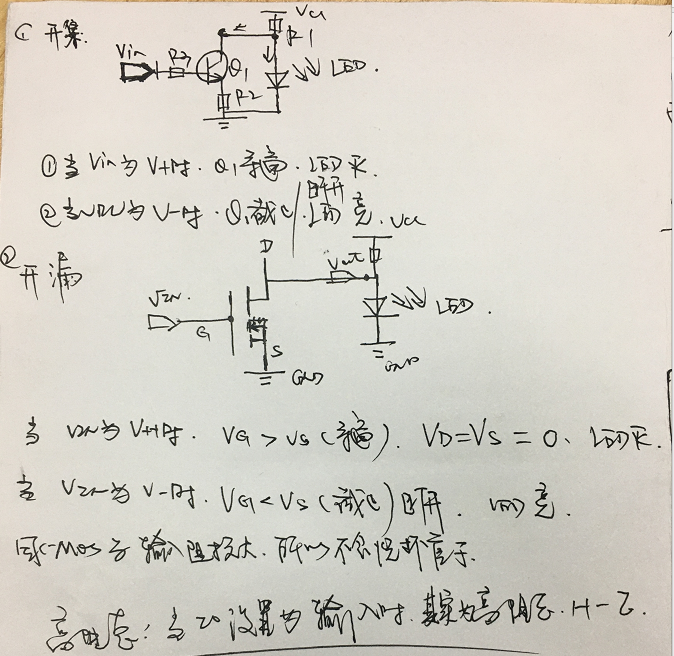

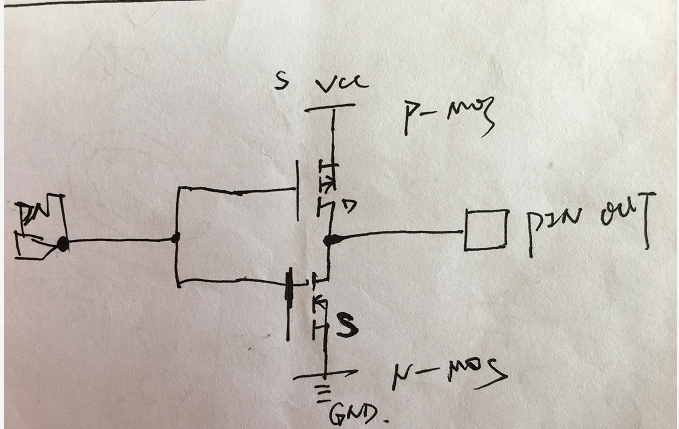

嵌入式软件开发中,操作GPIO口是最常见的事情,可以通过软件配置GPIO口的模式,比如输入或输出,上拉或下拉,推挽或开漏等等,为了理解这些概念需要查看芯片内部GPIO口电路图。 1、推挽输出:推状态时,电流会从GPIO口流出,挽状态时电流会流入(吸收电流)GPIO口。推状态GPIO口为高电平,挽状态GPIO为低电平。 2、开漏输出:控制寄存器设置GPIO为“0”时,此时GPIO口输出为低电平,控制寄存器设置GPIO为“1”时,此时GPIO口的状态由外部电路决定(对于开漏电路,外部会接一个上拉电阻),一般情况也为高电平。 3、高组态(H-Z):高阻状态,既不是高电平也不是低电平,状态由外部电路决定。高组态不是断路,只是内阻很大。GPIO口设置为输入时,此时可以认为为高组态;GPIO设置为开漏输出时,而且寄存器设置为为“1”时,此时也可以认为为高阻态。 高组态是数字电路中的术语,指电路的一种输出状态,不是低电平也不是高电平。若高阻态输入到下一级电路,对下一级电路无任何影响,和没有接是等同效果,电路特性由下级电路决定。高阻态时引脚对地电阻无穷大,此时读引脚电平时可以读到真实电平值。高阻态意义:如果当上/下拉管都截止时,输出端相当于浮空(没有电流流动),其电平随外部电平高低而定,即该门电路放弃对输出端电路的控制;高阻态是一个相对概念,一个系统或一个整体中,往往会定义一个参考点,无论是高电平还是低电平都是相对来说;如何防止高阻态时,ESD对该状态影响?电源和地的内阻都很小。 一、上拉电阻 图1 二、下拉电阻 图2 图3 补充内容:GPIO的驱动能力,其实就是允许的最大电流能力。 三、开集 图4 图5 图5所述的三极管为NPN型,晶体管工作时,发射结正偏,集电结反偏,基极流入电流,而且此时电流会从集电极流入发射极。(自由电子方向和电流方向刚好相反) 发射结正偏:PN结加正向电压,即基极电压高于发射极电压; 集电结反偏:PN结加反向电压,即基极电压低于集电极电压; 图6 图6所述的三极管为PNP型,晶体管工作时,发射极正偏,集电极反偏,基极流出电流,而且此时电流会从发射极流入集电极。(自由电子方向与电流方向刚好相反) 四、开漏 图7 图7所示,该电路为OC(open collecter)开集电路,并且此时三极管当做开关器件;若三极管当做开关器件,那么只能工作在截止区和饱和区,不能工作在放大区。 放大区:集电极电流Ic为基极电流Ib的m倍,即集电极电流跟基极电流成线性关系。(三极管是电流放大器件,流控型器件) 饱和区:当基极电流持续加大,加大到集电极电流跟基极电流不再是线性关系,且不会再随着基极电流增大而增大时,那么可以认为此时三极管进入了饱和区,当继续加大基极电流,三极管讲进入深度饱和区。在饱和区时,Uce此时电压很小,即内阻很小,那么可以认为C和E两端是闭合状态。 图8 图8所示:器件为MOS管,假设该MOS管为N沟道管,且源极S接地, 那么 当栅极为高电平时,UGS > 0,此时MOS管导通,当栅极为低电平时,UGS = 0,此时MOS管不导通。 图9 图9主要内容:对于OC、OD电路特性,由于MOS管输入输出电流较小,不会损坏MOS管,而三极管不同,所以目前常用的为OD电路。 图10 图10所示:呈现的是三极管的导通和截止电路,末端是OC电路。 图11 图12 图12讲解了OC和OD控制LED亮和灭电路。 开漏电路特点: 用外部驱动能力,减少IC内部驱动,或驱动比芯片电源电压高的负载;多个OD pin连接在一起,形成线与逻辑,I2C、SMBus判断总线占用状态原理;可以利用低电压控制输出高电压;开漏pin外部不接上拉电阻,则只能输出低电平;标准开漏pin一般只有输出能力,添加其他判断电路,才具备双向输入、输出的能力;正常的CMOS输出是上下两个管子,把上面管子去掉就是OD电路,OD电路的主要目的是为了“线与”。 总线上的pin都是用OD方式,这样可以防止短路情况,烧坏管子。(当总线上有高有低时,此时高电平会经过外部上拉电阻再流入总线上的低电平,起到短路作用。而推挽输出就会出现短路情况) 五、推挽输出 图12 图13 图12是一个典型的双三极管push-pull电路。Q1为NPN型,Q2为PNP型,Q1和Q2共发射极。Q1充当PUSH电路,Q2充当PULL电路,push电路提供电流,pull电路吸收电流。 图14 图14所示:该电路为两个MOS组成的push-pull电路,上面为PMOS,下面为NMOS,两者共用漏极D。VIN输入后会经过一个反相器,然后连接到栅极G。工作原理如下: 当VIN为高电平时,经过反相器后,栅极G电平为低电平,此时上面PMOS管导通(Vsg > 0),下面NMOS管截止(Vgs = 0),此时VOUT为PMOS管S极电压,即高电平。当VIN为低电平时,经过反相器后,栅极G电平为高电平,此时上面PMOS管截止(Vsg = 0),下面NMOS管导通(Vgs > 0),此时VOUT为NMOS管S极电压,即低电平。 |

【本文地址】