Verilog有符号数与无符号数的数值运算 |

您所在的位置:网站首页 › 有符号计算 › Verilog有符号数与无符号数的数值运算 |

Verilog有符号数与无符号数的数值运算

|

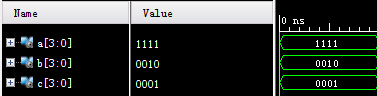

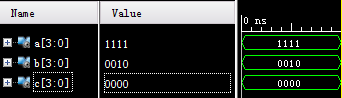

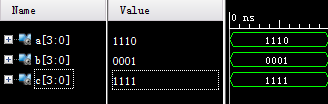

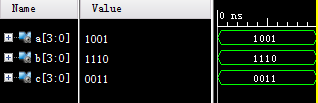

版权声明:本文为博主原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。 本文链接:https://blog.csdn.net/u014485485/article/details/79962316 仿真工具:Vivado 2015.2 一、无符号数 1.高位溢出赋给一个位宽不够的数 wire [3:0] a=4’b1111;//15 wire [3:0] b=4’b0010;//2 wire [3:0] c; assign c = a + b;//17=10001

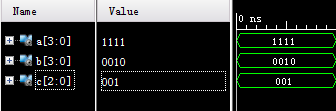

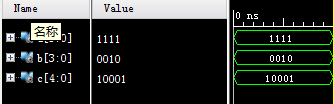

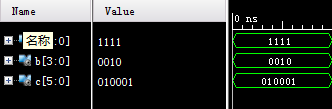

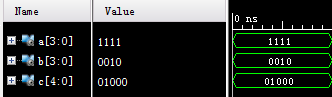

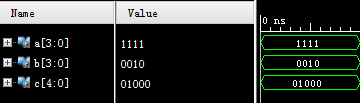

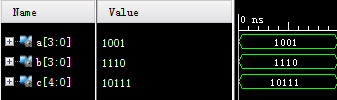

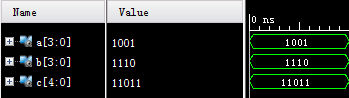

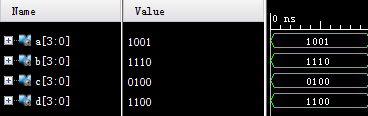

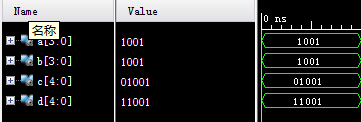

assign c = a + b; 高位截断,保留低位 2.高位溢出赋给一个位宽足够的数 wire [3:0] a=4’b1111; wire [3:0] b=4’b0010; wire [4:0] c; assign c = a + b; wire [3:0] a=4’b1111; wire [3:0] b=4’b0010; wire [5:0] c; assign c = a + b; 3.对中间结果移位 wire [3:0] a=4’b1111; wire [3:0] b=4’b0010; wire [3:0] c; assign c =(( a + b) >> 1); //17=10001

wire [3:0] a=4’b1111; wire [3:0] b=4’b0010; wire [4:0] c; assign c =(( a + b) >> 1); //17=10001

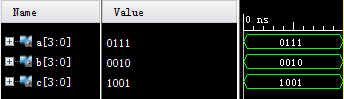

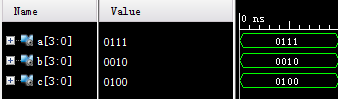

wire [3:0] a=4’b1111; wire [3:0] b=4’b0010; wire [4:0] c; assign c = ((a + b)>>>1) ; 二、有符号数 1.正常运算 wire signed [3:0] a=4’b1111;//-1 wire signed [3:0] b=4’b0010;//2 wire signed [3:0] c; assign c =a + b; wire signed [3:0] a=4’b1110;//-2 wire signed [3:0] b=4’b0001;//1 wire signed [3:0] c; assign c =a + b;

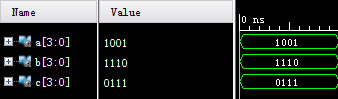

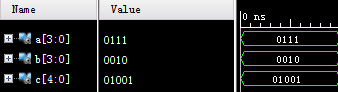

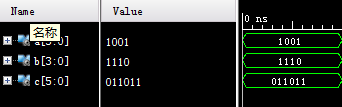

wire signed [3:0] a=4’b0111;//7 wire signed [3:0] b=4’b0010;//2 wire signed [3:0] c; assign c =a + b; //9=1001 wire signed [3:0] a=4’b1001;//-7 wire signed [3:0] b=4’b1110;//-2 wire signed [3:0] c; assign c =a + b;//-9=10111 3.赋给位宽足够的数 wire signed [3:0] a=4’b0111; wire signed [3:0] b=4’b0010; wire signed [4:0] c; assign c =a + b; wire signed [3:0] a=4’b1001;//-7 wire signed [3:0] b=4’b1110;//-2 wire signed [4:0] c; assign c =a + b;//-9=10111

4.给中间结果移位 wire signed [3:0] a=4’b1001;//-7 wire signed [3:0] b=4’b1110;//-2 wire signed [3:0] c; assign c =(( a + b ) >> 1); //-9=10111 wire signed [3:0] a=4’b1001; wire signed [3:0] b=4’b1110; wire signed [5:0] c; assign c = ((a + b)>>1) ; assign c =(( a + b ) >> 1);//9=01001 wire signed [3:0] a=4’b1001;//-7 wire signed [3:0] b=4’b1110;//-2 wire signed [3:0] c; assign c = ((a + b)>>>1) ; //-9=10111

wire signed [3:0] a=4’b1001; wire signed [3:0] b=4’b1110; wire signed [4:0] c; assign c = ((a + b)>>>1) ;

assign c=a>>1; assign d=a>>>1;

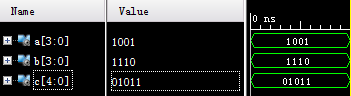

三、有符号数与无符号数运算 1.只有两个操作数都是有符号数,才会把两个操作数都看作有符号数计算,否则无论是有符号数还是无符号数都会按照无符号数计算。 wire [3:0] a=4’b1001; wire signed [3:0] b=4’b1110; wire signed [4:0] c; assign c = ((a + b)>>>1); //-9=10111

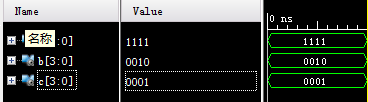

2.把a赋给b,若a是有符号数,则b高位用a的最高位填充,若a是无符号数,b的高位用0填充 。 wire [3:0] a=4’b1001; wire signed [3:0] b=4’b1001; wire signed [4:0] c,d; assign c=a; assign d=b; 符号位和符号位下一位相加(11+11)进位bit=11,根据上述判定是不溢出,最左侧进位自然舍弃 2) -2 1 1110 + 5 0 0101 --------------------------- 3 10011符号位和符号位下一位(11+00)相加进位bit=00,根据上述判定是正溢出,最左侧进位自然舍弃 3) -10 1 0110 + -7 1 1001 --------------------------- -17 10 1111符号位和符号位下一位(10+11)相加进位bit=10,根据上述判定是负溢出 4) 14 0 1110 + -7 1 1001 --------------------------- 7 00 0111符号位和符号位下一位(01+11)相加进位bit=01,根据上述判定是正溢出,高位补零 |

【本文地址】

今日新闻 |

点击排行 |

|

推荐新闻 |

图片新闻 |

|

专题文章 |

wire [3:0] a=4’b1111; wire [3:0] b=4’b0010; wire [2:0] c;

wire [3:0] a=4’b1111; wire [3:0] b=4’b0010; wire [2:0] c;

结果正确。

结果正确。 可以看出是先赋值再移位的。

可以看出是先赋值再移位的。 结果正确,左边补0。

结果正确,左边补0。

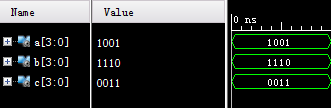

2.赋给位宽不够的数

2.赋给位宽不够的数

也是舍弃高位。

也是舍弃高位。

结果正确。

结果正确。

wire signed [3:0] a=4’b0111;//7 wire signed [3:0] b=4’b0010;//2 wire signed [3:0] c;

wire signed [3:0] a=4’b0111;//7 wire signed [3:0] b=4’b0010;//2 wire signed [3:0] c;

wire signed [3:0] a=4’b1001; wire signed [3:0] b=4’b1110; wire [3:0] c,d;

wire signed [3:0] a=4’b1001; wire signed [3:0] b=4’b1110; wire [3:0] c,d;

还是把c当做无符号数移位。

还是把c当做无符号数移位。 3.有符号数加法溢出判定 溢出定义: 对一个N位二进制补码,其可以表达的范围是 - 2N-1+1 ~ 2N+1 - 1之间。如果超出这个范围就称为溢出了。 如何判定是否溢出: 1)先把加前的数据转化成对应补码形式 2)各自最高两位相加,看两位进位组合

3.有符号数加法溢出判定 溢出定义: 对一个N位二进制补码,其可以表达的范围是 - 2N-1+1 ~ 2N+1 - 1之间。如果超出这个范围就称为溢出了。 如何判定是否溢出: 1)先把加前的数据转化成对应补码形式 2)各自最高两位相加,看两位进位组合