使用ModelSim软件进行时序仿真 |

您所在的位置:网站首页 › 时序仿真软件 › 使用ModelSim软件进行时序仿真 |

使用ModelSim软件进行时序仿真

|

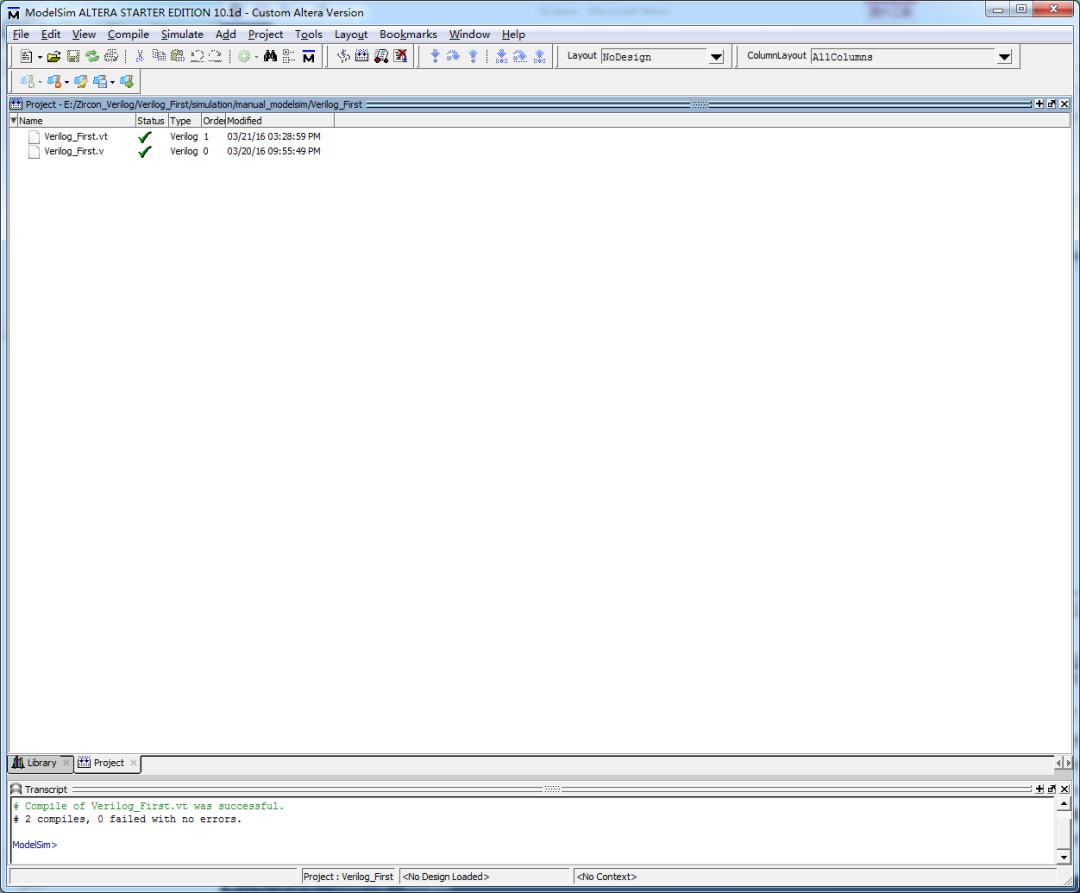

时序仿真与功能仿真的步骤大体相同,只不过中间需要添加仿真库、网表(.vo)文件和延时(.sdo)文件。到了这里,问题来了,仿真库、网表(.vo)文件和延时(.sdo)文件怎么获得呢?网表(.vo)文件和延时(.sdo)文件,其实我们在自动仿真的配置仿真功能中已经生成了,当我们配置好仿真功能之后,我们在 Quartus 进行一次全编译,这时,我们打开 Quartus 工程目录下 simulation/modelsim 中就能够看到 Verilog_First.vo 和 Verilog_First_v.sdo 这两个文件。我们将这两个文件复制到我们的 manual_modelsim 文件夹下。仿真库,我们需要到我们 Altera的安装目录下,也就是 C:altera13.1modelsim_asealteraverilog 中找到 cycloneive 文件夹,然后我们将 cycloneive 文件夹也复制到我们的 manual_modelsim 文件夹下。万事具备,接下来我们就可以打开我们的 ModelSim 软件,如图

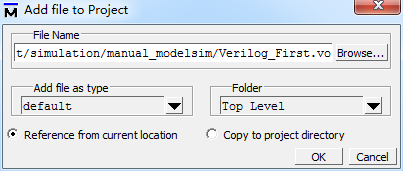

通过该图,我们可以看出,这个工程是我们之前做功能仿真的工程,当我们关闭 ModelSim之后,我们再次打开 ModelSim 这个软件,它会自动记录上一个我们使用的工程并打开。我们就直接在这个工程上进行更改,首先我们右键在弹出的菜单栏中找到【Add to Project】→【Existing File...】按钮并点击打开,则弹出图

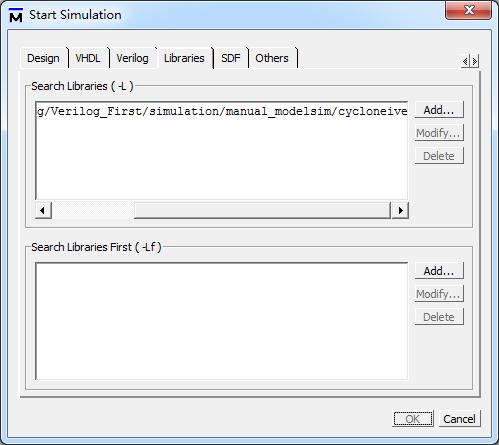

在该对话框中我们点击【Browse】,在弹出的对话框中我们找到 manual_modelsim 文件夹下的 Verilog_First.vo,然后将 Verilog_First.vo 添加至我们的 ModelSim 仿真工程中。接下来我们进行代码全编译,编译完成后,我们在 ModelSim 的菜单栏中找到【Simulate】→【StartSimulation...】按钮并点击打开,我们打开 Libraries 标签,将仿真库添加至配置仿真环境中,如图

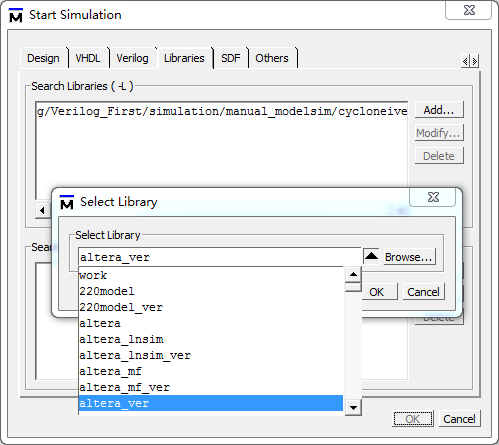

这里我们需要注意的是,只添加一个 cycloneive 仿真库是不够的,我们还需要将我们ModeSim 仿真库中的 altera_ver 库添加进来,如图

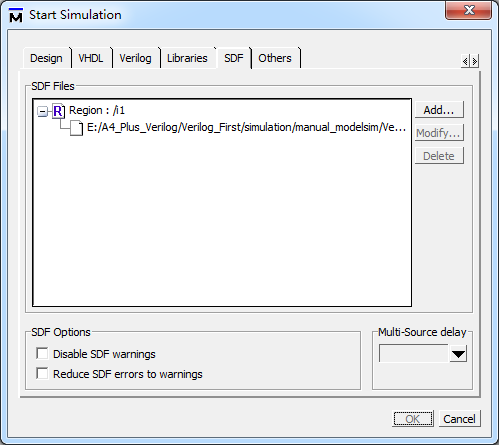

如果不知道需要选择哪个库,我们可以先直接运行仿真,这时候 ModelSim 控制窗口中会提示错误信息,我们根据错误信息便能够分析出我们需要的库名,然后我们再重复上述步骤添加完了仿真库,接下来我们在 SDF 标签页面中添加 Verilog_First_v.sdo 文件,如图

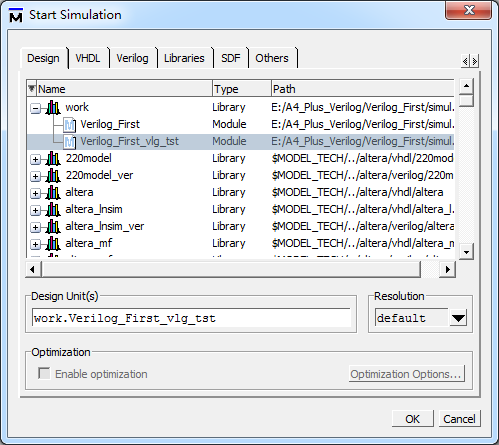

这里需要我们注意的是,因为的我们的实例化名是 i1,所以我们填写的是/i1。添加完成之后,最后我们在返回 Design 标签页面中,找到 work 下的 Verilog_First_vlg_tst,如图

在该页面中,我们点击【OK】就可以开始进行时序仿真了,到了这里,后面的工作就和我们的功能仿真是一样的了。至此,我们 ModelSim 软件的使用就讲解完了。 审核编辑:汤梓红 声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉 ModelSim ModelSim +关注关注 5文章 172浏览量 46919 时序仿真 时序仿真 +关注关注 0文章 14浏览量 7381原文标题:ModelSim 使用【六】modelsim手动时序仿真 文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。 收藏 人收藏扫一扫,分享给好友 复制链接分享 评论发布评论请先 登录 相关推荐 Modelsim SE 进行时序仿真及altera库的添加 [转] 为什么这样做就不是很了解了。经过昨天一天的努力,现在基本上明白了整个过程。对这篇文章进行整体的完善和补充(本人水平有限,如有错误请留言指正)。 用Modelsim对Quartus II工程进行时序 发表于 02-01 11:37 modelsim时序仿真总是出错为什么 在使用quartusii modelsim仿真时。。功能仿真可以好用,。但是时序仿真就出错。。无论是手动打开 发表于 11-26 21:06 modelsim-altera时序仿真 各位大神,求教如何用modelsim-ase 进行时序仿真,小弟最近被这整得焦头烂额{:4:}{:4:}。希望大家不吝赐教,最好附上详细教程。不过注意,不是modelsim SE哦。小 发表于 01-22 15:18 使用ModelSim进行设计仿真 ModelSim为HDL仿真工具,我们可以利用该软件来实现对所设计的VHDL或Verilog程序进行仿真,支持IEEE常见的各种硬件描述语言 发表于 04-19 20:52 •151次下载 使用 ModelSim 进行设计仿真 ModelSim为HDL仿真工具,我们可以利用该软件来实现对所设计的VHDL或Verilog程序进行仿真,支持IEEE常见的各种硬件描述语言 发表于 05-27 16:41 •132次下载 Modelsim的功能仿真和时序仿真

用ModelSim 进行功能仿真,进行功能仿真首先要检查设计的语法是否正确;其次检查代码是否达到设计的功能要求。下文主要介绍

发表于 11-13 15:35

•8802次阅读

使用 ModelSim 进行设计仿真详解

本章为ModelSim的初级教程,读者读完本章可以较为熟练的使用ModelSim进行设计仿真,本章没有也不可能涉及ModelSim的各个方面

发表于 12-24 18:29

•0次下载

modelsim仿真详细过程(功能仿真与时序仿真)

modelsim仿真详细过程(功能仿真与时序仿真).ModelSim不仅可以用于数字电路系统设计

发表于 12-19 11:14

•6.6w次阅读

Modelsim的功能仿真和时序仿真

用ModelSim 进行功能仿真,进行功能仿真首先要检查设计的语法是否正确;其次检查代码是否达到设计的功能要求。下文主要介绍

发表于 11-13 15:35

•8802次阅读

使用 ModelSim 进行设计仿真详解

本章为ModelSim的初级教程,读者读完本章可以较为熟练的使用ModelSim进行设计仿真,本章没有也不可能涉及ModelSim的各个方面

发表于 12-24 18:29

•0次下载

modelsim仿真详细过程(功能仿真与时序仿真)

modelsim仿真详细过程(功能仿真与时序仿真).ModelSim不仅可以用于数字电路系统设计

发表于 12-19 11:14

•6.6w次阅读

仿真软件ModelSim及其应用,ModelSim的仿真流程

ModelSim不仅可以用于数字电路系统设计的功能仿真,还可以应用于数字电路系统设计的时序仿真。 ModelSim的使用中,最基本的步骤包括

仿真软件ModelSim及其应用,ModelSim的仿真流程

ModelSim不仅可以用于数字电路系统设计的功能仿真,还可以应用于数字电路系统设计的时序仿真。 ModelSim的使用中,最基本的步骤包括

基于ModelSim使用modelsim手动时序仿真教程

时序仿真与功能仿真的步骤大体相同,只不过中间需要添加仿真库、网表(.vo)文件和延时(.sdo)文件。到了这里,问题来了,仿真库、网表(.v

基于ModelSim使用modelsim手动时序仿真教程

时序仿真与功能仿真的步骤大体相同,只不过中间需要添加仿真库、网表(.vo)文件和延时(.sdo)文件。到了这里,问题来了,仿真库、网表(.v

如何使用 ModelSim 进行设计仿真

ModelSim为HDL仿真工具,我们可以利用该软件来实现对所设计的VHDL或Verilog程 序进行仿真,支持IEEE常见的各种硬件描述语

发表于 01-14 09:47

•0次下载

如何使用 ModelSim 进行设计仿真

ModelSim为HDL仿真工具,我们可以利用该软件来实现对所设计的VHDL或Verilog程 序进行仿真,支持IEEE常见的各种硬件描述语

发表于 01-14 09:47

•0次下载

|

【本文地址】

今日新闻 |

点击排行 |

|

推荐新闻 |

图片新闻 |

|

专题文章 |