【乌拉喵.教程】编写TestBench,quartus与modelsim时序仿真 |

您所在的位置:网站首页 › 时序仿真的作用 › 【乌拉喵.教程】编写TestBench,quartus与modelsim时序仿真 |

【乌拉喵.教程】编写TestBench,quartus与modelsim时序仿真

|

最近将多年来收集到的教学视频、国内外图书、源码等整理整合拿出来,涉及arm、Linux、python、信号完整性、FPGA、DSP、算法、stm32、单片机、制图、电子模块、kali、出版社图书等。资料目前约1.5TB+。详情请见: https://www.bilibili.com/read/cv20701606昨天搜了一圈,也没整会这个仿真,今天在武梦梦的指导下修改了testbench,偶然一个操作,才成功。 下面详细的说说这个过程。 假设现在已经写好了一个电路vhdl,编译也没问题了,什么都没问题了,就差仿真了。 设置testbench语言

这里使用Verilog语言,因为从网上看的,说VHDL的testbench比较难,所以这里就用Verilog吧,确认。 生成testbench

点击之后,quartus会自动生成以.vt为扩展名的testbench文件。 添加testbench文件到工程中

找到button.vt添加工程中,现在testbench就是这个.vt文件了。 编译工程调用modelsim仿真

接下来就进入modelsim仿真界面了。 编辑button.vt testbench文件

Modelsim会弹出一个界面打开button.vt界面,可以看一下

下面就要修改这个文件 首先把注释什么的删了,干干净净的就这些东西

也就这么几块。首先要把 timescale改了,后面两个数据 /前的是仿真的时间单位 /后的是精度 我们把时间单位改成 1ns 精度改为1ps 其次,initial中的代码执行一次,always中的代码会一直执行。 为了演示方便,现在我们就只生成一个clk波形。那么我们在intial中为clk赋值(必须要赋初值),在always中对clk进行翻转。这样就可以形成一个clk了。

代码写成这样之后,我们保存,关闭即可。 编译testbench

如果modelsim没有报错,那么说明上面testbench的代码没有问题 加载测试文件

通过这样,就加载了测试文件 添加pin

在弹出的串口中 ctrl+A,选中所有的pin,有的不一定是监控的端口,有的是中间量,我不知道这个怎么叫,按照逻辑分析的意思,这个东西就是pin

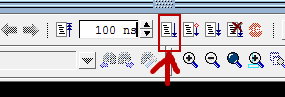

注意:在objects窗口中添加的pin才是最终的有效的,以前我从别的窗口添加pins,到调试的时候总是不出来波形,只有从object窗口添加的才是正确的! 点击Add wave命令后,就会打开另一个窗口,这个窗口就是最终的调试窗口了。 调试先修改整体的调试时间,将100ps改为100ns 即将 改为 之后点击run就行了……

多点几次run,之后将图像缩小,就能看到clk的出现了

|

【本文地址】

今日新闻 |

点击排行 |

|

推荐新闻 |

图片新闻 |

|

专题文章 |