FPGA配置OV5640摄像头及RGB图像数据采集 |

您所在的位置:网站首页 › 摄像头像素720p › FPGA配置OV5640摄像头及RGB图像数据采集 |

FPGA配置OV5640摄像头及RGB图像数据采集

|

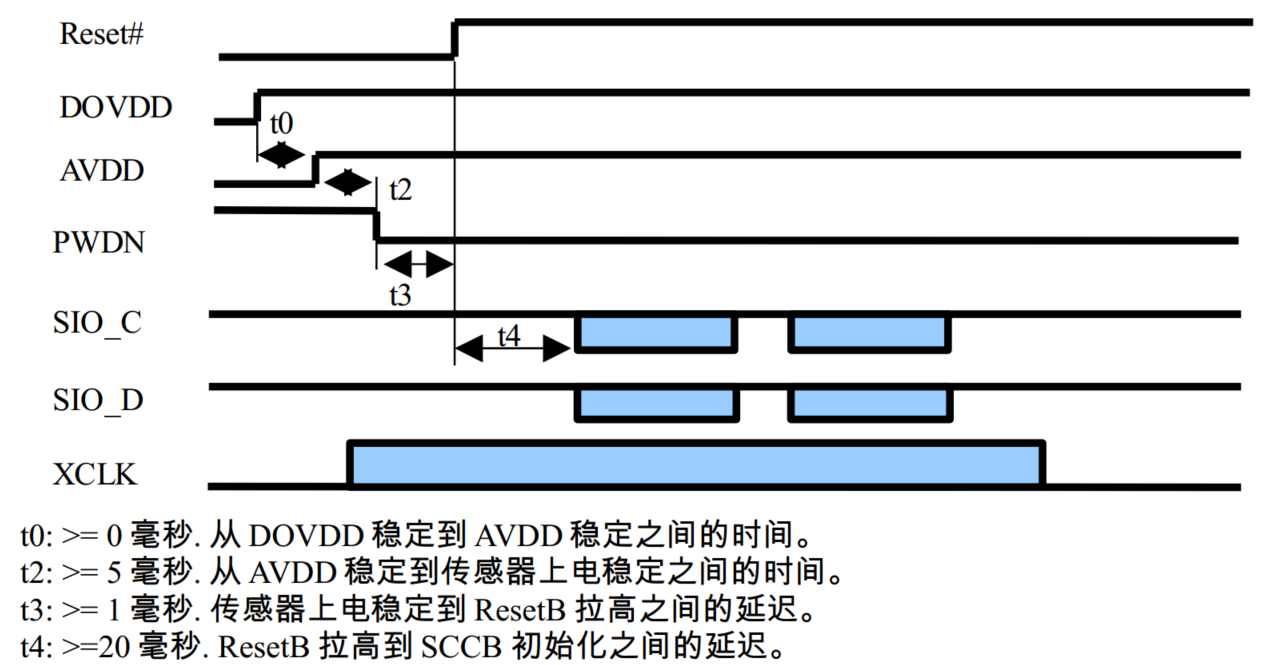

本文设计思想采用明德扬至简设计法。在做摄像头数据采集处理之前,需要配置OV5640传感器内部寄存器使其按要求正常工作,详细内容请参见《OV5640自动对焦照相模组应用指南》。首先要关注OV5640的上电时序:

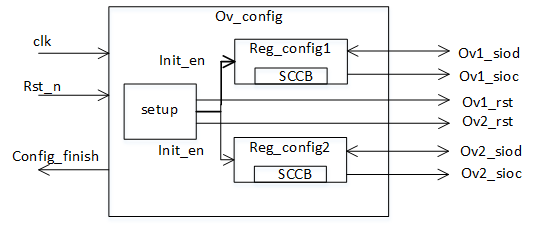

主控制器控制RESET PWDN两个信号按上电时序要求变化,之后允许ov_config模块配置内部寄存器。这里始终将PWDN拉低。实验中将摄像头分辨率设置为720p,即1280*720 ,帧率为30fps,图像输出格式是RGB565。此时摄像头输入时钟XCLK频率24MHz,输出像素时钟PCLK为84MHz。由于实验使用的是OV5640双目摄像头模组,且XCLK由外部24MHz晶振给出,故ov_config模块整体结构及端口定义如下:

setup模块构造上电时序,两个reg_config分别配置一个OV5640摄像头。SCCB_interface子模块负责SCCB协议读写寄存器数据。由于OV5640摄像头内部寄存器地址为16位,因此写寄存器地址阶段分高低字节两次写入。datasheet中给出了OV5640的SCCB ID地址(写),故读ID地址为0X79。

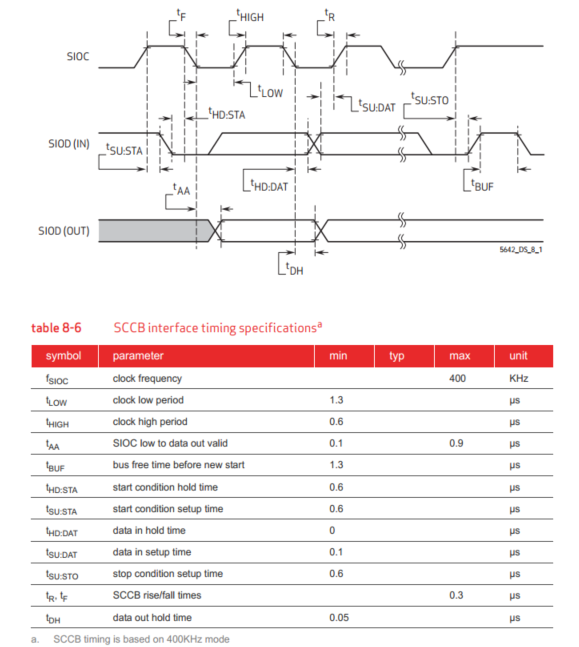

SCCB时序图及AC characteristics如下:

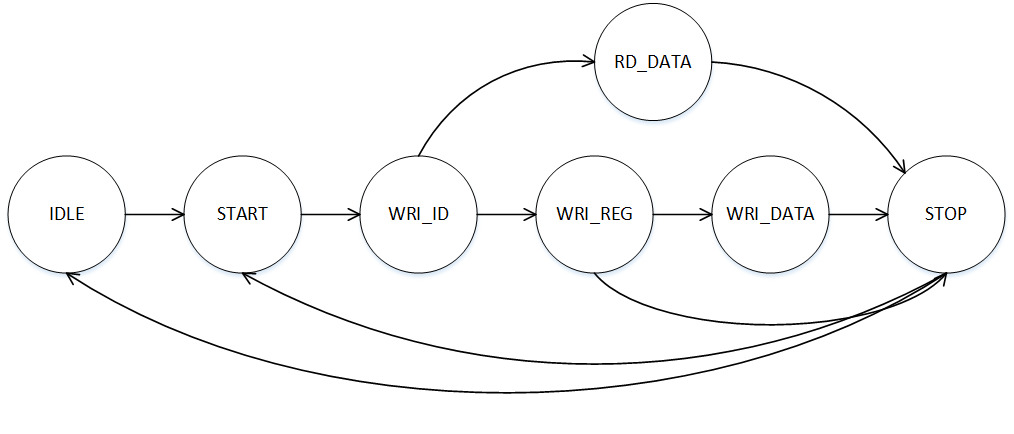

SCCB时钟SIOC支持最大频率为400KHz,一般选100KHz即可。以下是本人设计的SCCB接口读写时序状态机,写操作:IDLE START WRI_ID WRI_REG WRI_DATA STOP 对应三相写,读操作:IDLE START WRI_ID WRI_REG STOP START WRI_ID RD_DATA STOP对应两相写和两相读。

上代码: SCCB读写模块:   1 `timescale 1ns / 1ps

2

3

4 module sccb_interface(

5 input clk,

6 input rst_n,

7

8 input wr_en,

9 input rd_en,

10 input [8-1:0] id_addr,

11 input [16-1:0] reg_addr,

12 input [8-1:0] wr_data,

13 output reg [8-1:0] rd_data,

14 output reg rd_vld,

15 output rdy,

16

17 output reg sio_c,

18 output reg sio_out_en,

19 output reg sio_out,

20 input sio_in

21 );

22

23 parameter CYC = 500;

24

25

26 localparam IDLE = 0 ;

27 localparam START = 1 ;

28 localparam WRI_ID = 2 ;

29 localparam WRI_REG = 3 ;

30 localparam WRI_DATA = 4;

31 localparam RD_DATA = 5;

32 localparam STOP = 6 ;

33

34 //计数器

35 reg [ (9-1):0] div_cnt ;

36 wire add_div_cnt ;

37 wire end_div_cnt ;

38 reg [ (5-1):0] bit_cnt ;

39 wire add_bit_cnt ;

40 wire end_bit_cnt ;

41 reg [5-1:0] N;

42 (*DONT_TOUCH = "TRUE"*)reg [7-1:0] state_c,state_n;

43 wire idle2start,start2wri_id,wri_id2wri_reg,wri_id2rd_data, wri_reg2wri_data,wri_reg2stop,wri_data2stop,rd_data2stop,stop2start,stop2idle;

44 wire [18-1:0] regaddr;

45 reg [16-1:0] reg_addr_tmp;

46 reg [8-1:0] wr_data_tmp;

47 wire [9-1:0] idaddr_nc;

48 reg [8-1:0] id_addr_tmp;

49 reg rd_oper,rd_flag;

50 wire [9-1:0] wdata_nc;

51 wire [8-1:0] id_rwCtrl;

52

53

54 assign rdy = state_c == IDLE && !wr_en && !rd_en;

55

56 always @(posedge clk or negedge rst_n) begin

57 if (rst_n==0) begin

58 div_cnt

362 226:op_reg_data= {RW_CTRL, 24'h380bd0}; // DVPVO (720)->

363 227:op_reg_data= {RW_CTRL, 24'h380c07}; // HTS

364 228:op_reg_data= {RW_CTRL, 24'h380d64}; // HTS

365 229:op_reg_data= {RW_CTRL, 24'h380e02}; // VTS

366 230:op_reg_data= {RW_CTRL, 24'h380fe4}; // VTS

367 231:op_reg_data= {RW_CTRL, 24'h381304}; // timing V offset

368 232:op_reg_data= {RW_CTRL, 24'h361800};

369 233:op_reg_data= {RW_CTRL, 24'h361229};

370 234:op_reg_data= {RW_CTRL, 24'h370952};

371 235:op_reg_data= {RW_CTRL, 24'h370c03};

372 236:op_reg_data= {RW_CTRL, 24'h3a0202}; // 60Hz max exposure

373 237:op_reg_data= {RW_CTRL, 24'h3a03e0}; // 60Hz max exposure

374 238:op_reg_data= {RW_CTRL, 24'h3a0800}; // B50 step

375 239:op_reg_data= {RW_CTRL, 24'h3a096f}; // B50 step

376 240:op_reg_data= {RW_CTRL, 24'h3a0a00}; // B60 step

377 241:op_reg_data= {RW_CTRL, 24'h3a0b5c}; // B60 step

378 242:op_reg_data= {RW_CTRL, 24'h3a0e06}; // 50Hz max band

379 243:op_reg_data= {RW_CTRL, 24'h3a0d08}; // 60Hz max band

380 244:op_reg_data= {RW_CTRL, 24'h3a1402}; // 50Hz max exposure

381 245:op_reg_data= {RW_CTRL, 24'h3a15e0}; // 50Hz max exposure

382 246:op_reg_data= {RW_CTRL, 24'h400402}; // BLC line number

383 247:op_reg_data= {RW_CTRL, 24'h30021c}; // reset JFIFO, SFIFO, JPG

384 248:op_reg_data= {RW_CTRL, 24'h3006c3}; // disable clock of JPEG2x, JPEG

385 249:op_reg_data= {RW_CTRL, 24'h471303}; // JPEG mode 3

386 250:op_reg_data= {RW_CTRL, 24'h440704}; // Quantization sacle

387 251:op_reg_data= {RW_CTRL, 24'h460b37};

388 252:op_reg_data= {RW_CTRL, 24'h460c20};

389 253:op_reg_data= {RW_CTRL, 24'h483716}; // MIPI global timing

390 254:op_reg_data= {RW_CTRL, 24'h382404}; // PCLK manual divider

391 255:op_reg_data= {RW_CTRL, 24'h5001a3}; // SDE on, CMX on, AWB on, scale on

392 256:op_reg_data= {RW_CTRL, 24'h350300}; // AEC/AGC on

393 257:op_reg_data= {RW_CTRL, 24'h301602}; //Strobe output enable

394 258:op_reg_data= {RW_CTRL, 24'h3b070a}; //FREX strobe mode1

395 //strobe flash and frame exposure

396 259:op_reg_data={RW_CTRL, 24'h3b0083}; //STROBE CTRL: strobe request ON, Strobe mode: LED3

397 260:op_reg_data={RW_CTRL, 24'h3b0000}; //STROBE CTRL: strobe request OFF

398

399 default:op_reg_data={RW_CTRL, 24'h000000};

400 endcase

401 end

402

403

404 endmodule

reg_config

1 `timescale 1ns / 1ps

2

3

4 module sccb_interface(

5 input clk,

6 input rst_n,

7

8 input wr_en,

9 input rd_en,

10 input [8-1:0] id_addr,

11 input [16-1:0] reg_addr,

12 input [8-1:0] wr_data,

13 output reg [8-1:0] rd_data,

14 output reg rd_vld,

15 output rdy,

16

17 output reg sio_c,

18 output reg sio_out_en,

19 output reg sio_out,

20 input sio_in

21 );

22

23 parameter CYC = 500;

24

25

26 localparam IDLE = 0 ;

27 localparam START = 1 ;

28 localparam WRI_ID = 2 ;

29 localparam WRI_REG = 3 ;

30 localparam WRI_DATA = 4;

31 localparam RD_DATA = 5;

32 localparam STOP = 6 ;

33

34 //计数器

35 reg [ (9-1):0] div_cnt ;

36 wire add_div_cnt ;

37 wire end_div_cnt ;

38 reg [ (5-1):0] bit_cnt ;

39 wire add_bit_cnt ;

40 wire end_bit_cnt ;

41 reg [5-1:0] N;

42 (*DONT_TOUCH = "TRUE"*)reg [7-1:0] state_c,state_n;

43 wire idle2start,start2wri_id,wri_id2wri_reg,wri_id2rd_data, wri_reg2wri_data,wri_reg2stop,wri_data2stop,rd_data2stop,stop2start,stop2idle;

44 wire [18-1:0] regaddr;

45 reg [16-1:0] reg_addr_tmp;

46 reg [8-1:0] wr_data_tmp;

47 wire [9-1:0] idaddr_nc;

48 reg [8-1:0] id_addr_tmp;

49 reg rd_oper,rd_flag;

50 wire [9-1:0] wdata_nc;

51 wire [8-1:0] id_rwCtrl;

52

53

54 assign rdy = state_c == IDLE && !wr_en && !rd_en;

55

56 always @(posedge clk or negedge rst_n) begin

57 if (rst_n==0) begin

58 div_cnt

362 226:op_reg_data= {RW_CTRL, 24'h380bd0}; // DVPVO (720)->

363 227:op_reg_data= {RW_CTRL, 24'h380c07}; // HTS

364 228:op_reg_data= {RW_CTRL, 24'h380d64}; // HTS

365 229:op_reg_data= {RW_CTRL, 24'h380e02}; // VTS

366 230:op_reg_data= {RW_CTRL, 24'h380fe4}; // VTS

367 231:op_reg_data= {RW_CTRL, 24'h381304}; // timing V offset

368 232:op_reg_data= {RW_CTRL, 24'h361800};

369 233:op_reg_data= {RW_CTRL, 24'h361229};

370 234:op_reg_data= {RW_CTRL, 24'h370952};

371 235:op_reg_data= {RW_CTRL, 24'h370c03};

372 236:op_reg_data= {RW_CTRL, 24'h3a0202}; // 60Hz max exposure

373 237:op_reg_data= {RW_CTRL, 24'h3a03e0}; // 60Hz max exposure

374 238:op_reg_data= {RW_CTRL, 24'h3a0800}; // B50 step

375 239:op_reg_data= {RW_CTRL, 24'h3a096f}; // B50 step

376 240:op_reg_data= {RW_CTRL, 24'h3a0a00}; // B60 step

377 241:op_reg_data= {RW_CTRL, 24'h3a0b5c}; // B60 step

378 242:op_reg_data= {RW_CTRL, 24'h3a0e06}; // 50Hz max band

379 243:op_reg_data= {RW_CTRL, 24'h3a0d08}; // 60Hz max band

380 244:op_reg_data= {RW_CTRL, 24'h3a1402}; // 50Hz max exposure

381 245:op_reg_data= {RW_CTRL, 24'h3a15e0}; // 50Hz max exposure

382 246:op_reg_data= {RW_CTRL, 24'h400402}; // BLC line number

383 247:op_reg_data= {RW_CTRL, 24'h30021c}; // reset JFIFO, SFIFO, JPG

384 248:op_reg_data= {RW_CTRL, 24'h3006c3}; // disable clock of JPEG2x, JPEG

385 249:op_reg_data= {RW_CTRL, 24'h471303}; // JPEG mode 3

386 250:op_reg_data= {RW_CTRL, 24'h440704}; // Quantization sacle

387 251:op_reg_data= {RW_CTRL, 24'h460b37};

388 252:op_reg_data= {RW_CTRL, 24'h460c20};

389 253:op_reg_data= {RW_CTRL, 24'h483716}; // MIPI global timing

390 254:op_reg_data= {RW_CTRL, 24'h382404}; // PCLK manual divider

391 255:op_reg_data= {RW_CTRL, 24'h5001a3}; // SDE on, CMX on, AWB on, scale on

392 256:op_reg_data= {RW_CTRL, 24'h350300}; // AEC/AGC on

393 257:op_reg_data= {RW_CTRL, 24'h301602}; //Strobe output enable

394 258:op_reg_data= {RW_CTRL, 24'h3b070a}; //FREX strobe mode1

395 //strobe flash and frame exposure

396 259:op_reg_data={RW_CTRL, 24'h3b0083}; //STROBE CTRL: strobe request ON, Strobe mode: LED3

397 260:op_reg_data={RW_CTRL, 24'h3b0000}; //STROBE CTRL: strobe request OFF

398

399 default:op_reg_data={RW_CTRL, 24'h000000};

400 endcase

401 end

402

403

404 endmodule

reg_config

上电时序模块:   1 `timescale 1ns / 1ps

2

3

4 module setup(

5 input clk,//50MHZ

6 input rst_n,

7 output reg init_en,

8

9 output reg ov_pwdn1,

10 output reg ov_rst_n1,

11 output reg ov_pwdn2,

12 output reg ov_rst_n2

13 );

14

15 parameter MS_CYC = 50_000;

16

17 reg [16-1:0] ms_cnt;

18 wire add_ms_cnt;

19 wire end_ms_cnt;

20 reg [ (5-1):0] wait_cnt ;

21 wire add_wait_cnt ;

22 wire end_wait_cnt ;

23 reg [5-1:0] N;

24 reg [ (2-1):0] phase_cnt ;

25 wire add_phase_cnt ;

26 wire end_phase_cnt ;

27 reg setup_done;

28

29

30 //ms计数

31 always @(posedge clk or negedge rst_n)begin

32 if(!rst_n)begin

33 ms_cnt

1 `timescale 1ns / 1ps

2

3

4 module setup(

5 input clk,//50MHZ

6 input rst_n,

7 output reg init_en,

8

9 output reg ov_pwdn1,

10 output reg ov_rst_n1,

11 output reg ov_pwdn2,

12 output reg ov_rst_n2

13 );

14

15 parameter MS_CYC = 50_000;

16

17 reg [16-1:0] ms_cnt;

18 wire add_ms_cnt;

19 wire end_ms_cnt;

20 reg [ (5-1):0] wait_cnt ;

21 wire add_wait_cnt ;

22 wire end_wait_cnt ;

23 reg [5-1:0] N;

24 reg [ (2-1):0] phase_cnt ;

25 wire add_phase_cnt ;

26 wire end_phase_cnt ;

27 reg setup_done;

28

29

30 //ms计数

31 always @(posedge clk or negedge rst_n)begin

32 if(!rst_n)begin

33 ms_cnt |

【本文地址】

公司简介

联系我们

今日新闻 |

点击排行 |

|

推荐新闻 |

图片新闻 |

|

专题文章 |