timegen学习记录 |

您所在的位置:网站首页 › 如何画输出电压波形图片 › timegen学习记录 |

timegen学习记录

|

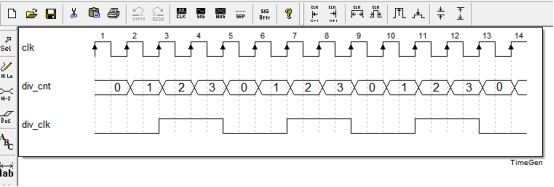

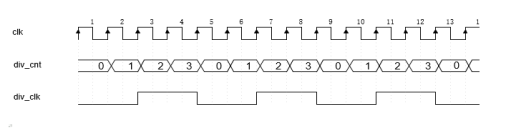

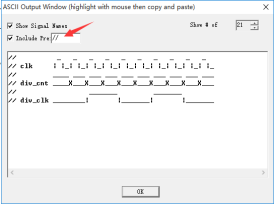

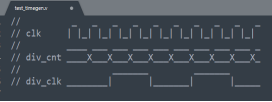

timegen学习记录-如何画图和导入Visio 最近重新从零开始学习FPGA,把基础打扎实。用visio画波形图,感觉这画波形图的效率不高、使用不够方便。自己是用过timegen软件,感觉画得比较快,方便时序对齐。但指导老师说,timegen画的图不方便导出到文档、不方便后期修改,交作业也都是用visio的格式。突然在csdn上看到有timegen波形图导出到visio里面修改的方法,于是转载,把方法整理一下。 画完之后去掉背景logo: (1)View-TimeGen Logo去掉勾(即去掉右下角的字符); View-Bounding Rectangle去掉勾(去掉四周黑色边框); (2)File-Export-Enhanced MetaFile(.emf),导出为.emf文件; 导入visio软件方便调整修改 (3)打开visio软件,打开该文件,选择*.emf TIME GEN 学习笔记【原创:翩若惊鸿】 1.TIME GEN可以做什么? TIME GEN是一个比较高效的波形绘制软件,可以用于绘画波形,在IC设计领域,硬件设计领域,集成电路领域使用的比较多。 以FPGA逻辑设计为例,编写源代码时,某个模块的功能构建通常需要FSM实现特定的时序控制、流程控制。而FSM有效的设计方法是,使用“状态图(visio绘制)+时序图(TIME GEN绘制)”组合,快速定义模块功能,提高设计效率。 另外,很多模块之间的接口信号的时序关系,也可以通过TIME GEN 绘制。 TIME GEN不仅可以将绘制波形以图片的方式保存下来,还可以以ASCII码的格式复制到源代码文件中,作为注释跟随设计文件存在。 File-Export-show ascii waveforms,然后复制,到verilog、vhdl等设计文件中粘贴即可; 2.以一个简单FSM设计为例 1)功能: 前端缓存FIFO(first word first through模式,W8xD256)写满16个数据,prog_empty信号拉低,FSM触发缓存FIFO读动作,将数据按照帧格式解析( 示例仅解析2个寄存器),送入后端逻辑; 2)FSM模块接口: module fr_unpack_fsm( input clk, input reset, input fifo_prog_empty, output fifo_rd_en, input [7:0] fifo_rd_data, output [7:0] reg_1, output [7:0] reg_2, output [5:0] state );3)状态图 3.使用TIME GEN绘制时序图 3.1双击启动TIME GEN 我使用的版本是TIEM GEN 3.2,界面如下图。 快捷工具条:选择;信号高低绘制1/信号高阻态绘制/信号高低绘制2;添加文本;添加标签1/添加标签2;增加曲线箭头/增加折线箭头/增加直线箭头/增加悬浮直线箭头;增加时间间断;增加波形无效区域/擦除波形无效区域;增加波形延时/减少波形延时 3.2 波形设计 1)添加时钟 添加时钟,选择工具栏CLK图标,点击一下时钟信号就出现了。 4)绘制信号波形 信号波形的绘制,主要使用快捷工具条:Hi Lo、Hi-z、Bus工具。 以reset信号为例,要将reset信号在clk第2个周期上升沿到来后下拉,可以点击Hi Lo图标,然后在reset信号波形上clk第2个周期上升沿后位置,开始拖动鼠标,即可获取如下波形。 5)添加时间间断 在复位完成后,fifo_prog_empty的下拉到来时刻是不确定的,因此需要用时间间断来表征这种不确定性。 单击工具条时间间断图标,选中该功能,在所有信号的时钟3周期单击,添加时间间断标识。 本设计中,fifo_prog_empty信号的下拉,触发了帧解析动作,因此单击工具条的曲线箭头图标,标注信号关联性。 8)标注波形无效区域 所谓波形无效区域,也可以理解为设计不关心的区域。标注此类区域,有助于界定设计用不需要处理的时序部分,和信号无效区域。 FPGA的设计,必须考虑信号输出延时带来的影响。TIME GEN可以很好地使用增加延时的工具来调整波形输出延时。 以fifo_prog_empty信号为例,要推迟该信号的延时,可以选择该信号的CLK-4时段,单击工具条DELAY图标,推迟fifo_prog_empty的下拉时刻。也可以直接在编辑模式下,将鼠标移动到该信号的下降沿,直接拖动下降沿向右移动。 可以选中时间标签,修改属性。 附上原文链接如下: 原文链接1: https://blog.csdn.net/tafengtianya/article/details/80184601 原作者:tafengtianya 来源:CSDN 原文链接2: http://blog.sina.com.cn/s/blog_75c020ef0102x1u2.html |

【本文地址】

今日新闻 |

点击排行 |

|

推荐新闻 |

图片新闻 |

|

专题文章 |

TimeGen官网下载链接:http://www.xfusionsoftware.com/download_timegen.html 链接:https://pan.baidu.com/s/1lauZhB8fOY21LJj3iYFWGg 提取码:1234

TimeGen官网下载链接:http://www.xfusionsoftware.com/download_timegen.html 链接:https://pan.baidu.com/s/1lauZhB8fOY21LJj3iYFWGg 提取码:1234 打开文件后,①可以右键点击图片-组合-取消组合,②也可以左键选中该图片,点击上方的组合-取消组合。取消组合后就可以随意删除了。

打开文件后,①可以右键点击图片-组合-取消组合,②也可以左键选中该图片,点击上方的组合-取消组合。取消组合后就可以随意删除了。  可以在visio中修改,并重新另存为.vsdx的格式。

可以在visio中修改,并重新另存为.vsdx的格式。  timegen的help FAQ链接:http://www.xfusionsoftware.com/timegenhowto.html

timegen的help FAQ链接:http://www.xfusionsoftware.com/timegenhowto.html

下节具体记录使用TIME GEN绘制时序图步骤。

下节具体记录使用TIME GEN绘制时序图步骤。 菜单栏:文件/编辑/视图/添加/模式/帮助 工具栏:新建/打开/保存;剪切/复制/打印;撤销/返回;时钟/信号/总线/分割;属性;ASCII;帮助;删除时钟周期;增加时钟周期;时钟周期延长;时钟周期缩短;增加信号高度;减小信号高度;减小信号行距;增加信号行距

菜单栏:文件/编辑/视图/添加/模式/帮助 工具栏:新建/打开/保存;剪切/复制/打印;撤销/返回;时钟/信号/总线/分割;属性;ASCII;帮助;删除时钟周期;增加时钟周期;时钟周期延长;时钟周期缩短;增加信号高度;减小信号高度;减小信号行距;增加信号行距 2)添加信号、总线 添加信号,选择工具栏SIG图标,点击一下信号就出现了。 同样,添加总线,选择工具栏BUS图标,点击一下总线信号也出现。 根据FSM设计要求,reset、fifo_prog_empty、fifo_rd_en是信号,fifo_rd_data 、reg_1、 reg_2、state则为总线信号。因此依次添加3个信号、4个总线信号。

2)添加信号、总线 添加信号,选择工具栏SIG图标,点击一下信号就出现了。 同样,添加总线,选择工具栏BUS图标,点击一下总线信号也出现。 根据FSM设计要求,reset、fifo_prog_empty、fifo_rd_en是信号,fifo_rd_data 、reg_1、 reg_2、state则为总线信号。因此依次添加3个信号、4个总线信号。  信号未修改属性前,均使用默认名称。 3)修改信号属性

信号未修改属性前,均使用默认名称。 3)修改信号属性  添加完信号后,工作模式保持在绘制模式,需要先将工作模式转换到编辑模式,才能进行信号属性修改。 点击菜单栏mode图标,选择edit模式。 然后,直接双击信号名称进行修改,也可选择信号后,点击工具栏SIG ATTR,进行修改。

添加完信号后,工作模式保持在绘制模式,需要先将工作模式转换到编辑模式,才能进行信号属性修改。 点击菜单栏mode图标,选择edit模式。 然后,直接双击信号名称进行修改,也可选择信号后,点击工具栏SIG ATTR,进行修改。 依此方法,设计信号波形。

依此方法,设计信号波形。 6)完成波形设计,并添加文字注释

6)完成波形设计,并添加文字注释  7)添加信号关联性注释

7)添加信号关联性注释 要修改箭头的属性,可以选中箭头后右击,修改,如下图,将箭头颜色改为红色。

要修改箭头的属性,可以选中箭头后右击,修改,如下图,将箭头颜色改为红色。 9)增加信号延时

9)增加信号延时 10)添加时间标签 为上一步中增加的时间延时,添加时间标签。选中工具条时间标签图标后,单击fifo_prog_empty在CLK-4时段的波形,放置到时间标签的起点,然后单击fifo_prog_empty下拉时刻波形,放置时间标签的终点,完成时间标签的添加。

10)添加时间标签 为上一步中增加的时间延时,添加时间标签。选中工具条时间标签图标后,单击fifo_prog_empty在CLK-4时段的波形,放置到时间标签的起点,然后单击fifo_prog_empty下拉时刻波形,放置时间标签的终点,完成时间标签的添加。 至此,使用TIME GEN设计FSM时序完成

至此,使用TIME GEN设计FSM时序完成