【学习笔记/PLL】锁相环PLL线性模型理论分析 |

您所在的位置:网站首页 › 低通滤波器传递函数推导 › 【学习笔记/PLL】锁相环PLL线性模型理论分析 |

【学习笔记/PLL】锁相环PLL线性模型理论分析

|

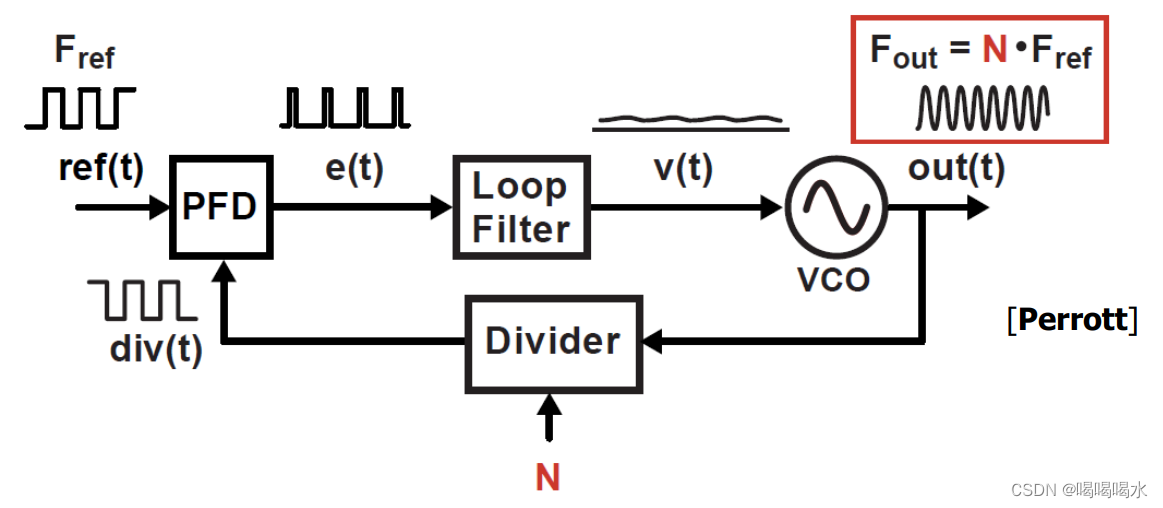

锁相(phase locking)的概念是20世纪30年代提出的,距今已经100年左右了,尽管工艺在持续发展,振荡器的频率也越来越快,各种花样锁相环结构的文章层出不穷,但是发展至今,基本的锁相环结构几乎保持原样。这对于初学者了解锁相环的基本原理是很友好的。本文参考了Razavi、Sam Palermo等学者的教材、文章,简略的总结了PLL线性模型下的噪声传递函数,欢迎各位同学批评指正。 目录 一、PLL功能及线性模型 二、PLL的噪声传递函数分析 2.1 PD(PFD+CP) 2.2 LPF 2.3 VCO 2.4 Divider 2.5 PLL的开环传递函数、环路增益、闭环传递函数 2.6 PLL各模块的噪声对PLL输出相位噪声的贡献 三、PLL环路稳定性分析 3.1 环路稳定性分析 3.2 PLL关键参数:环路带宽、阻尼系数、固有频率 一、PLL功能及线性模型下图是锁相环(Phase Locked Loop,PLL)的框图,PLL的输入为参考时钟信号,与反馈时钟信号一同输入到鉴相器(Phase Detector,PD)中进行相位比较,输出电压信号。如果反馈信号相位落后,输出电压升高,会控制压控振荡器(Voltage Controlled Oscillator,VCO)的输出频率增大,以“追赶”参考时钟的相位;反之,VCO震荡减慢,等待参考时钟相位“追上来”,最终使得参考时钟相位和反馈时钟相位对齐,PLL锁定。可以看出,PLL实际上是一个负反馈系统。

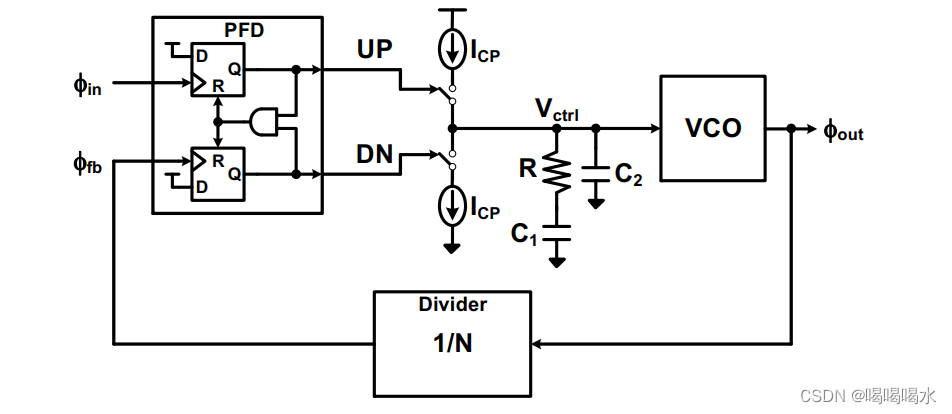

电荷泵锁相环(Charge-pump PLL)是目前更为常用的锁相环结构(如下图),鉴频鉴相器(phase and frequency detector,PFD)和电荷泵(CP)合并看作鉴相器PD,其输出的电流信号对环路滤波器充电/放电,控制电压升高/降低,从而控制VCO的振荡频率。

为了便于分析和建模,我们不考虑具体的电路结构,仅从信号与系统的角度进行分析。同时,为了简化计算,我们需要将整个PLL电路近似看作一个线性时不变系统,构造其线性模型,推导传递函数。 二、PLL的噪声传递函数分析我们把PLL分成几个子模块,分别是PD(PFD+CP)、环路滤波器(Loop Filter,LPF)、VCO和分频器Divider。首先推导各子模块的传递函数。 2.1 PD(PFD+CP)PD的输入是参考时钟和反馈时钟的相位差,输出是CP的电流Icp。实际上,PLL的锁定过程中,PD并不是一个连续的模型,CP的电流仅在有相位差的时间段内会打开,因此它是一个离散的信号。但是为了简化计算,我们构建PLL线性模型中,把PD看作一个连续输出电流信号的模块。为了保证这个结论近似成立,必须要有一定的条件约束。这个条件就是:PLL环路的响应要远小于参考时钟的频率,也就是说环路带宽要小于1/10~1/15的参考时钟频率。

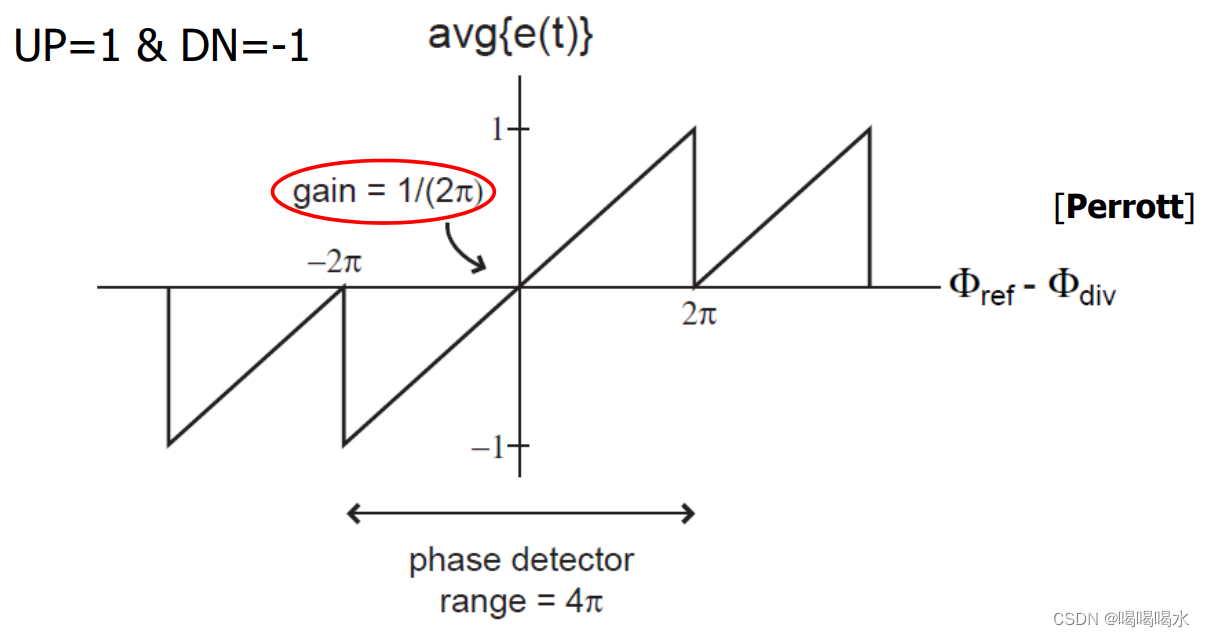

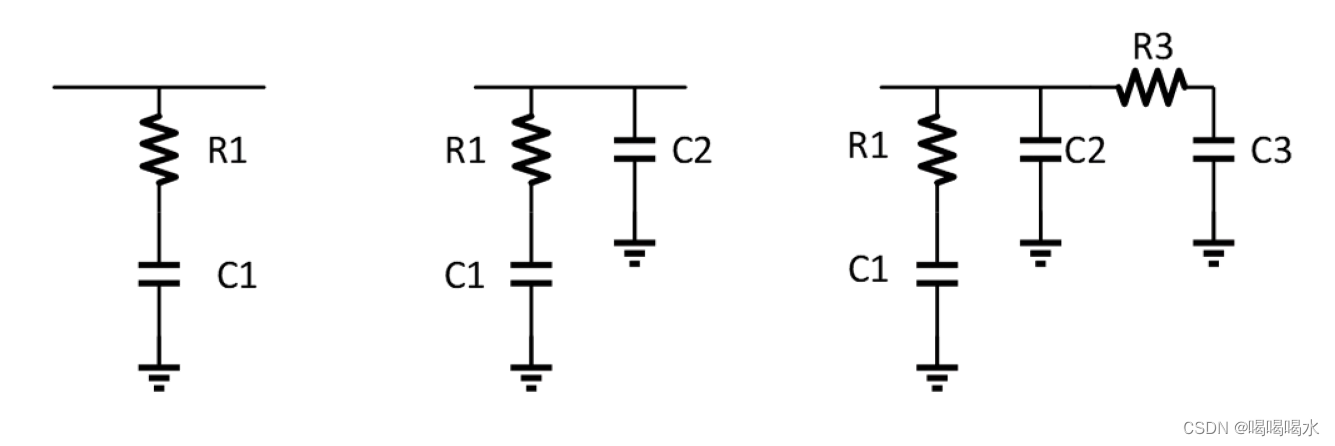

PD的函数图像如上图所示,在-2π~2π的区间内,都有相位差和Icp的线性关系,其斜率为 LPF是由电阻电容构成的,输入为CP的电流Icp,输出为控制VCO的电压Vctrl,传递函数Z(s)的推导比较容易。下图列出了一阶、二阶、三阶环路滤波器的电路图。

由上图可知,一阶环路滤波器的传递函数为: 二阶环路滤波器的传递函数为: 三阶环路滤波器的传递函数为:

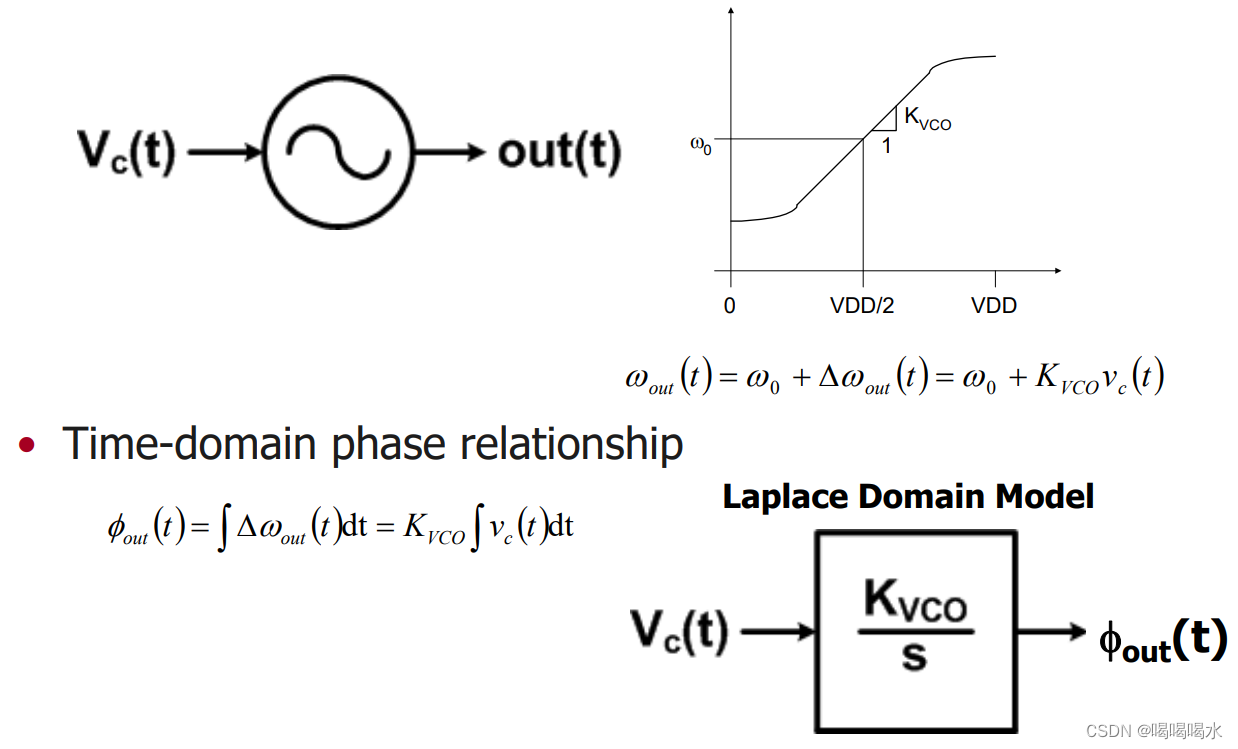

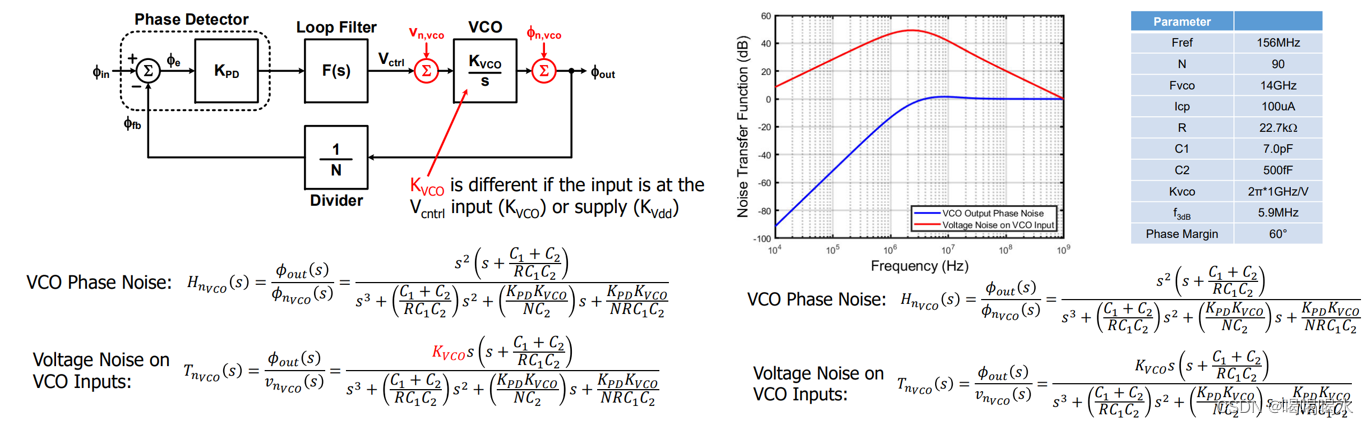

VCO是PLL的核心模块,主要分为Ring-VCO和LC-VCO两大类,有很多巧妙复杂的具体电路结构,但在PLL线性模型中,我们把它看成一个理想的积分器,其输出频率随输入电压线性变化,即: 其中斜率为Kvco。VCO的输入为LPF的输出电压Vctrl,输出为相位,上述公式两侧对时间进行积分(忽略 频率对时间的积分为相位,整理可得其传递函数为:

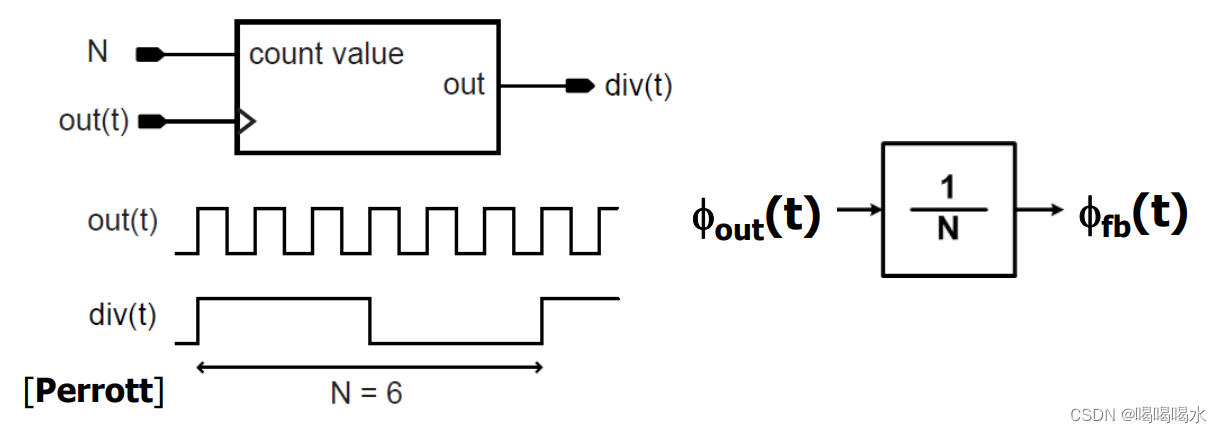

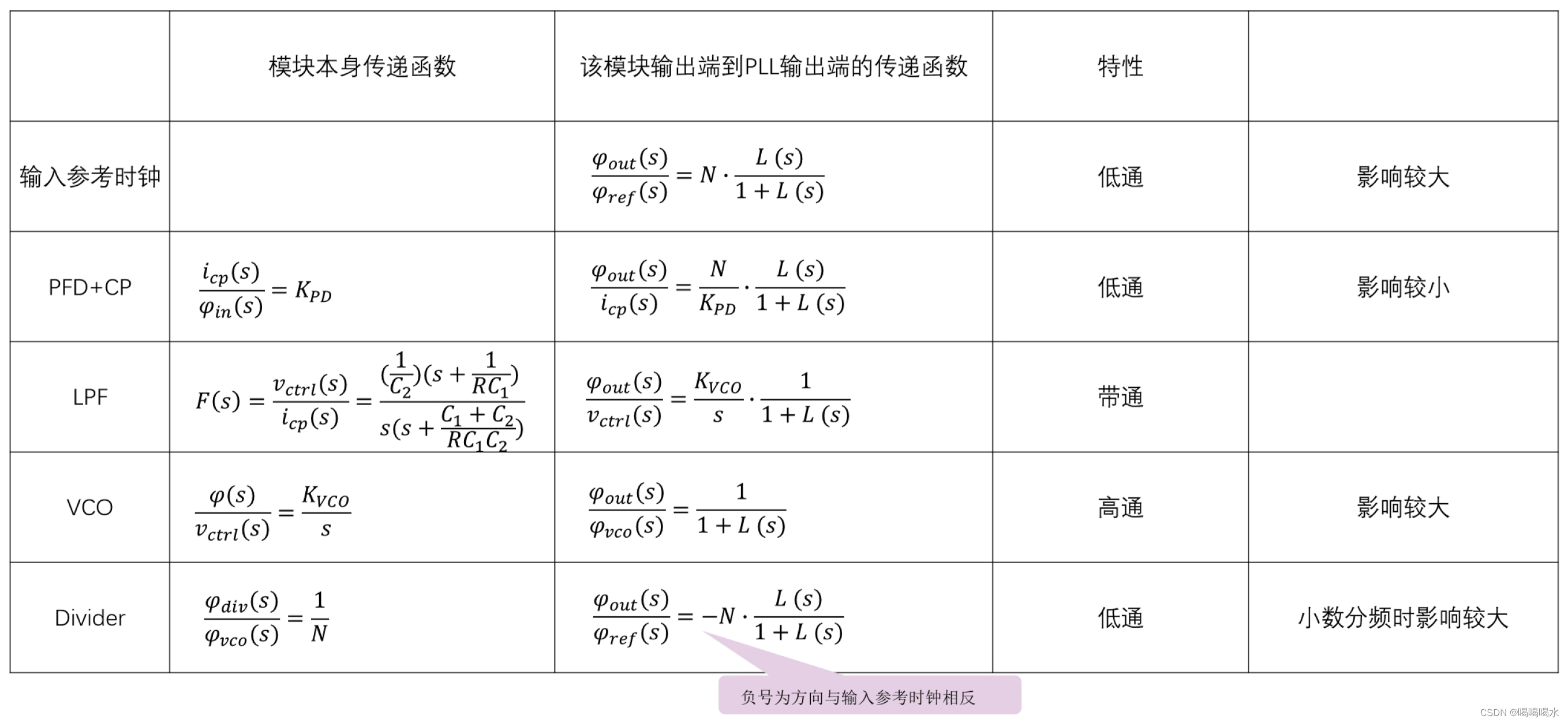

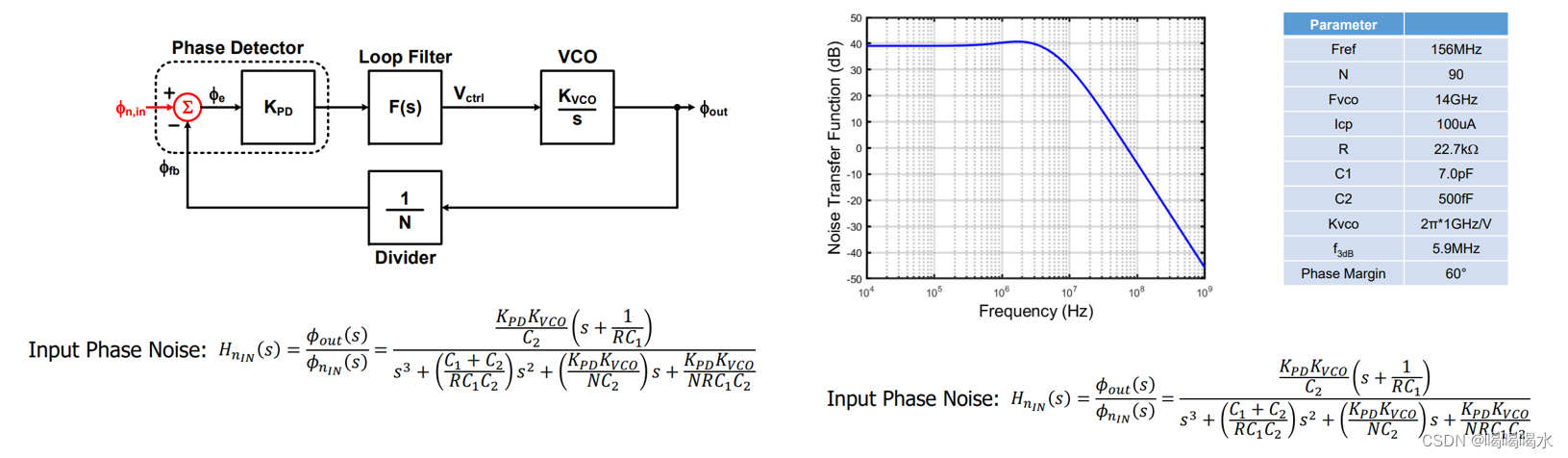

分频器的模型比较简单,其输入为VCO的输出相位,输出为反馈时钟相位,传递函数为 根据我们上述推导的PLL各模块的传递函数,我们可以很容易的写出PLL的开环传递函数、环路增益、闭环传递函数(LPF以二阶为例),分别是: 开环传递函数 环路增益 闭环传递函数 输入参考时钟的输出噪声为相位噪声;PD的输出噪声为CP的电流噪声;LPF的输出噪声为Vctrl上的电压噪声;VCO的输出噪声为相位噪声;Divider的输出噪声为相位噪声。各模块的输出噪声到PLL输出端的传递函数,即各模块的输出端到PLL输出端的开环增益,除以1加环路增益,各模块的传递函数及其噪声到PLL输出端的传递函数总结如下表:

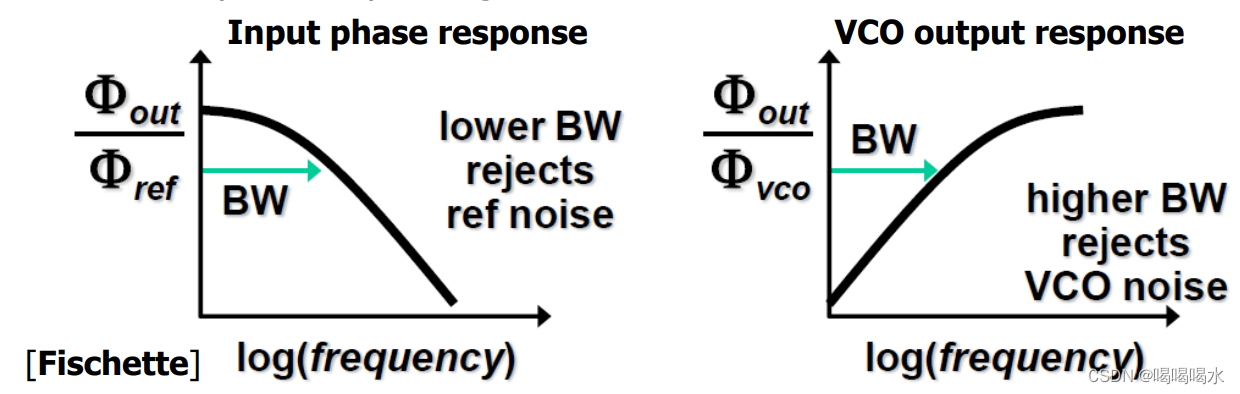

可以看出输入参考时钟、PD和Divider的噪声为低通特性,LPF的噪声为带通特性,VCO的噪声为高通特性。Sam Palermo教授的课件如下,也证明了这一结果。

值得注意的是,这里Sam Palermo为什么没有讨论PD的输出噪声对PLL的影响,我的理解是,因为在PLL锁定或者近似锁定的情况下,相位差占整个周期的比例很小,也就是说,每个周期内,只有很小比例的时间CP会开启并引入电流噪声,因此可以忽略。 对于不同模块引入的噪声,除了在设计上降低其本身的噪声外,也可以通过PLL系统参数的调整来抑制噪声,如下图所示。减小PLL的环路带宽,可以抑制低通的带内噪声,如输入参考时钟的噪声、CP的噪声和Divider的噪声;增大PLL的环路带宽,可以抑制高通的带外噪声,即VCO的噪声。当然,通过减小(增大)带宽,来抑制带内(带外)噪声,势必也会导致带外(带内)的噪声贡献增大。

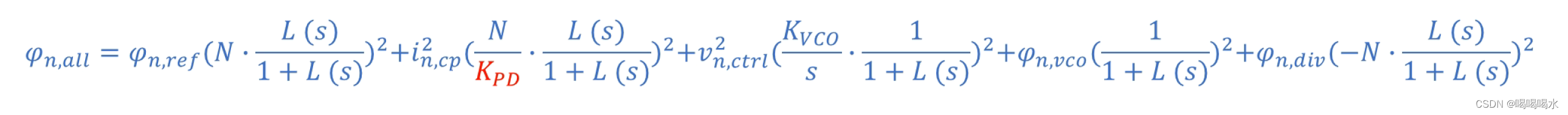

这里有一个重要的结论:PLL的相位噪声,等于各模块输出噪声乘以其到PLL输出端的传递函数的平方加和。如下:

这里有一个有意思的点,如果CP的电流噪声较大,应该如何优化呢?正常来说电流噪声与电流值成正比,因此减小Icp可以降低CP本身的电流噪声,但是可以看到,其到PLL输出端的传递函数中,Kpd在分母上,并且是平方关系,一约分的话,还有一个Icp在分母上,也就是说,尽管减小Icp降低了CP本身的电流噪声,但是却导致对PLL输出端的噪声贡献增大。正确的方法应该是增大Icp。当然,考虑到实际情况Icp打开的时间占比很短,这个噪声的贡献实际应该很小。 三、PLL环路稳定性分析 3.1 环路稳定性分析我们可以通过PLL零极点和波特图,对PLL的环路稳定性进行分析。

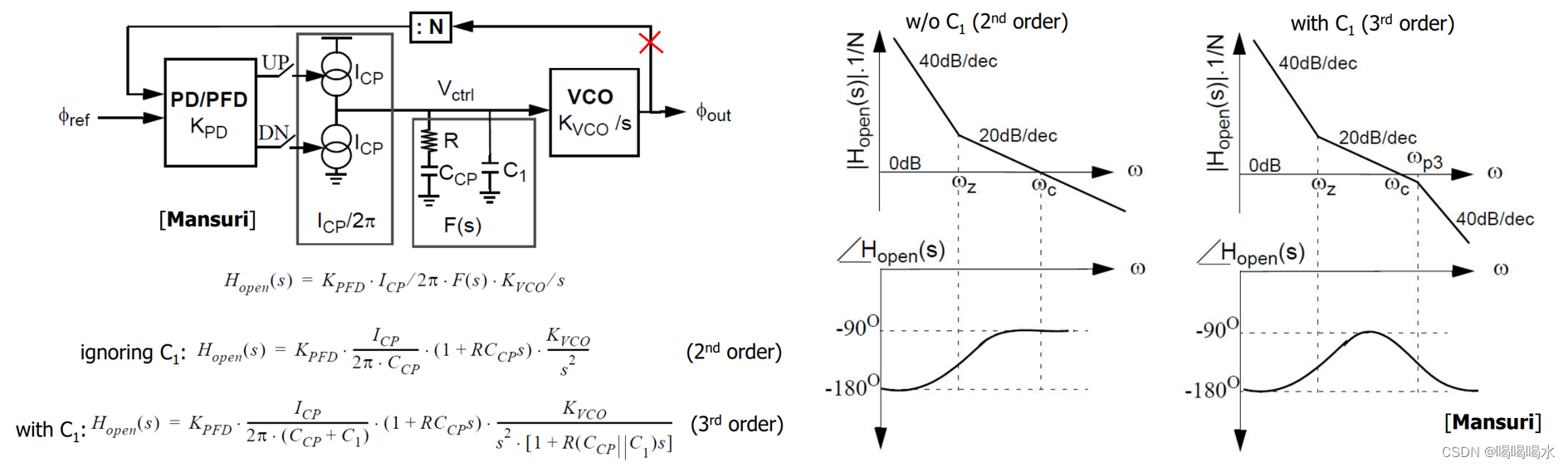

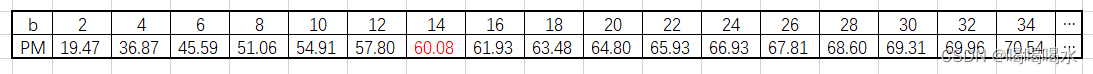

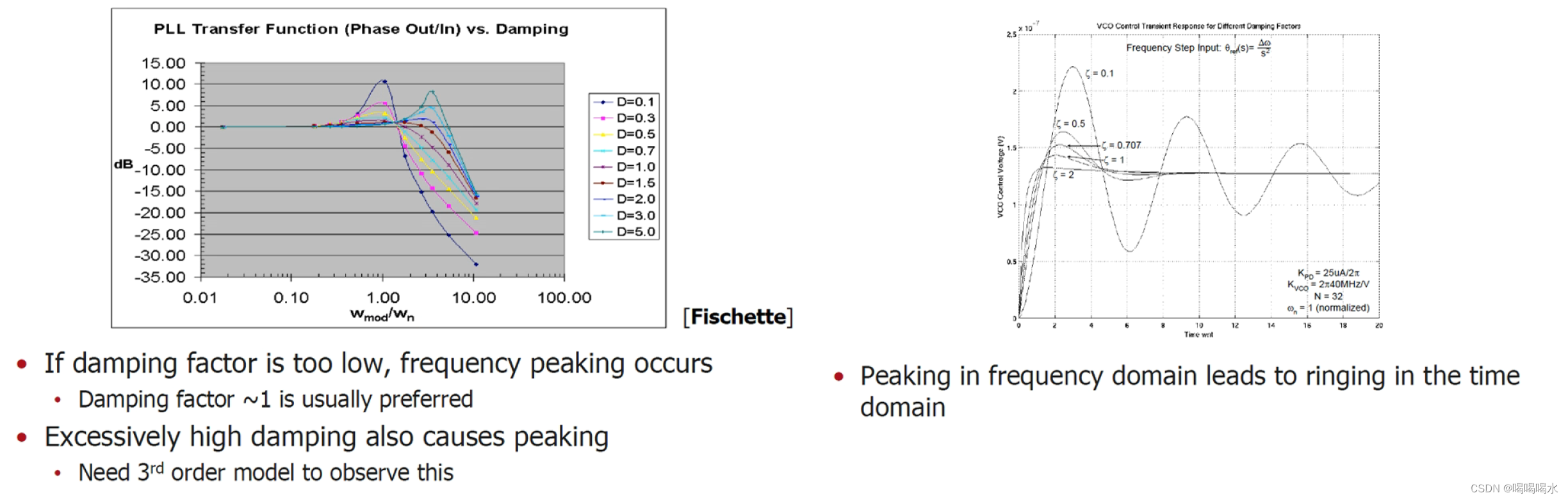

由上图可以看出,当LPF为一阶时,LPF提供一个左半平面零点 从PLL的环路增益公式中,我们可以得知零极点的位置,分别为: 显然,当环路带宽 令 我们看PLL的相位裕度与零极点的关系: 带入b的值可得PM值,如下图:

可以看出,b取值越大,即C2越小于C1,即 PLL的关键参数环路带宽、阻尼系数,一般是在设计之前就需要确定的。 对于环路带宽,一种求值方式为,令 可以看出环路带宽与CP电流Icp、电阻R、VCO的Kvco和分频比N有关,对于PLL系统,一般输入输出频率是确定的,N也随之确定,Kvco一般随着VCO设计完后也不容易修改,电阻R调整也伴随着电容C需要调整以保证零极点位置,所以最容易改变的参数就是Icp,完全可以多做几路电流源来实现。 前面提到了环路带宽的选取依据,总结几点如下: 为保证线性模型近似成立,环路带宽要小于输入参考频率的1/10~1/15。为保证环路快速锁定,环路带宽越大越好,锁定时间的经验公式通常采用二阶PLL模型计算阻尼系数和固有频率,即忽略LPF中的C2,闭环传递函数如下: 标准二阶公式为: 可得, 并且有,

为保证环路的稳定和快速锁定,阻尼系数 ++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++ 以上就是我对PLL线性模型的理论分析总结,学习时间不长,认识较浅,欢迎各位同学批评指正,共同进步! |

【本文地址】

今日新闻 |

点击排行 |

|

推荐新闻 |

图片新闻 |

|

专题文章 |