Serdes 高速串行接口 |

您所在的位置:网站首页 › serdes协议 › Serdes 高速串行接口 |

Serdes 高速串行接口

|

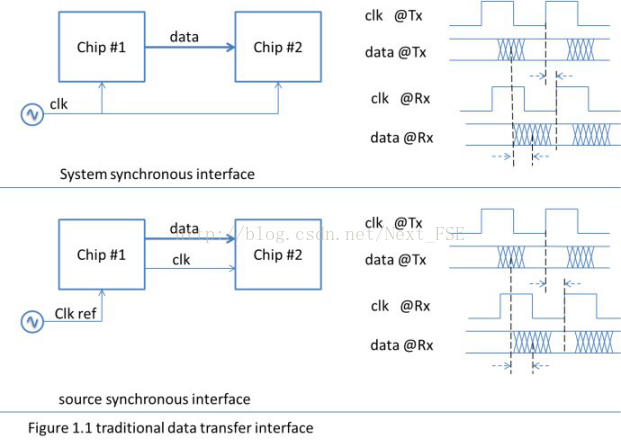

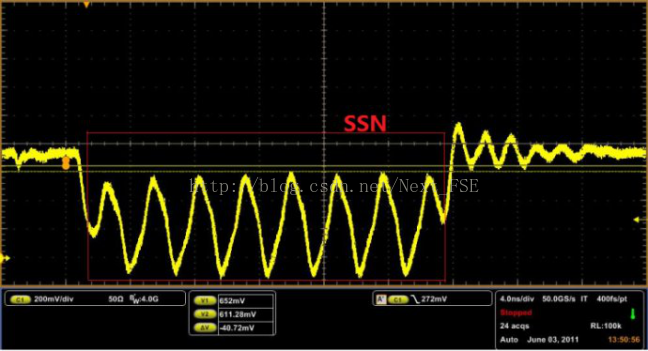

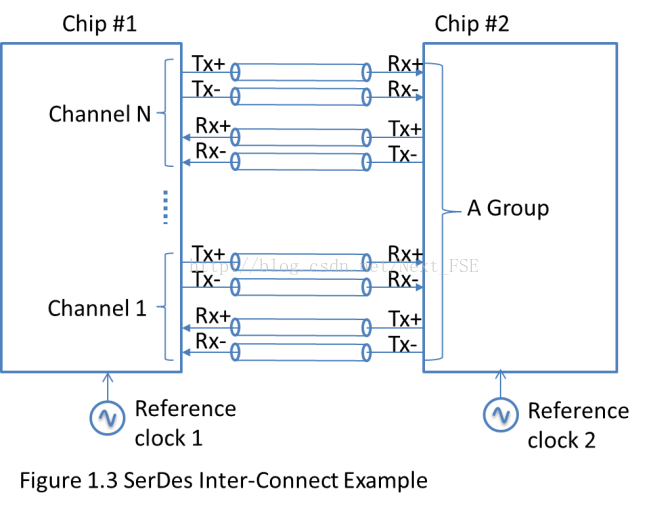

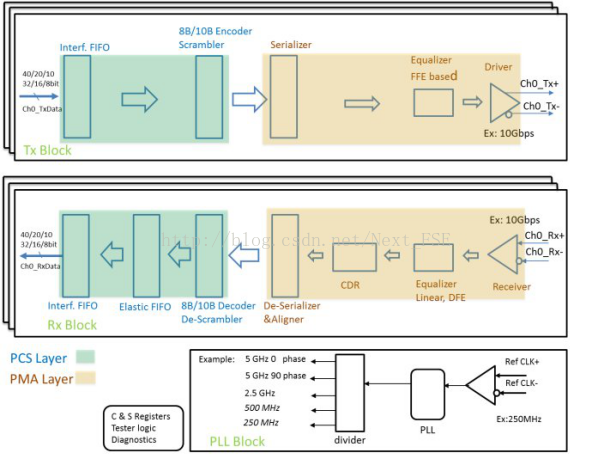

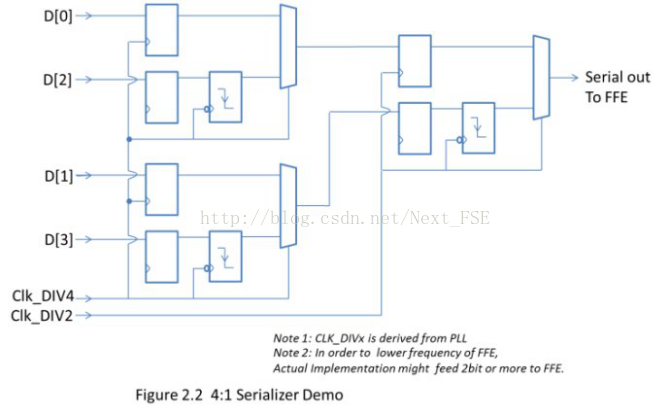

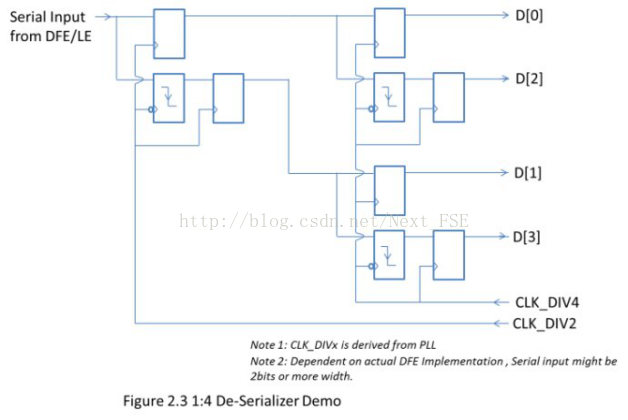

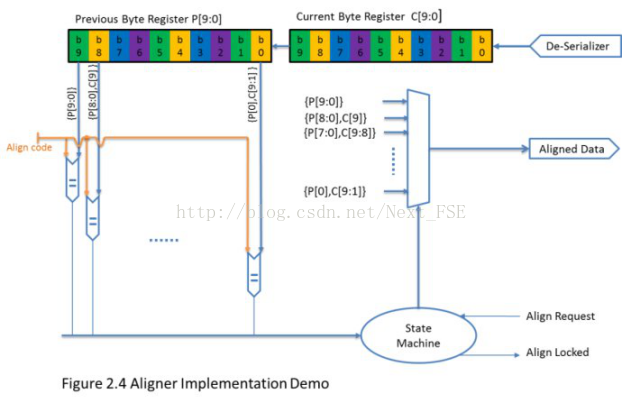

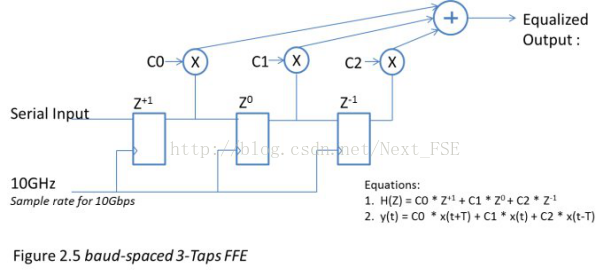

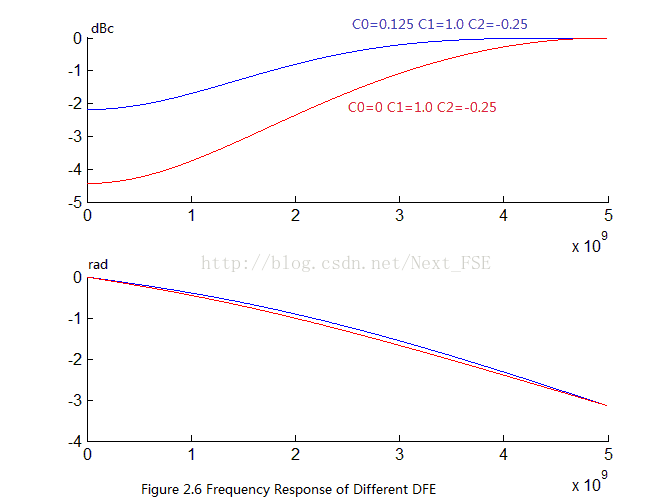

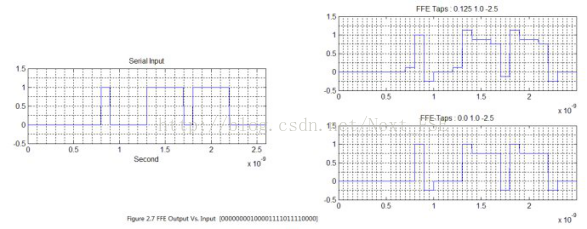

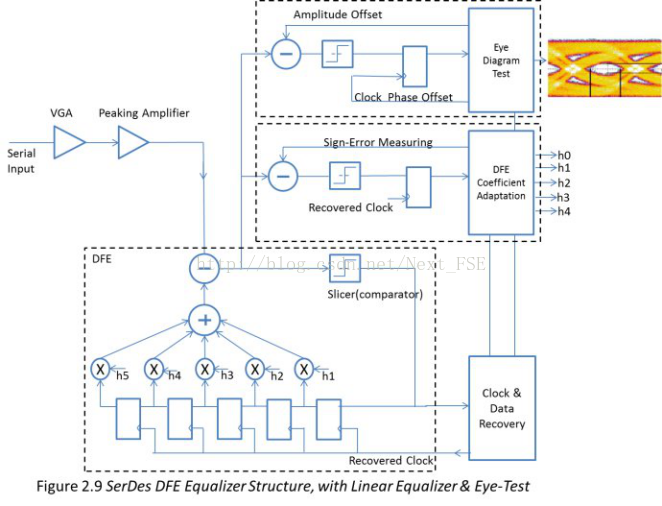

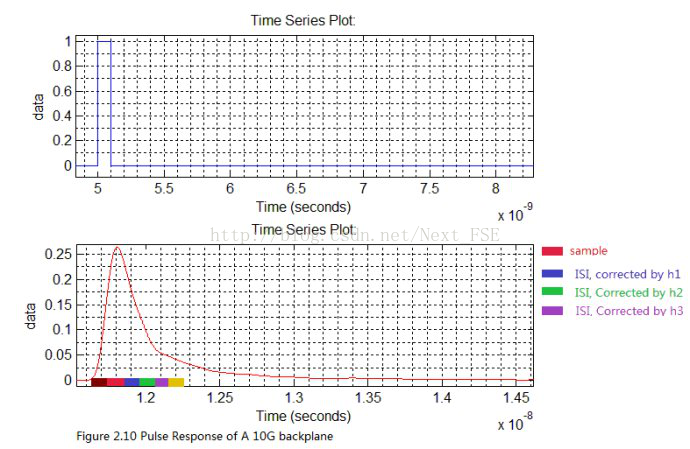

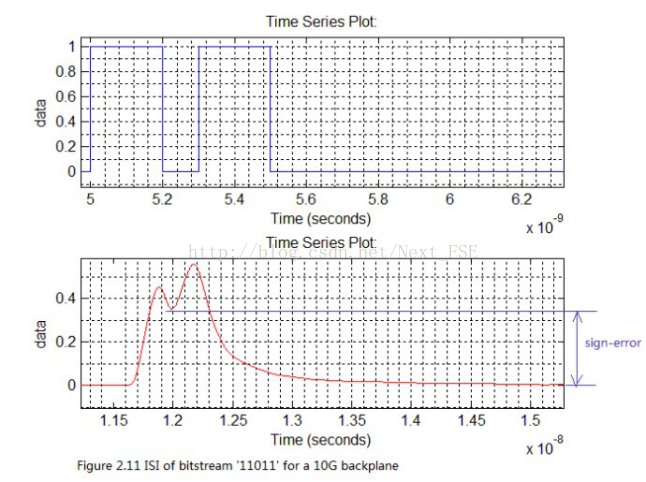

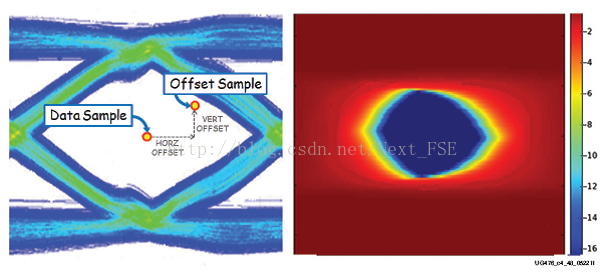

一、SERDES的作用 1.1并行总线接口 在SerDes流行之前,芯片之间的互联通过系统同步或者源同步的并行接口传输数据,图1.1演示了系统和源同步并行接口。 随着接口频率的提高,在系统同步接口方式中,有几个因素限制了有效数据窗口宽度的继续增加。 a)、时钟到达两个芯片的传播延时不相等(clock skew) b)、并行数据各个bit的传播延时不相等(data skew) c)、时钟的传播延时和数据的传播延时不一致(skew between data and clock) 虽然可以通过在目的芯片(chip #2)内用PLL补偿时钟延时差(clock skew),但是PVT变化时,时钟延时的变化量和数据延时的变化量是不一样的。这又进一步恶化了数据窗口。 源同步接口方式中,发送侧Tx把时钟伴随数据一起发送出去, 限制了clock skew对有效数据窗口的危害。通常在发送侧芯片内部,源同步接口把时钟信号和数据信号作一样的处理,也就是让它和数据信号经过相同的路径,保持相同的延时。这样PVT变化时,时钟和数据会朝着同一个方向增大或者减小相同的量,对skew最有利。 我们来做一些合理的典型假设,假设一个32bit数据的并行总线, a)、发送端的数据skew = 50 ps —很高的要求 b)、pcb走线引入的skew = 50ps —很高的要求 c)、时钟的周期抖动jitter = +/-50 ps —很高的要求 d)、接收端触发器采样窗口 = 250 ps —Xilinx V7高端器件的IO触发器 可以大致估计出并行接口的最高时钟 = 1/(50+50+100+250) = 2.2GHz (DDR)或者1.1GHz (SDR)。 利用源同步接口,数据的有效窗口可以提高很多。通常频率都在1GHz以下。在实际应用中可以见到如SPI4.2接口的时钟可以高达DDR 700MHz x 16bits位宽。DDR Memory接口也算一种源同步接口,如DDR3在FPGA中可以做到大约800MHz的时钟。 要提高接口的传输带宽有两种方式,一种是提高时钟频率,一种是加大数据位宽。那么是不是可以无限制的增加数据的位宽呢?这就要牵涉到另外一个非常重要的问题—–同步开关噪声(SSN)。 这里不讨论SSN的原理,直接给出SSN的公式: SSN = L *N* di/dt。 L是芯片封装电感,N是数据宽度,di/dt是电流变化的斜率。 随着频率的提高,数据位款的增加,SSN成为提高传输带宽的主要瓶颈。图1.2是一个DDR3串扰的例子。图中低电平的理论值在0V,由于SSN的影响,低电平表现为震荡,震荡噪声的最大值达610mV,因此噪声余量只有1.5V/2-610mV=140mV。 Figure 1.2 DDR3串扰演示 因此也不可能靠无限的提高数据位宽来继续增加带宽。一种解决SSN的办法是使用差分信号替代单端信号,使用差分信号可以很好的解决SSN问题,代价是使用更多的芯片引脚。使用差分信号仍然解决不了数据skew的问题,很大位宽的差分信号再加上严格的时序限制,给并行接口带来了很大的挑战。 1.2 SerDes接口 源同步接口的时钟频率已经遇到瓶颈,由于信道的非理想(channel)特性,再继续提高频率,信号会被严重损伤,就需要采用均衡和数据时钟相位检测等技术。这也就是SerDes所采用的技术。SerDes(Serializer-Deserializer)是串行器和解串器的简称。串行器(Serializer)也称为SerDes发送端(Tx),(Deserializer)也称为接收端Rx。Figure1.3是一个N对SerDes收发通道的互连演示,一般N小于4。 可以看到,SerDes不传送时钟信号,这也是SerDes最特别的地方,SerDes在接收端集成了CDR(Clock Data Recovery)电路,利用CDR从数据的边沿信息中抽取时钟,并找到最优的采样位置。 SerDes采用差分方式传送数据。一般会有多个通道的数据放在一个group中以共享PLL资源,每个通道仍然是相互独立工作的。 SerDes需要参考时钟(Reference Clock),一般也是差分的形式以降低噪声。接收端Rx和发送端Tx的参考时钟可以允许几百个ppm的频差(plesio-synchronous system),也可以是同频的时钟,但是对相位差没有要求。 作个简单的比较,一个SerDes通道(channel)使用4个引脚(Tx+/-,Rx+/-), 目前的FPGA可以做到高达28Gbps。而一个16bits的DDR3-1600的线速率为1.6Gbps*16 = 25Gbps,却需要50个引脚。此对比可以看出SerDes在传输带宽上的优势。 相比源同步接口,SerDes的主要特点包括: SerDes在数据线中时钟内嵌,不需要传送时钟信号。 SerDes通过加重/均衡技术可以实现高速长距离传输,如背板。 SerDes 使用了较少的芯片引脚 1.3 中间类型 也存在一些介于SerDes和并行接口之间的接口类型,相对源同步接口而言,这些中间类型的接口也使用串行器(Serializer)解串器(Deserializer),同时也传送用于同步的时钟信号。这类接口如视频显示接口7:1 LVDS等。 二、 SerDes结构(architecture) SerDes的主要构成可以分为三部分,PLL模块,发送模块Tx,接收模块Rx。为了方便维护和测试,还会包括控制和状态寄存器,环回测试,PRBS测试等功能。见图2.1。 Figure 2.1 Basic Blocks of a typical SerDes 图中蓝色背景子模块为PCS层,是标准的可综合CMOS数字逻辑,可以硬逻辑实现,也可以使用FPGA软逻辑实现,相对比较容易被理解。褐色背景的子模块是PMA层,是数模混合CML/CMOS电路,是理解SerDes区别于并行接口的关键,也是本文要讨论的内容。 发送方向(Tx)信号的流向: FPGA软逻辑(fabric)送过来的并行信号,通过接口FIFO(Interface FIFO),送给8B/10B编码器(8B/10B encoder)或扰码器(scambler),以避免数据含有过长连零或者连1。之后送给串行器(Serializer)进行 并->串 转换。串行数据经过均衡器(equalizer)调理,有驱动器(driver)发送出去。 接收方向(Rx)信号的流向, 外部串行信号由线性均衡器(Linear Equalizer)或DFE (Decision Feedback Equalizer判决反馈均衡)结构均衡器调理,去除一部分确定性抖动(Deterministic jitter)。CDR从数据中恢复出采样时钟,经解串器变为对齐的并行信号。8B/10B解码器(8B/10B decoder)或解扰器(de-scambler)完成解码或者解扰。如果是异步时钟系统(plesio-synchronous system),在用户FIFO之前还应该有弹性FIFO来补偿频差。 补充:均衡器 在通信系统的基带或中频部分插入的,能够减少码间干扰, 起到补偿作用的滤波器。分为频域均衡器和时域均衡器。 频域均衡器 频域均衡器利用可调滤波器的频率特性来弥补实际信道的幅频特性和群延时特性,使包括均衡器在内的整个系统的总频率特性满足无码间干扰传输条件。 时域均衡器 时域均衡器是直接从时间响应角度考虑,使包括均衡器在内的整个传输系统的冲激响应满足无码间干扰条件。频域均衡满足奈奎斯特整形定理的要求,仅在判决点满足无码间干扰的条件相对宽松一些。所以,在数字通信中一般时域均衡器使用较多。 时域均衡器可以分两大类:线性均衡器和非线性均衡器。如果接收机中判决的结果经过反馈用于均衡器的参数调整,则为非线性均衡器;反之,则为线性均衡器。在线性均衡器中,最常用的均衡器结构是线性横向均衡器,它由若干个抽头延迟线组成,延时时间间隔等于码元间隔。非线性均衡器的种类较多,包括判决反馈均衡器(DFE)、最大似然(ML)符号检测器和最大似然序列估计等。 PLL负责产生SerDes各个模块所需要的时钟信号,并管理这些时钟之间的相位关系。以图中线速率10Gbps为例,参考时钟频率250MHz。Serializer/Deserializer至少需要5GHz 0相位时钟和5GHz 90度相位时钟,1GHz(10bit并行)/1.25GHz(8bit并行)时钟等。 一个SerDes通常还要具调试能力。例如伪随机码流产生和比对,各种环回测试,控制状态寄存器以及访问接口,LOS检测, 眼图测试等。 2.1串行器解串器(Serializer/Deserializer) 串行器Serializer把并行信号转化为串行信号。Deserializer把串行信号转化为并行信号。一般地,并行信号为8 /10bit或者16/20bit宽度,串行信号为1bit宽度(也可以分阶段串行化,如8bit->4bit->2bit->equalizer->1bit以降低equalizer的工作频率)。采用扰码(scrambled)的协议如SDH/SONET, SMPTE SDI使用8/16bit的并行宽度,采用8B/10B编码的协议如PCIExpress,GbE使用10bits/20bits宽度。 一个4:1的串行器如图所示。8:1或16:1的串行器采用类似的实现。实现时,为了降低均衡器的工作频率,串行器会先把并行数据变为2bits,送给均衡器equalizer滤波,最后一步再作2:1串行化,本文后面部分都按1bit串行信号解释。 一个1:4的解串器如图2.3所示,8:1或16:1的解串器采用类似的实现。实现时,为了降低均衡器(DFE based Equalizer)的工作频率,DFE工作在DDR模式下,解串器的输入是2bit或者更宽,本文后面部分都按1bit串行信号解释。 Serializer/Deserializer的实现采用双沿(DDR)的工作方式,利用面积换速度的策略,降低了电路中高频率电路的比例,从而降低了电路的噪声。 接收方向除了Deserializer之外,一般带有还有对齐功能逻辑(Aligner)。相对SerDes发送端,SerDes接收端起始工作的时刻是任意的,接收器正确接收的第一个 bit可能是发送并行数据的任意bit位置。因此需要对齐逻辑来判断从什么bit位置开始,以组成正确的并行数据。对齐逻辑通过在串行数据流中搜索特征码字(Alignment Code)来决定串并转换的起始位置。比如8B/10B编码的协议通常用K28.5(正码10’b1110000011,负码10’b0001111100)来作为对齐字。图2.4为一个对齐逻辑的演示。通过滑窗,逐bit比对,以找到对齐码(Align-Code)的位置,经过多次在相同的位置找到对齐码之后,状态机锁定位置并选择相应的位置输出对齐数据。 2.2发送端均衡器( Tx Equalizer) SerDes信号从发送芯片到达接收芯片所经过的路径称为信道(channel),包括芯片封装,pcb走线,过孔,电缆,连接器等元件。从频域看,信道可以简化为一个低通滤波器(LPF)模型,如果SerDes的速率大于信道(channel)的截止频率,就会一定程度上损伤(distort)信号。均衡器的作用就是补偿信道对信号的损伤。 发送端的均衡器采用FFE(Feed forward equalizers)结构,发送端的equalizer也称作加重器(emphasis)。加重(Emphasis)分为去加重(de-emphasis)和预加重(pre-emphasis)。De-emphasis降低差分信号的摆幅(swing)。Pre-emphasis增加差分信号的摆幅。FPGA大部分使用de-emphasis的方式,加重越强,信号的平均幅度会越小。 发送侧均衡器设计为一个高通滤波器(HPF),大致为信道频响H(f)的反函数H-1(f),FFE的目标是让到达接收端的信号为一个干净的信号。FFE的实现方式有很多,一个典型的例子如图2.5所示。 调节滤波器的系数可以改变滤波器的频响,以补偿不同的信道特性,一般可以动态配置。以10Gbps线速率为例,图2.5为DFE频率响应演示。可以看到,对于C0=0,C1=1.0,C2=-0.25的配置,5GHz处高频增益比低频区域高出4dB,从而补偿信道对高频频谱的衰减。 采样时钟的频率限制了这种FFE最高只能补偿到Fs/2(例子中Fs/2=5GHz)。根据采样定理,串行数据里的信息都包含在5GHz以内,从这个角度看也就足够了。如果要补偿Fs/2以上的频率,就要求FFE高于Fs的工作时钟,或者连续时间域滤波器(Continuous Time FFE)。 图2.7为DFE时域滤波效果的演示,以10Gbps线速率为例,一个UI=0.1 nS=100ps。演示的串行数据码流为二进制[00000000100001111011110000]。 2.3接收端均衡器( Rx Equalizer) 2.3.1 线形均衡器(Linear Equalizer)接收端均衡器的目标和发送均衡器是一致的。对于低速(5Gbps)SerDes,由于信号的抖动(如ISI相关的确定性抖动)可能会超过或接近一个符号间隔(UI, Unit Interval), 单单使用线性均衡器不再适用。线性均衡器对噪声和信号一起放大,并没有改善SNR或者说BER。对于高速SerDes,采用一种称作DFE (Decision Feedback Equalizer裁决反馈均衡器)的非线性均衡器。DFE通过跟踪过去多个UI的数据(history bits)来预测当前bit的采样门限。DFE只对信号放大,不对噪声放大,可以有效改善SNR。 补充: Unit Interval 单位时间间隔:通常在通信信号的抖动测试中用来表示抖动幅度的单位。表示一个等步信号的两个相邻的有效瞬时之间的标称时间差 图2.9演示了一个典型的5阶DFE。接收的串行数据由比较器(slicer)来判决0或者1,然后数据流由一个滤波器来预测码间干扰(ISI),再从输入的原始信号中减掉码间干扰(ISI),从而的到一个干净的信号。为了让DFE均衡器的电路工作在电路线形范围内,串行信号先经过VGA自动控制进入DFE的信号幅度。 为了理解DFE的工作原理,先来看一个10Gbps背板的脉冲响应,这个背板模型是matlab给出的一个基于实测的模型,具有典型特性。 图2.10中,一横格代表一个UI的时间。可以看出,一个UI( 0.1nS = 1/10GHz )的脉冲信号,通过背板后,泄漏到前后多个相邻的UI里面,从而对其他UI的数据产生干扰。采样点后面的干扰叫做post-cursor干扰,采样点前面的叫做pre-cursor干扰。DFE的第一个系数 h1(此例中0.175)矫正第一个post-cursor, 第二个系数 h2(此例中0.075)矫正第二个post-cursor。DFE的阶数越多,能够校正的post-cursor也越多。 用上述的背板传输一个11011的码流,由于post-cursor和pre-cursor的泄漏,如果没有均衡,将会导致’0’不能识别,见图2.11。假定有一个2阶的DFE, 那么‘0’bit处的幅度应该减去第一个’1’bit的h2, 第二个’1’bit的h1, 得到0.35-0.075-0.175 =0.1, 足够被识别为0。 可见,DFE计算历史bits的post-cursor干扰,在当前bit中把干扰减去,从而得到干净的信号。由于DFE只能能够校正post-cursor ISI, 所以DFE前面一般会带有LE。只要DFE的系数接近信道(channel)的脉冲相应,就可以到的比较理想的结果。但是信道是一个时变的媒介,比如温度电压工艺的慢变化等因素会改变信道channel的特性。因此DFE的系数需要自适应算法,自动扑获和跟随信道的变化。DFE系数自适应算法非常学术,每个厂商的算法都是保密的,不对外公布。对于NRZ码,典型的算法准则是基于sign-error驱动的算法。Sign-error是均衡后信号的幅度和期望值的误差,算法以sign-error均方差最小为优化目标,逐次优化h1/h2/h3…。因为sign-error和采样位置是耦合在一起相互影响,因此也可以sign-error和眼图宽度两个准则为目标进行DFE系数的预测。也因此,采用DFE结构的SerDes通常都会带有内嵌眼图测试电路,如图2.9所示。眼图测试电路通过垂直方向上平移信号的幅度,水平方向上平移采样位置,计算每一个平移位置上的误码率BER,从而得到每一个偏移位置与误码率关系的”眼图”,见图2.12。 Figure 2.12 SerDes Embedded Eye-Diagram Test Function 2.4时钟数据恢复(CDR) CDR的目标是找到最佳的采样时刻,这需要数据有丰富的跳变。CDR有一个指标叫做最长连0或连1长度容忍(Max Run Length或者Consecutive Identical Digits)能力。如果数据长时间没有跳变,CDR就无法得到精确的训练,CDR采样时刻就会漂移,可能采到比真实数据更多的1或者0。而且当数据重新恢复跳变的时,有可能出现错误的采样。比如有的CDR采用PLL实现,如果数据长时间停止跳变,PLL的输出频率就会漂移。实际上,SerDes上传输的数据要么利用加扰,要么利用编码的方法来保证Max Run Length在一定的范围内。 8B/10B编码的方法可以保证Max Run Length不超过5个UI。 64B/66B编码的方法可以保证Max Run Length不超过66个UI SONET/SDH加扰得方法可以保证Max Run Length不超过80个UI(BER |

【本文地址】

今日新闻 |

点击排行 |

|

推荐新闻 |

图片新闻 |

|

专题文章 |