PON BIP8问题分析 |

您所在的位置:网站首页 › SDH原理 › PON BIP8问题分析 |

PON BIP8问题分析

|

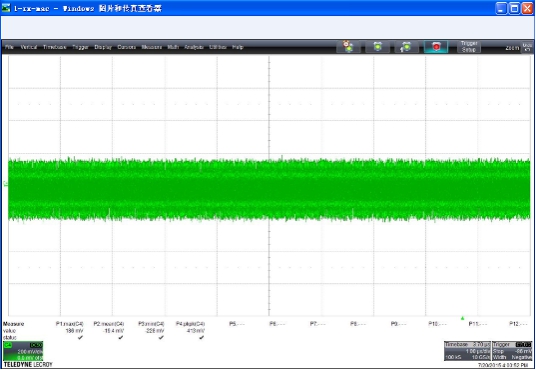

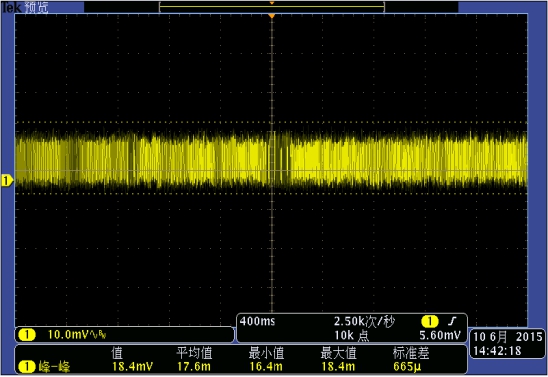

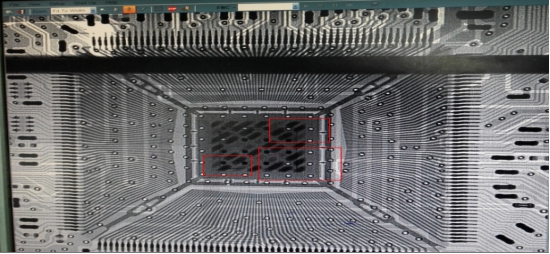

1、问题描述 现网同一PON下挂多台样机(32台以上),个别样机出现下行BIP 8 Error告警, 2、问题定位分析过在送样50台样机中共发现8台样机存在BIP Error问题,同批次样机存在一定不良比例,定位个体差异引起并非必现设计问题。 2.1 验证环境影响将问题样机在同一个OLT环境下,改变光路衰减,在有效功率范围内,告警频率随功率变大而减小; 在不同OLT环境下部分样机告警取消,但还是有6台样机持续告警,确认样机本身有问题。 第一验证结论,环境影响BIP告警,但样机存在问题。 2.2 ONU差异验证检查ONU个体差异问题,依据之前测试经验, 光链路BIP Error问题与光信号链路相关, a、检测Serdes信号 RX:

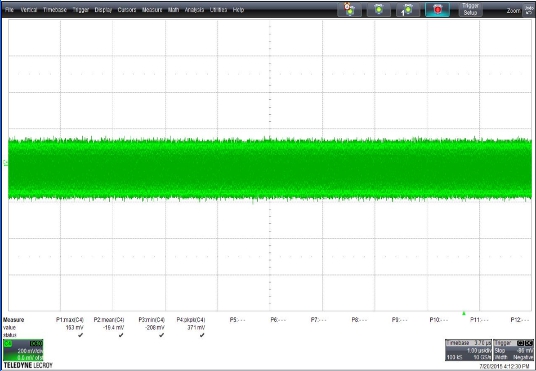

TX:

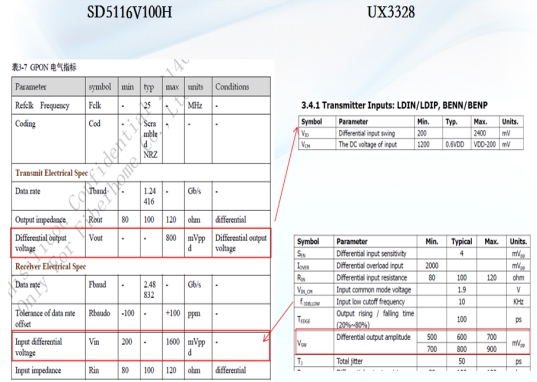

由于RX信号为持续信号,不存在类似TX 信号翻转上升沿不足问题,确认数字信号没有问题,满足芯片要求, 芯片Datasheet要求

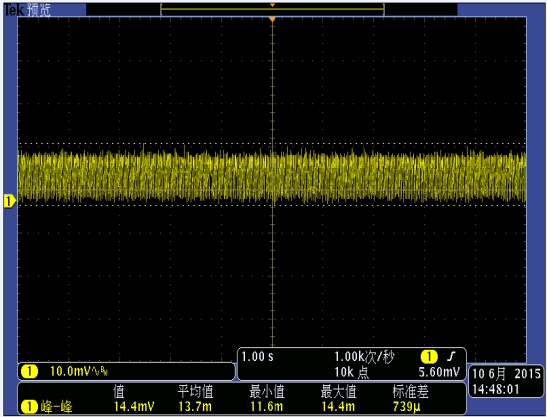

b、供电电源1.1V、3.3V ,Ripple 满足要求

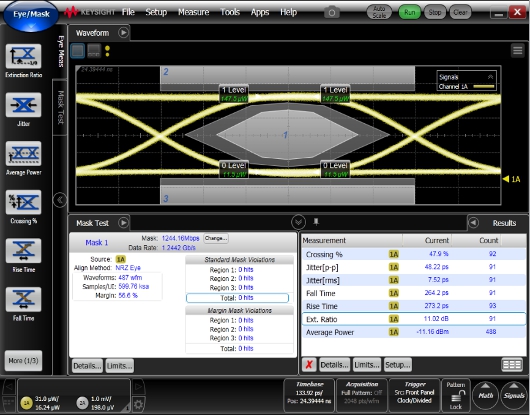

c、光眼图测试Pass

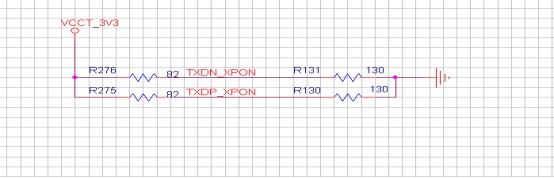

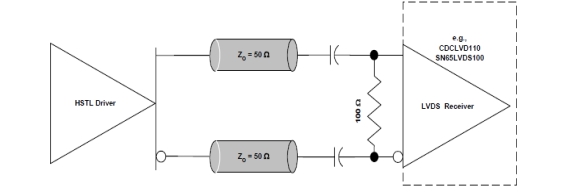

第二验证证明目前光链路信号满足信号完整性要求,再一次排除信号引质量引入的问题 2.3 配合软件再次分析硬件设计电路在Serdes电路设计中,预留上件戴维南匹配与模块内部高速信号匹配重复,在信号匹配上存在设计逻辑错误,去件验证发现,去掉外部匹配,告警速率会有所下降,但是异常样机告警始终存在。

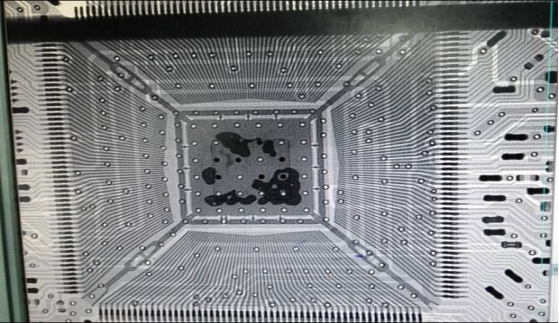

a、删除wifi模块,对测试结果无影响 b、删除语音模块,对测试结果无影响 c、更换flash型号,对测试结果无影响 d、更换CPU验证,原异常样机告警消失 针对更换CPU验证,维修3PCS样机,告警问题都有改善; 针对不同版本的5116H(100\110)芯片交叉验证,发现重焊的两个版本芯片样机都可以改善BIP告警问题。 针对不良品样机进行X-Ray分析:

从焊接请款来看,CPU下方锡厚度有明显差异,且焊点接触面积过小,仅20~30%,不能满足芯片EPAD接触点要求。 手焊修复样机:

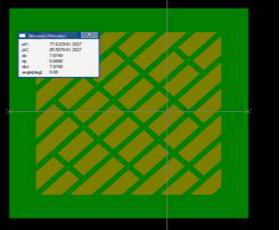

虽然焊接点并非很大,但是相对于不良样机有较大面积改善。 3、问题结论1、 本次BIP告警主要由于芯片焊接不良导致,针对EPAD-LQFP216 大型芯片焊接,生产前没有进行特殊评估,按照经验操作,导致上锡量不能满足芯片焊接要求; 2、 排查过程中,发现了设计缺陷及告警相关因素:高速信号匹配电路重复预留、ONU应用场景环境的保障。 4、解决或规避措施焊接不良原因: 1. 物料PIN脚变形,加大了零件PIN脚底部到零件本体的距离,这样锡膏无法和零件形成焊接; 2. 锡量不够导致。已确认目前钢网开孔面积接近PAD 50%,正常情况下应该是可以满足焊接的。 (可能性较大)。 目前共进钢网设计:

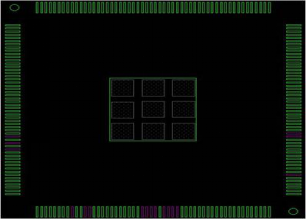

PCB PAD尺寸:7.9*7.9MM,面积约62 钢网开孔尺寸6.1*6.1MM,除去中间的架桥,面积约30,占PAD面积的48%。 后续更改如下: 采用9宫格的开孔方式。单格开孔尺寸:2.1*2.1MM

总开孔面积2.1*2.1*9=39.7,占PAD总面积的62%,比之前的开孔面积增加了14%。 生产改善方案: 生产过程中是修改钢网开孔,加大钢网的开孔面积,增加锡量。 设计改善建议: 删除外部戴维南匹配电路 |

【本文地址】

今日新闻 |

点击排行 |

|

推荐新闻 |

图片新闻 |

|

专题文章 |