| #systemverilog# 关于随机约束 unique、unique if | 您所在的位置:网站首页 › 随机查找的定义 › #systemverilog# 关于随机约束 unique、unique if |

#systemverilog# 关于随机约束 unique、unique if

|

前言

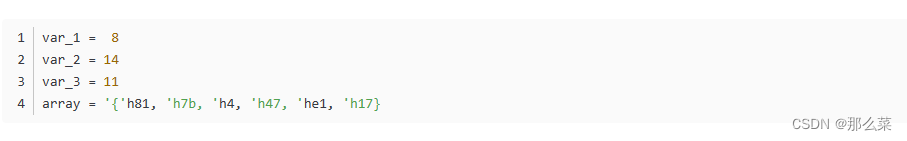

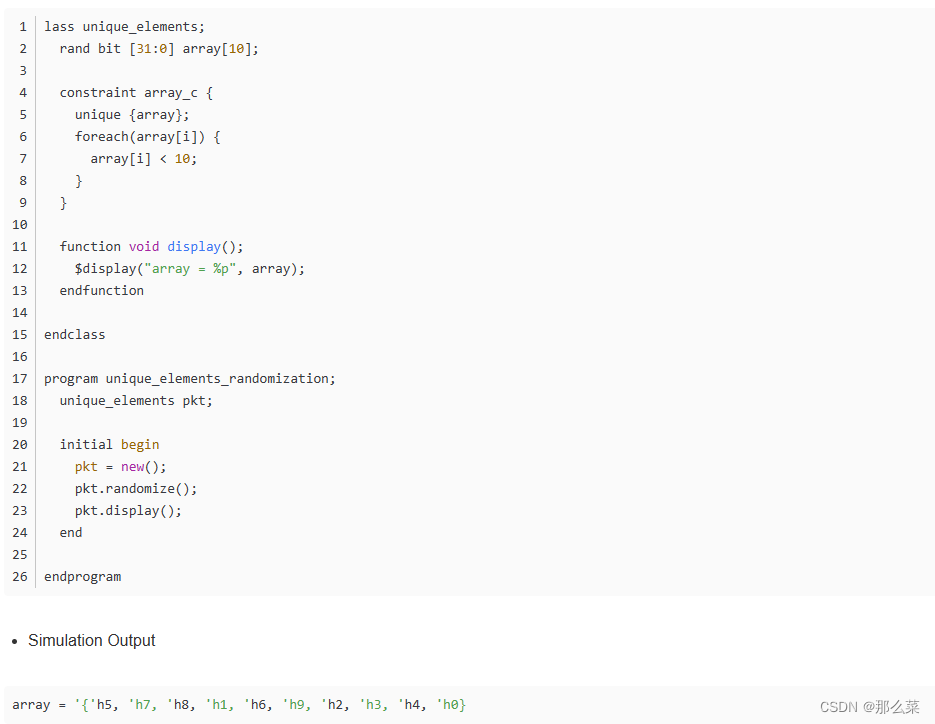

使用关键字unique定义的SystemVerilog约束称为唯一约束。在随机化中,使用唯一约束可以生成变量集的唯一值或数组的唯一元素。 通过unique约束我们可以完成以下任务: 在变量之间生成唯一的值在数组中生成唯一元素(固定大小数组、动态数组、关联数组和队列)Unique if evaluates all the conditions parallel. In the following conditions simulator issue a run time error/warning: More than one condition is true ; No condition is true or final if doesn’t have corresponding else ; 一、唯一约束的例子 1.1、产生唯一的元素 class unique_elements; rand bit [3:0] var_1,var_2,var_3; rand bit [7:0] array[6]; constraint varis_c {unique {var_1,var_2,var_3};} constraint array_c {unique {array};} function void display(); $display("var_1 = %p",var_1); $display("var_2 = %p",var_2); $display("var_3 = %p",var_3); $display("array = %p",array); endfunction endclass program unique_elements_randomization; unique_elements pkt; initial begin pkt = new(); pkt.randomize(); pkt.display(); end endprogram

In the below example,More than one condition is true.value of a=10, b=20 and c=40. conditions a |

【本文地址】

公司简介

联系我们