| DDR介绍及设计要求详解1 | 您所在的位置:网站首页 › 通信模组设计规范要求 › DDR介绍及设计要求详解1 |

DDR介绍及设计要求详解1

|

DDR介绍及设计要求详解

DDR类别和参数介绍

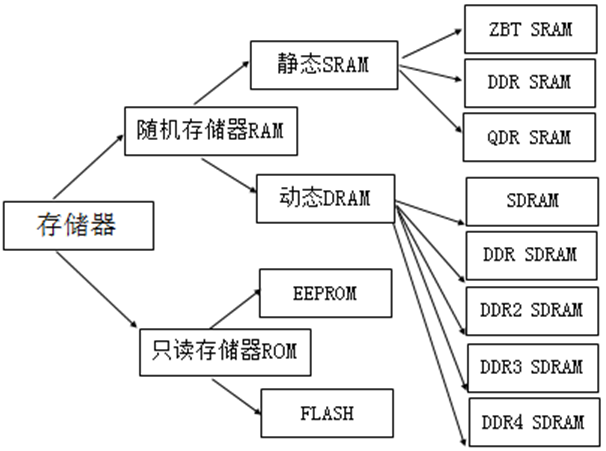

DDR采用TSSOP封装技术,而DDR2和DDR3内存均采用FBGA封装技术。TSSOP封装的外形尺寸较大,呈长方形,其优点是成本低、工艺要求不高,缺点是传导效果差,容易受干扰,散热不理想,而FBGA内存颗粒精致小巧,体积大约只有DDR内存颗粒的三分之一,有效地缩短信号传输距离,在抗干扰、散热等方面更有优势,而DDR4采用3DS(3-Dimensional Stack)三维堆叠技术来增大单颗芯片容量,封装外形则与DDR2、DDR3差别不大。在我们的设计用到的内存颗粒有SRAM、DRAM、EEPROM、Flash等,其中DDR系列用的是最多的,其DDR-DDR4的详细参数如下:

随着制造工艺不断提高,从DDR到DDR2再到DDR3内存,其制造工艺都在不断改善,更高工艺水平会使内存电气性能更好,成本更低;DDR内存颗粒广泛采用0.13微米制造工艺,而DDR2采用了0.09微米制造工艺,DDR3则采用了全新65nm制造工艺,而DDR4使用20nm以下的工艺来制造,从DDR~DDR4的具体参数如下表所示 MemoryType DDR DDR2 DDR3 DDR4 核心频率(MHz) 133-200 133-200 133-200 133-200 时钟频率(MHz) 133-200 266-400 533-800 1066-1600 预读数 2n 4n 8n 8n 数据传输速率(MT/s) 266-400 533-800 1066-1600 2133-3200 带宽(GB/s) 2.1-3.1 4.2-6.4 8.5-14.9 17-21.3 工作电压(V) 2.5/2.6 1.8 1.35/1.5 1.2 最大功耗 418mW 318mW

通常工作电压 2.5V 1.8V 1.5V 1.2V 移动计算低压标准 \ 1.2V(LPDDR2) 1.2V(LPDDR3) 1.1V(LPDDR4) 笔记本电脑低压标准 \ \ 1.35V(DDR3L) 1.05V(DDR4L) 接口标准 SSTL_2(2.5V) SSTL_1.8(1.8V) SSTL_1.5(1.5V) POD12(1.2V) VTT电压 1.25V 0.9V 0.75V 0.6V VREF电压 1.25V 0.9V 0.75V 0.6V 时钟地址控制布线 “T”型 “T”型 “Fly-by”型 “Fly-by”型 DQS选通信号 单端 单端/差分 差分 差分 时钟信号 单端/差分 单端/差分 差分 差分 ODT信号 无 有 有 有 WriteLeveling 无 无 有 有 DBI(降低功耗并提升SI) 无 无 无 有 时钟频率(MHz) 100/133/166/200 200/266/333/400 400/533/667/800 800/933/1066/1200 数据传输率(Mbps) 200/266/333/400 400/533/667/800 800/1066/1333/1600-2133 1600/1866/2133/2400-3200 容量标准 64M~1G 256M~4G 512M~8G 2G~16G 封装形式 TSOP FBGA FBGA FBGA(堆叠引脚) 预取设计(Bit) 2 4 8 16 “Burst”突发长度 2/4/8 4/8 8 8 逻辑BANK数量 2/4 4/8 8/16 16/32 CL值 1.5、2.5、3.5、3 3、4、5、6 5、6、7、8、9、10、11

AL值 无 0、1、2、3、4 0、CL-1、CL-2

驱动校准

Off-Chip(OCD) On-ChipwithZQpin(ZQcal)

新增特性

ODT、OCDCalibration、PostedCAS,AL CWD、Reset、ZQ、SRT、PASR

DDR原理介绍 2.1. 定义说明 SDRAM介绍:SDRAM是SynchronousDynamicRandomAccessMemory(同步动态随机存储器)的简称,是使用很广泛的一种存储器,一般应用在200MHz以下,常用在33MHz、90MHz、100MHz、125MHz、133MHz等。其中同步是指时钟频率与SDRAM控制器如CPU前端其时钟频率与CPU前端总线的系统时钟频率相同,并且内部命令的发送和数据的传输都以它为准;动态是指存储阵列需要不断刷新来保证数据不丢失;随机是指数据不是线性一次存储,而是自由指定地址进行数据的读写。为了配合SDRAM控制芯片的总线位宽,必须配合适当数量的SDRAM芯片颗粒,如32位的CPU芯片,如果用位宽16bit的SDRAM芯片就需要2片,而位宽8bit的SDRAM芯片则就需要4片。 DDR SDRAM全称为Double Data Rate SDRAM,中文名为“双倍数据率SDRAM”,是在SDRAM的基础上改进而来,人们习惯称为DDR,DDR本质上不需要提高时钟频率就能加倍提高SDRAM的数据传输速率,它允许在时钟的上升沿和下降沿读取数据,因而其速度是标准SDRAM的两倍。 2.2. 相关信号说明

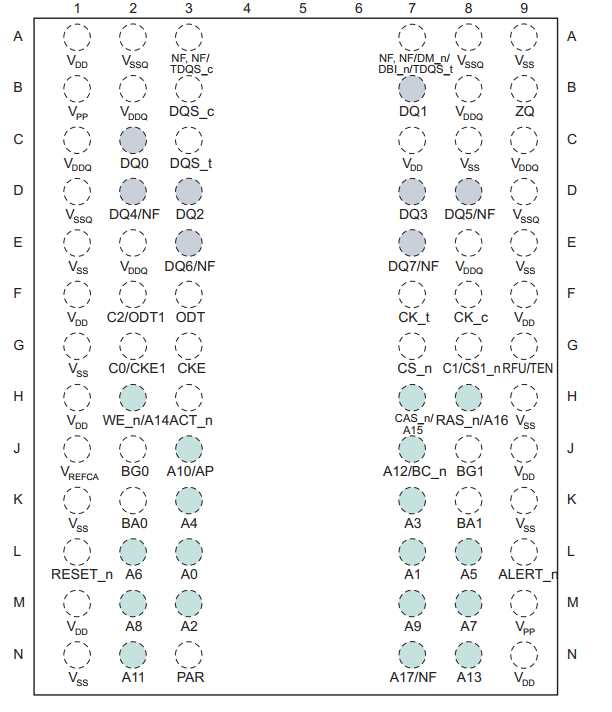

CLK是由系统时钟驱动的,SDRAM所有的输入信号都是在CLK的上升沿采样,CLK还用于触发内部计数器和输出寄存器; CK/CK#是DDR的全局时钟,DDR的所有命令信号,地址信号都是以CK/CK#为时序参考的。 CKE为时钟使能信号,与SDRAM不同的是,在进行读写操作时CKE要保持为高电平,当CKE由高电平变为低电平时,器件进入断电模式(所有BANK都没有激活时)或自刷新模式(部分BANK激活时),当CKE由低电平变为高电平时,器件从断电模式或自刷新模式中退出。 CS#为片选信号,低电平有效。当CS#为高时器件内部的命令解码将不工作。同时,CS#也是命令信号的一部分。 RAS#、CAS#、WE#分别为行选择、列选择、写使能信号,低电平有效。这三个信号与CS#一起组成了DDR的命令信号。 LDM、UDM为数据掩码信号。写数据时,当DM为高电平时对应的写入数据无效。LDM与UDM分别对应与数据信号的低8位与高8位。 A为地址总线信号。在读写命令时行列地址都由该总线输入。 BA0、BA1为BANK地址信号,用以确定当前的命令操作对哪个BANK有效。 DQ为数据总线信号。读写操作时的数据信号通过该总线输出或输入。 LDQS、UDQS为数据锁存信号,双沿有效。写数据时输入,读数据时输出。写数据时信号沿与数据中心对齐,读数据时信号沿与数据边沿对齐;LDQS与UDQS分别对应与数据信号的低8位与高8位。 VREF为SDRAM内部进行高低电平判决的参考电压。 2.3. 各版本差异从各版本DDR的性能来看SDRAM从发展到现在已经历经了六代,其分别是: 第一代SDRSDRAM,单边沿传输数据. 第二代DDRSDRAM,允许在时钟脉冲的上升沿和下降沿传输采样数据. 第三代DDR2SDRAM,拥有两倍与DDR1内存的预读取能力(即4bit数据预读取能力). 第四代DDR3SDRAM,具备更低的工作电压(1.5V),240线接口,支持8bit预读取. 第五代DDR4SDRAM,16bit预读取机制,同样核心频率下理论速度是DDR3的两倍. 第六代DDR5SDRAM32bit预读取机制,更低的工作电压(1.1v)。 DDR的数据信号与地址\控制信号是参考不同的时钟信号,数据信号参考DQS选通信号,地址\控制信号参考CK\CK#差分时钟信号;而SDRAM信号的数据、地址、控制信号是参考同一个时钟信号。 数据信号参考的时钟信号即DQS信号是上升沿和下降沿都有效,即DQS信号的上升沿和下降沿都可以触发和锁存数据,而SDRAM的时钟信号只有在上升沿有效,相对而言DDR的数据速率翻倍。 DDR的数据信号通常分成几组,如每8位数据信号加一位选通信号DQS组成一组,同一组的数据信号参考相同组里的选通信号。 DDR2新增功能与DDR1的不同之处 新增功能: ODT(On-DieTermination)即芯片内部匹配终结。 OCD(OffChipDriver)是加强上下拉驱动的控制功能,通过减小DQS与/DQS(DQS是数据Strobe,源同步时钟,数据的1和0由DQS作为时钟来判断)Skew(时滞)来增加信号的时序容限。 不同之处: 选通信号(DataStrobe)DQS采用了差分信号。 封装方面DDR采用TSOP封装,而DDRII采用FBGA封装 ODT技术使得DDRII的拓扑结构较DDR简单,布局布线也相对较容易一些。 DDR3新增功能与DDR2的不同之处 1,DDR3是相较于DDR2SDRAM具有更高的运行效能与更低的电压。 新增功能: CWD是作为写入延迟之用。 Reset提供了超省电功能的命令,可以让DDR3SDRAM内存颗粒电路停止运作、进入超省电待命模式。 ZQ则是一个新增的终端电阻校准功能,用来校准ODT内部终端电阻。 SRT(可编程化温度控制内存时脉功能)让内存颗粒在温度、时脉和电源管理上进行优化。 PASR(PartialArraySelf-Refresh)局部Bank刷新的功能,可以说针对整个内存Bank做更有效的资料读写以达到省电功效。 参考电压分成两个:在DDR3系统中,对于内存系统工作非常重要的参考电压信号VREF将分为两个信号,即为命令与地址信号服务的VREFCA和为数据总线服务的VREFDQ,这将有效地提高系统数据总线的信噪等级。 点对点连接(Point-to-Point,P2P):这是为了提高系统性能而进行的重要改动,也是DDR3与DDR2的一个关键区别。在DDR3系统中,一个内存控制器只与一个内存通道打交道,而且这个内存通道只能有一个插槽,因此,内存控制器与DDR3内存模组之间是点对点(P2P)的关系(单物理Bank的模组),或者是点对双点(Point-to-two-Point,P22P)的关系(双物理Bank的模组),从而大大地减轻了地址/命令/控制与数据总线的负载。 DDR设计要求详解DDR颗粒基本原理及个版本的差异及相似现针对DDR设计要求进行说明。 通用设计要求 当使用多片DDR芯片时布局首先要确认芯片是否支持FLY-BY走线拓扑结构,来确定我们是否采用T拓扑结构还是FLY-BY拓扑结构。如果是T拓扑结构时,上拉电阻放在T点处,如果使用FLY-BY拓扑,则把上拉电阻放在最后一片芯片的后端。上拉电阻的走线长度要小于500Mil。 电源走线有足够的通流能力:如果电源的走线宽度不足,则当DDR3芯片所需的电流超过电源走线的通流能力时,会因驱动能力不足导致信号幅度不能达到接口规范的要求,并进而导致对信号处理的错误。 确保回流路径的连续性:DDR3的信号走线必须以可靠的电源或地平面作为参考,不能跨越参考平面更不能没有参考平面,以保证信号能够以最短路径回流。此外,为了确保返回电路的低阻抗,DDR信号最好在相邻平面为地的信号平面上走线,如果不能保证所有的信号线都满足此要求,至少要保证数据和时钟走线。 避免在参考平面边缘走线:当DDR3信号的走线靠近参考平面的边缘时,保证走线与参考平面的边缘≥40Mil的间距。 避免换层走线以减少过孔的数量:由于DDR3的工作频率很高,时钟和数据信号速率一般都会达到400MHz以上,为了避免过孔的寄生电容和电感对信号质量的影响,需要通过控制换层的次数严格控制时钟线上过孔的数量。 保持信号线间距:当两个不同信号线之间距离过近时,会因电磁场的耦合导致串扰的产生。为了降低这种串扰,需要在不同信号线之间保持大于3倍走线宽度的间距,不要在反焊盘上走线。 电源设计要求 VTT电源孤岛尽可能靠近内存颗粒以及终端调节模块放置:由于很难在电源平面中单独为VTT电源划出一个完整的电源平面,因此一般的VTT电源都在PCB的信号层通过大面积铺铜划出一个电源孤岛作为VTT电源平面。VTT电源需要靠近产生该电源的终端调节模块以及消耗电流的DDR颗粒放置,通过减少走线的长度一方面避免因走线导致的电压跌落,另一方面避免各种噪声以及干扰信号通过走线耦合入电源。 终端调节模块的Sense引脚走线需要从VTT电源孤岛的中间引出:终端调节模块一般都有一个Sense引脚用于跟踪输出电压的变化,并根据变化进行动态调节。由于电源孤岛的面积比较大,电源孤岛上各处的电压也不尽相同,为了能够反映整体的电压水平即电源孤岛上电压的平均值,Sense管脚的走线需要从VTT电源孤岛的中间处引出。 降低Vref上的噪声:Vref上的噪声会增加数据选通和数据信号之间的skew并且降低电压裕度。为了降低这些噪声的干扰,需要加大Vref的走线宽度并且将Vref的走线与其它走线隔离。虽然Vref上的电流一般只有2mA左右,但是为了上述原因,一般需要保证其走线宽度不小于25Mil,同时Vref与其它信号线之间保持25Mil的距离。此外Vref要避免电源噪声的影响,Vref走线时应该以地平面作为参考平面。 不同信号线间走线长度的匹配 由于需要通过DQS信号对DQ进行采样,通过时钟信号对地址/控制信号进行采样,因此需要保证这些信号线间长度的匹配。 换层及过孔数量的控制 由于抑制过孔的寄生电容和电感对高速信号质量的影响。 信号线阻抗要求 通过控制信号线阻抗达到阻抗匹配、提高信号完整性的目的。 抑制信号线间干扰 通过加大不同信号线间的距离达到抑制信号线间干扰的目的。 信号走线设计要求

走线要求 时钟线 数据信号 地址/命令/控制信号 单端走线长度要求

1、同一组DQ信号线之间的长度差≤10Mil; 2、每组DQ信号线与其对应的DQS信号线的走线长度差≤10Mil以内; 3、不同组的数据线,误差≤100Mil; 以时钟为参考,走线长度与时钟信号的长度差≤100Mil; 差分走线长度要求 差分时钟线长度对内差≤5mil; 差分线内两根线间距保持一致,差分时钟线长度差保持在5mil以内,不同差分信号线对之间的长度差≤100mil;

换层及过孔 一段走线内过孔不超过两个;过孔相邻处加旁路电容或地过孔; 走线上过孔不超过两个

信号线阻抗匹配 差分阻抗75–100Ω,参考平面完整; 单端信号线阻抗可以控制在40-50Ω之间,参考平面完整; 2、差分阻抗75–10Ω,参考平面完整; 单端信号线阻抗可以控制在40-50Ω之间,参考平面完整; 信号间干扰抑制 与其它信号线保持4W以上; 同组信号线3W以上,不同组之间4W以上。 同组信号线3W以上,不同组之间4W以上。 其它要求 从第一片到最后一片DDR3颗粒之间的走线长度≤6000Mil;

1、按照数据线从低至高的顺序从第一片至最后一片颗粒进行布线,并且端接电阻放置在最后一片DDR颗粒之后; 2、从第一片到最后一片DDR3颗粒之间的走线长度≤6000Mil; 以上为针对DDR3一般性走线要求,可作为一般性参考。如使用DDR芯片有其自有要求则以芯片手册为准。 其他类型DDR走线等长,布局布线等要求可针对DDR3颗粒进行相对的调整,如果是DDR2等其他上代版本颗粒可相对DDR3的要求进行放宽,相对的DDR4等更先进颗粒可针对DDR3布局布线要求进行更加严格的把控,且每个颗粒厂商的要求不一致,在针对DDR颗粒进行布局布线时应严格按照芯片手册要求进行设计。 下图是DDR3与DDR4颗粒的走线的一个比较,各位设计人员可根据实际设计需求进行修改。

DDR3 DDR4 数据信号线 1,同组DQ与DQS等长保持在100mil内; 2,DQS差分线对内等长5mil内; 3,同组的DQ等长保持在30mil内; 1,同组DQ与DQS等长保持在50mil内 2,DQS差分线对内等长5mil内; 3,同组的DQ等长保持在10mil内; 时钟信号线 CLK差分线对内等长保持在5mil内; CLK差分线对内等长保持在5mil内; 地址,命令,控制信号线 地址,控制,命令参考CLK等长保持在200mil内 地址,控制,命令参考CLK等长保持在100mil内

例,下图为核心板LPDDR4颗粒等长规则设置: 从上图设计规则可看出,针对DDR4颗粒的等长,差分,阻抗设计要求和DDR3颗粒的设置是相类似的,因为他们都遵循DDR颗粒的设计原理,只是DDR4颗粒在等长等的设置要求上相较于DDR3版本来说会更加严格。

|

【本文地址】