| 电子技术基础(三) | 您所在的位置:网站首页 › 译码器的主要用途是什么 › 电子技术基础(三) |

电子技术基础(三)

|

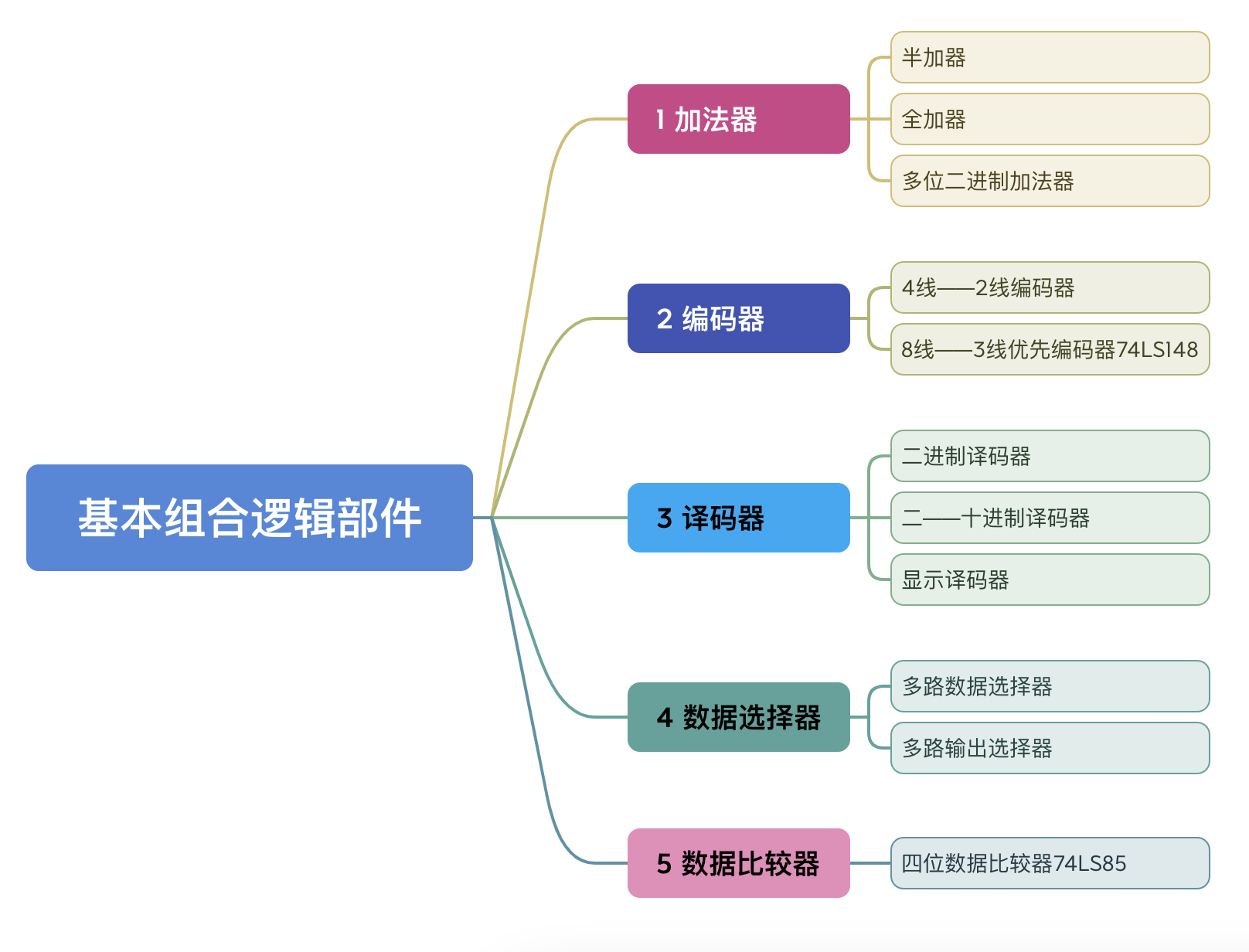

基本组合逻辑部件 有5种: 加法器、 编码器、 译码器、 数据选择器、 数据比较器。 口诀: 加 编 译 选 比

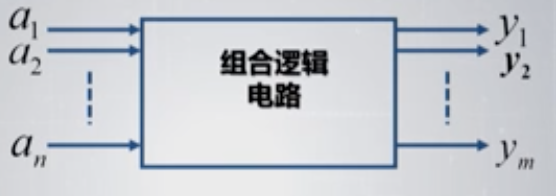

概述 一 组合逻辑电路的特点: 1. 从功能上, 任意时刻的输出取决于该时刻的输入 2. 从电路结构上, 没有记忆元件。 二 逻辑功能的描述 组合逻辑电路的框图

用逻辑函数式, 来表示

逻辑门符号 下面依次介绍5种组合逻辑器件 一. 加法器 1. 半加器半加器电路是数字电路中常用的运算电路之一, 其含义是只对本位的两个二进制数求和, 并向高位产生进位, 不考虑低位的进位。 简单地说,不考虑低位的进位 称为半加器。设A、B 代表两个本位相加的二进制数, S代表本位和、C代表向高位的进位。 半加器算式如左:

半加器的真值表 输 入 输 出 A BSC 0 000011010101101

可以看出, S的结果正好为异或的结果, C的结果为 与运算的结果 其逻辑电路如图6.4.1所示, 逻辑符号如图6.4.2所示

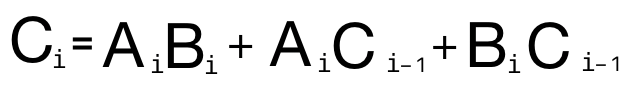

注意: 半加器符号里 CO 指 进位输出, O 表示 Output 输出 总结: 半加器只能应用于 两个 都只是一位的二进制相加, 不能用于多位的二进制数 的相加!! 2 全加器 全加器是指两个多位二进制数相加是, 第 i 位的被加数 写出逻辑函数表达式为

全加器符号为:

3. 多位二进制加法器 全加器只能实现一位二进制数的加法, 要实现多位二进制的加法, 可用多个一位全加器级联而实现, 将低位片的进位输出信号接到高位片的进位输入端。 四位二进制数的加法电路如下所示

为什么需要编码器? 数字系统只能处理二进制信息,人们习惯采用十进制。 因此需要一种将十进制数或字符转换成二进制代码的电路, 这种电路称为编码器。 下表6.4.3 给出了四个输入端

常用的编码器有: 10线——4线优先编码器74LS147, 8线——3线优先编码器74LS148 三 译码器a. 实现译码功能的电路称作译码器, b. 将二进制翻译成十进制的译码器称为二——十进制译码器, c. 用于显示的译码器称为显示译码器。 3.1 二进制译码器(最小项译码器) 例如: 3位二进制(3线——8线) 译码器框图和真值表如下所示:

这里, 3线 指输入, 8线指输出, 对应的真值表如下

从真值表,可得出结论: 最小项译码器 特点: n线——2ⁿ线; 输出仅有1个有效信号对应。 例如 2-4 (读作2线—4线), 3-8(读作3线—8线), 4-16(读作4线—16线) |

【本文地址】

和加数

和加数  以及来自相邻低位的进位位

以及来自相邻低位的进位位  三者相加, 其结果得到本位和以及向相邻高位的进位

三者相加, 其结果得到本位和以及向相邻高位的进位  .

.