| 【基础知识】~ FIFO | 您所在的位置:网站首页 › 精心挑选造句二年级 › 【基础知识】~ FIFO |

【基础知识】~ FIFO

|

本章目录:

1. 了解FIFO1.1 定义1.2 FIFO有什么用处?1.3 FIFO的参数有哪些?

2. 同步FIFO2.1 原理2.2 代码

3. 异步FIFO3.1 原理3.2 最小深度计算3.2.1 需要用到FIFO最小深度的情况3.2.2 fa>fb并且没有空闲(IDLE)周期3.2.3 fa>fb并且有空闲(IDLE)周期3.2.4 fa

1. 了解FIFO

1.1 定义

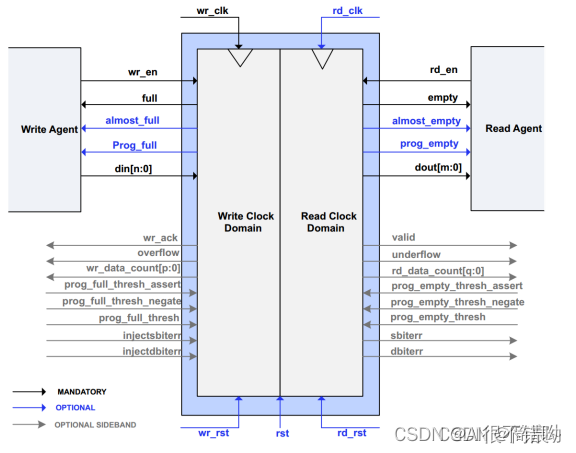

FIFO(First In First Out),即先进先出队列。FIFO存储器是一个先入先出的双口缓冲器,即第一个进入其内的数据第一个被移出,其中一个是存储器的输入口,另一个口是存储器的输出口。对于单片FIFO来说,主要有两种结构:触发导向结构和零导向传输结构。触发导向传输结构的FIFO是由寄存器阵列构成的,零导向传输结构的FIFO是由具有读和写地址指针的双口RAM构成。 FPGA 使用的 FIFO 一般指的是对数据的存储具有先进先出特性的一个缓存器,常被用于数据的缓存,或者高速异步数据的交互也即所谓的跨时钟域信号传递。它与 FPGA 内部的 RAM 和 ROM 的区别是没有外部读写地址线,采取顺序写入数据,顺序读出数据的方式,使用起来简单方便,由此带来的缺点就是不能像 RAM 和 ROM 那样可以由地址线决定读取或写入某个指定的地址。 根据 FIFO 工作的时钟域,可以将 FIFO 分为同步 FIFO 和异步 FIFO。同步 FIFO 是指读时钟和写时钟为同一个时钟,在时钟沿来临时同时发生读写操作。异步 FIFO 是指读写时钟不一致,读写时钟是互相独立的。 Xilinx 的 FIFO IP 核可以被配置为同步 FIFO 或异步 FIFO,其信号框图如下图所示。从图中可以了解到,当被配置为同步 FIFO 时,只使用 wr_clk,所有的输入输出信号都同步于 wr_clk 信号。而当被配置为异步 FIFO 时,写端口和读端口分别有独立的时钟,所有与写相关的信号都是同步于写时钟 wr_clk,所有与读相关的信号都是同步于读时钟 rd_clk。 宽度:一次读写操作的数据位 深度:可以存储的 N 位数据的数目(宽度为 N) 满标志: full。FIFO 已满时,由 FIFO 的状态电路送出的信号,阻止 FIFO 写操作 空标志: empty。FIFO 已空时,由 FIFO 的状态电路送出的信号,阻止 FIFO 读操作 读时钟:读操作所遵循的时钟 写时钟:写操作所遵循的时钟 2. 同步FIFO 2.1 原理典型同步FIFO由三部分组成:FIFO写控制逻辑、FIFO读控制逻辑、FIFO存储实体。 FIFO写控制逻辑主要功能:产生FIFO写地址、写有效信号,同时产生FIFO写满、写错等状态信号; FIFO读控制逻辑主要功能:产生FIFO读地址、读有效信号,同时产生FIFO读空、读错等状态信号。 FIFO读写过程的地址控制如下图所示: 当FIFO初始化(复位)时,fifo_write_addr与fifo_read_addr同指到0x0,此时FIFO处于空状态; 当FIFO进行写操作时,fifo_write_addr递增(增加到FIFO DEPTH时回绕),与fifo_read_addr错开,此时FIFO处于非空状态; 当FIFO进行读操作时,fifo_read_addr递增。FIFO空满状态产生: 为产生FIFO空满标志,引入Count 计数器,用于指示FIFO内部存储数据个数; 当只有写操作时,Count加1;只有读操作时,Count减1;其它情况下,保持不变; Count为0时,说明FIFO为空,fifo_empty置位; Count等于FIFO_DEPTH时,说明FIFO已满,fifo_full置位。 2.2 代码参照博客 3. 异步FIFO 3.1 原理异步FIFO的实现通常是利用双口RAM和读写地址产生模块来实现的。FIFO的接口包括异步的写时钟(wr_clk)和读时钟(rd_clk)、与写时钟同步的写有效(wr_en)和写数据(wr_data)、与读时钟同步的读有效(rd_en)和读数据(rd_data)。为了实现正确的读写和避免FIFO的上溢或下溢,通常还应该给出与读时钟和写时钟同步的FIFO的空标志(empty)和满标志(full)以禁止读写操作。 写地址产生模块还根据读地址和写地址关系产生FIFO的满标志。当wren有效时,若写地址+2=读地址时,full为1;当wren无效时,若写地址+ 1=读地址时,full为1。读地址产生模块还根据读地址和写地址的差产生FIFO的空标志。当rden有效时,若写地址-1=读地址时,empty为 1;当rden无效时,若写地址=读地址时,empty为1。按照以上方式产生标志信号是为了提前一个时钟周期产生对应的标志信号。 由于空标志和满标志控制了FIFO的操作,因此标志错误会引起操作的错误。如上所述,标志的产生是通过对读写地址的比较产生的,当读写时钟完全异步时,对读写地址进行比较时,可能得出错误的结果。例如,在读地址变化过程中,由于读地址的各位变化并不同步,计算读写地址的差值,可能产生错误的差值,导致产生错误的满标志信号。若将未满标志置为满标志时,可能降低了应用的性能,降低写数据速率;而将满置标志置为未满时,执行一次写操作,则可能产生溢出错误,这对于实际应用来说是绝对应该避免的。空标志信号的产生也可能产生类似的错误。 3.2 最小深度计算

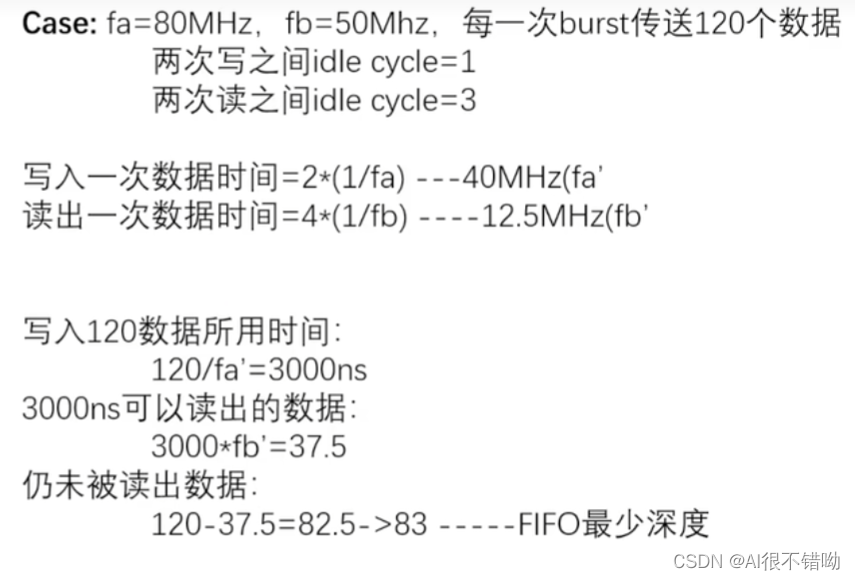

大概有以下四种情况:(以上图为例) fa>fb并且没有空闲(IDLE)周期;fa>fb并且有空闲(IDLE)周期;fafb并且有空闲(IDLE)周期

这里遇到一个问题,反复查看代码,怎么也找不出来,哭了!!! 最后一查,实例化RAM的时候,有个线连错了,最后通过,奥里给!!! ========================================================================================== 参考文献参考FIFO深度 声明本人所有系列的文章,仅供学习,不可商用,如有侵权,请告知,立删!!! 本人主要是记录学习过程,以供自己回头复习,再就是提供给后人参考,不喜勿喷!!! 如果觉得对你有用的话,记得收藏+评论!!! |

【本文地址】

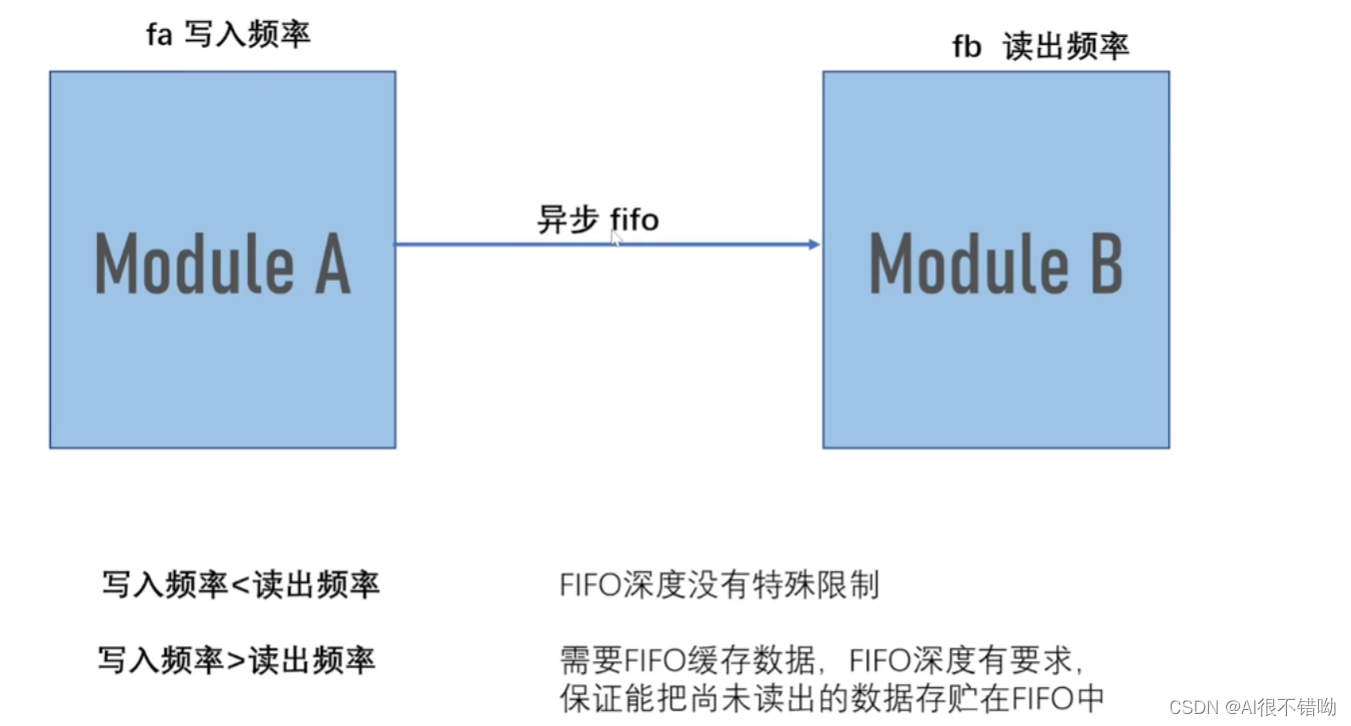

对于异步FIFO而言,无非就是写入频率大于或者小于读出频率呗!然而,对于写入频率 小于 读出频率,意味着写的慢,读的快,会怎样?那肯定是对你的FIFO深度没有要求了呀!你没了我就不读了呗。重要的是看另一种情况:写入大于读出,那就需要FIFO进行储存,既然储存,那肯定得有深度要求!

对于异步FIFO而言,无非就是写入频率大于或者小于读出频率呗!然而,对于写入频率 小于 读出频率,意味着写的慢,读的快,会怎样?那肯定是对你的FIFO深度没有要求了呀!你没了我就不读了呗。重要的是看另一种情况:写入大于读出,那就需要FIFO进行储存,既然储存,那肯定得有深度要求!