| 数字电路之RS触发器(与非门) | 您所在的位置:网站首页 › 由或非门组成的锁存器和输入端信号 › 数字电路之RS触发器(与非门) |

数字电路之RS触发器(与非门)

|

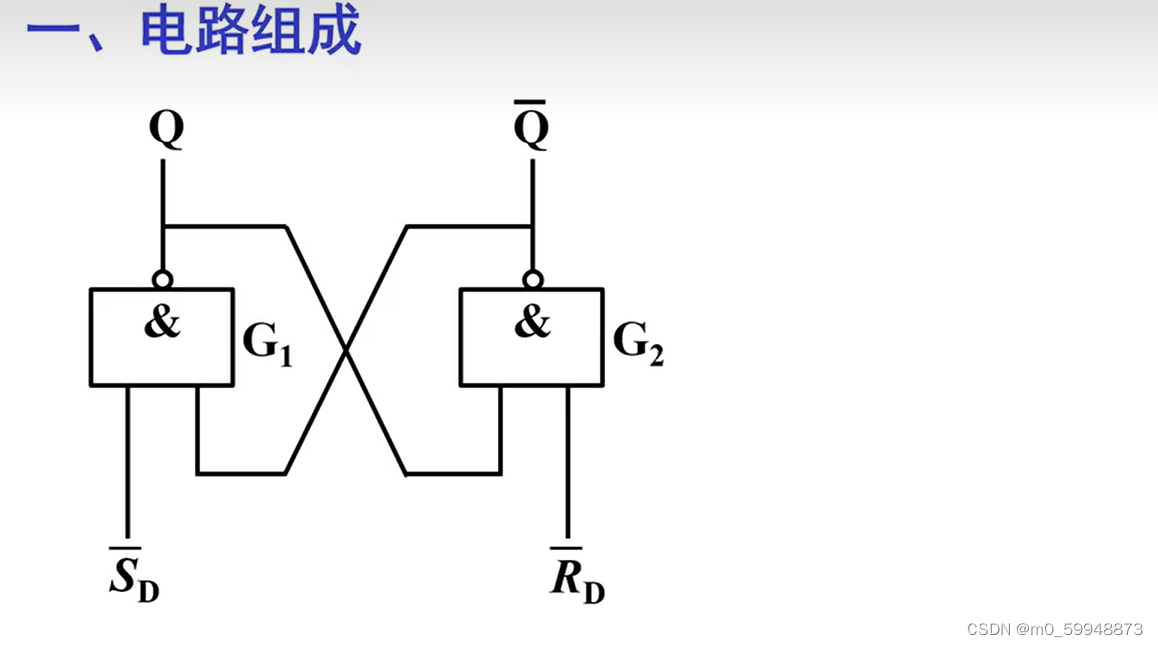

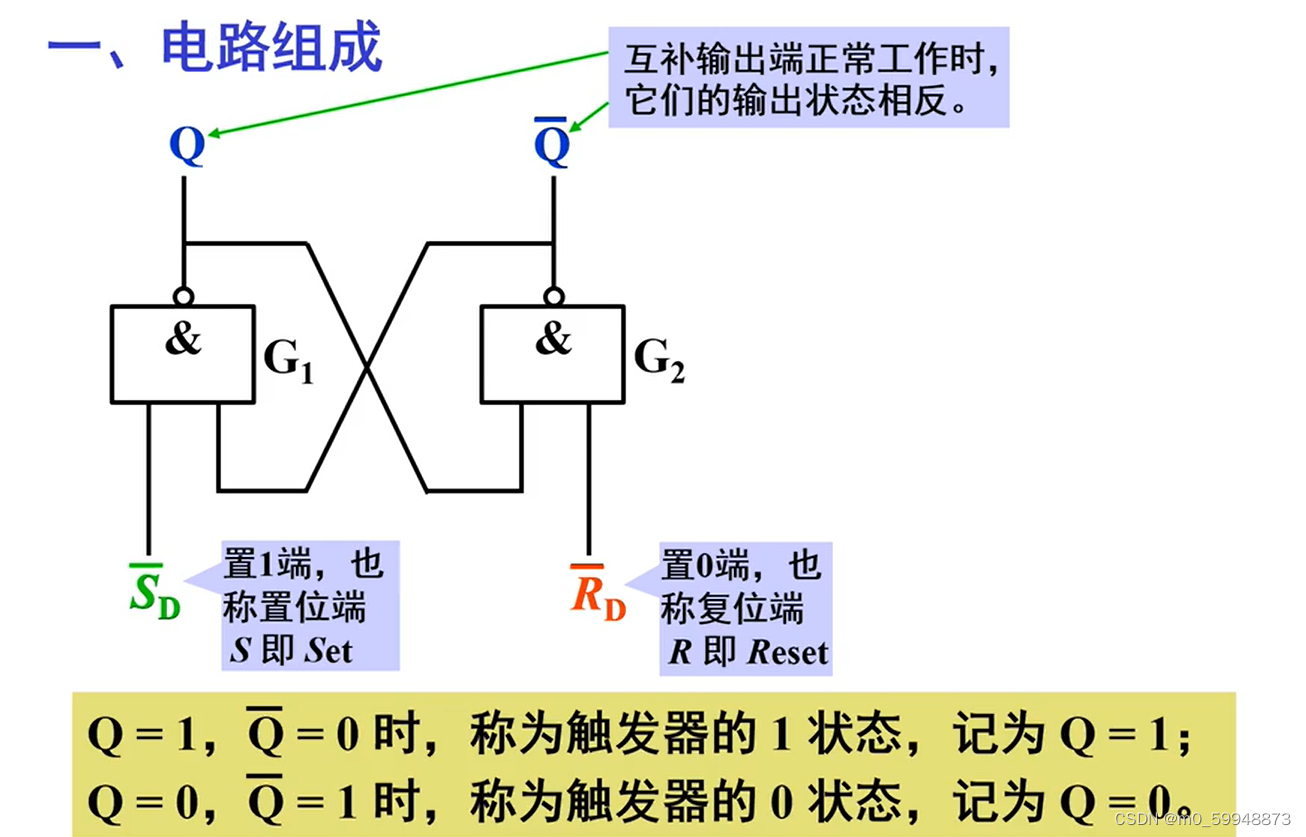

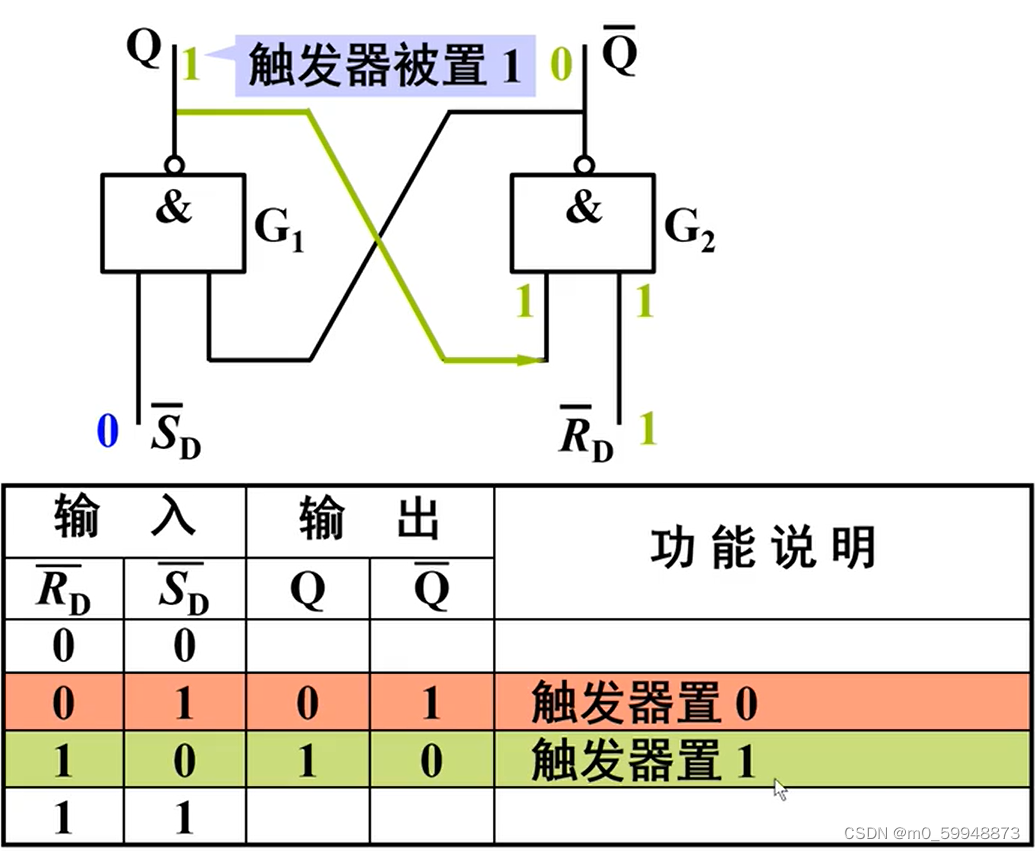

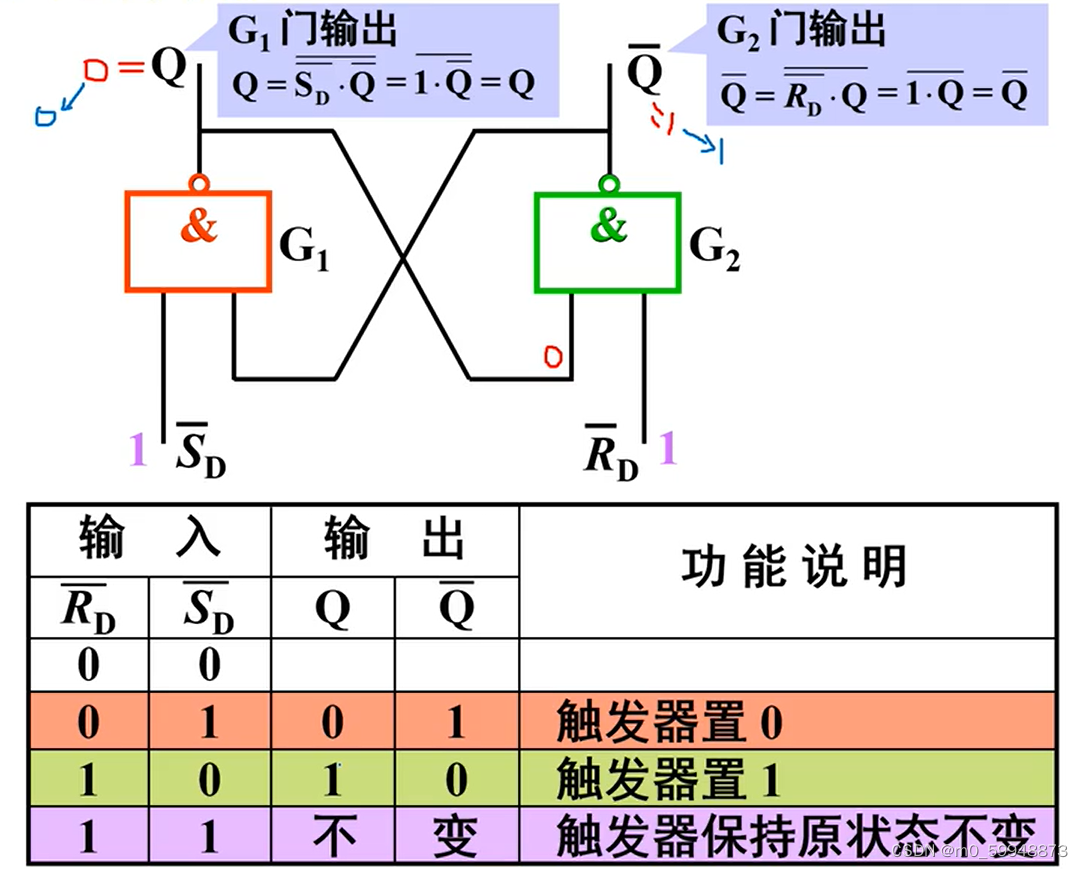

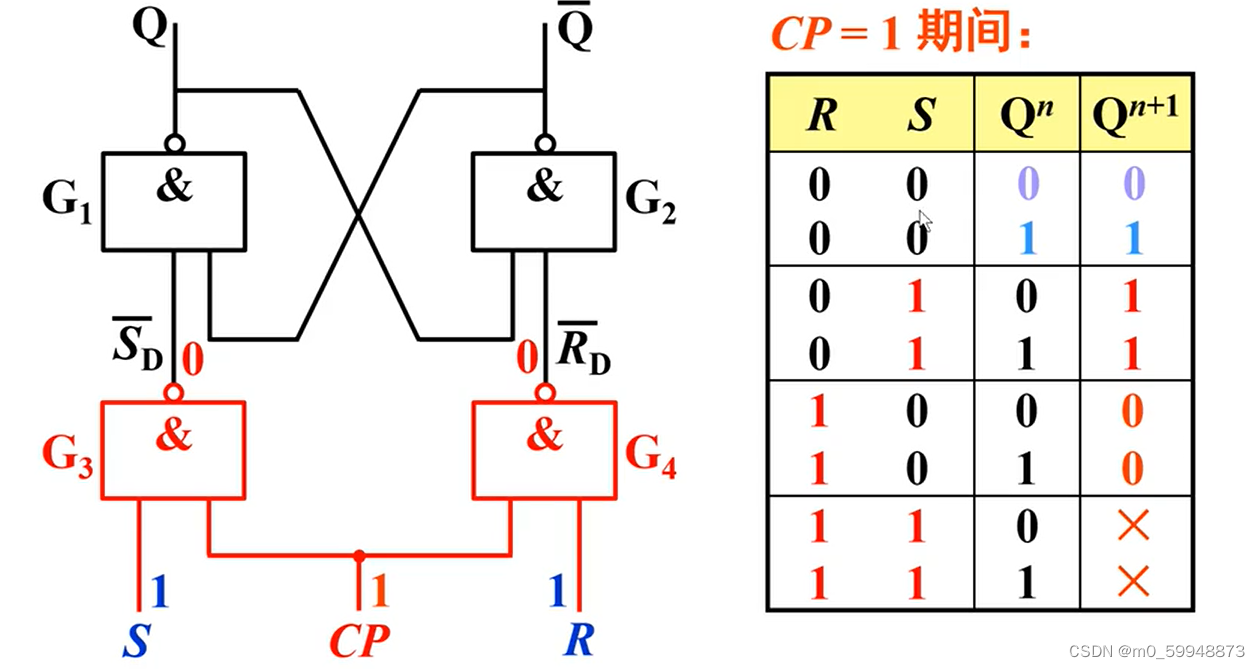

本文相关图片转载自数电53-与非门构成的基本RS触发器_哔哩哔哩_bilibili RS触发器电路结构:

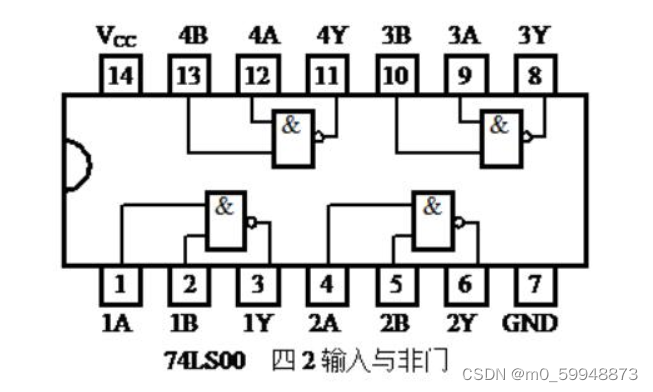

RS触发器由两个二输入与非门组成,在实验室中可以使用74LS00搭建

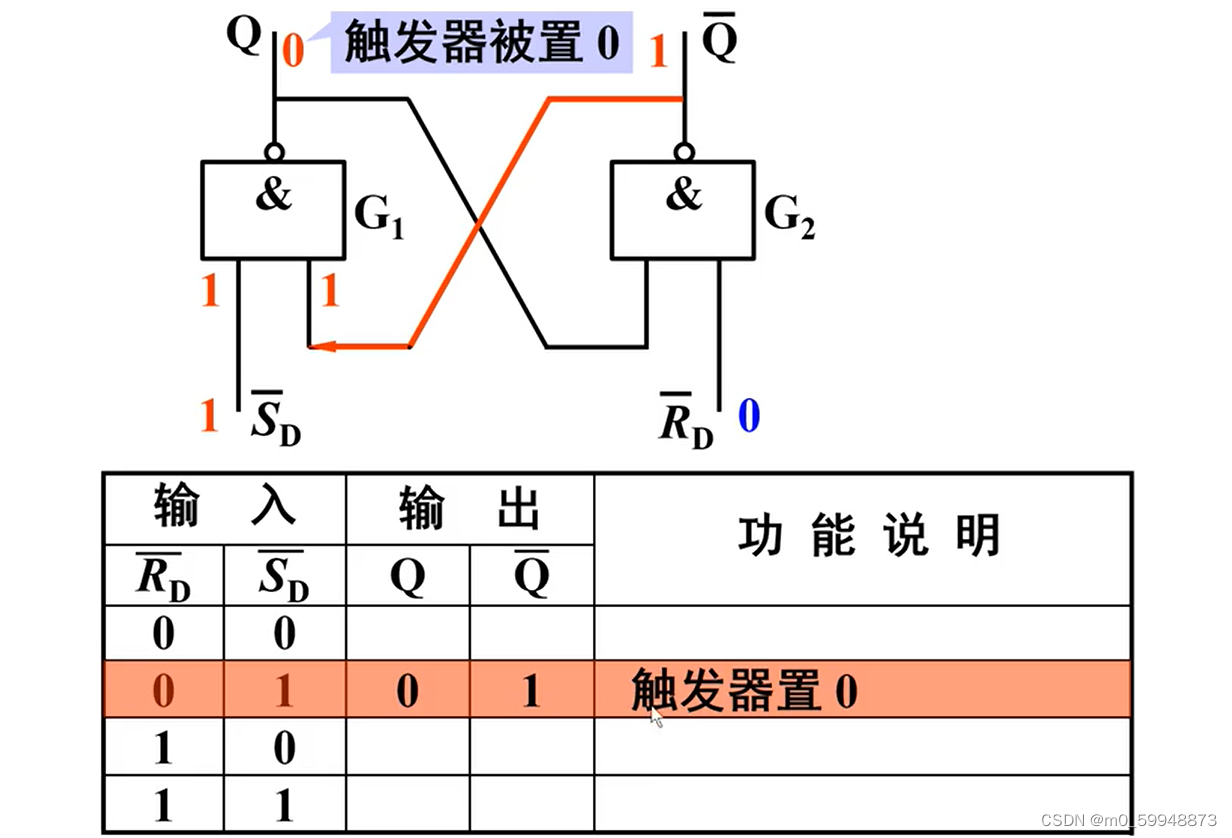

S端是置1端,R端是置0端(这很重要),后面真值表会有分析

与非门input有0,则output为1

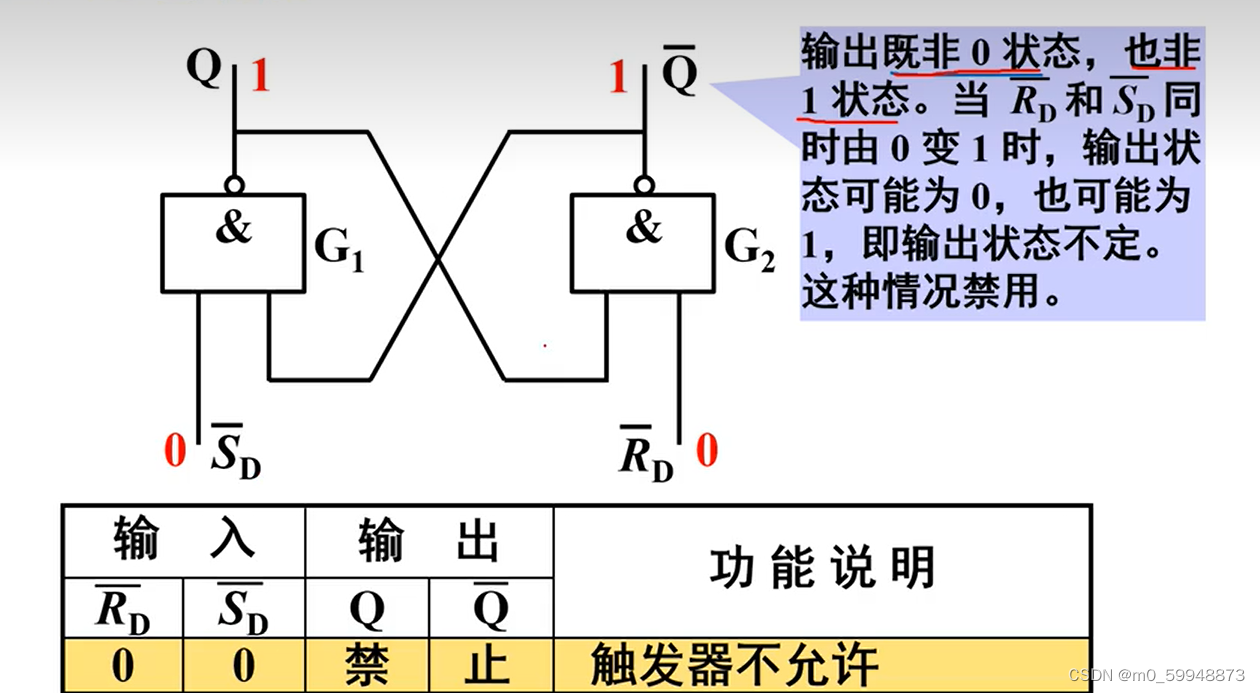

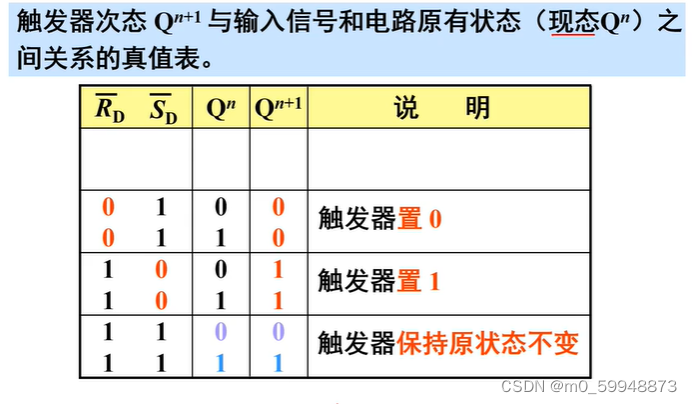

———————————————————分割线————————————————————— ———————————————————分割线———————————————————— ———————————————————分割线———————————————————— 两输入端不能同时为0 特性表

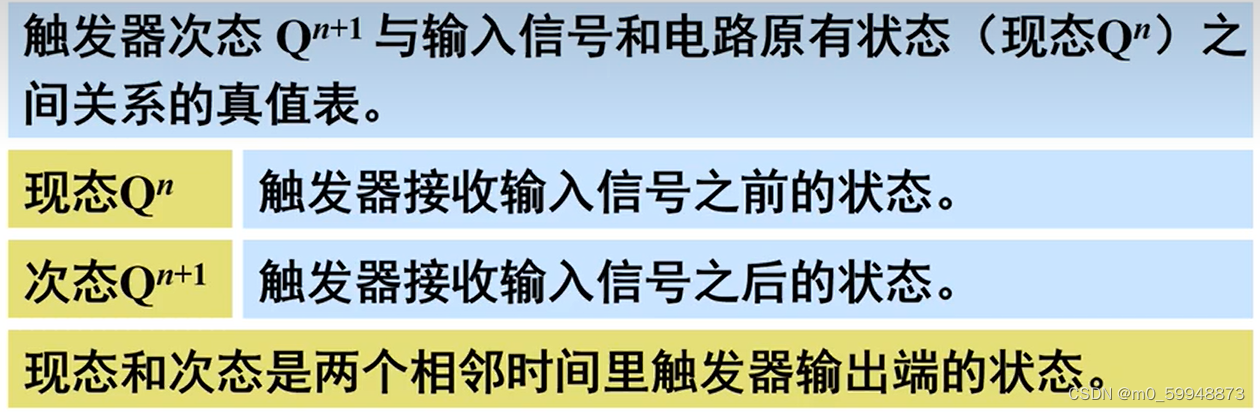

上面介绍完了基本RS触发器,就让我们再看一下同步RS触发器

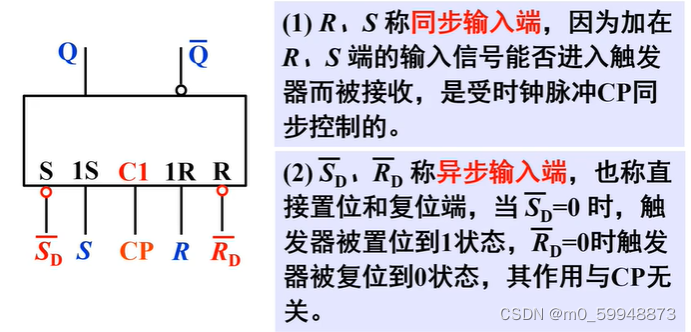

R、S称之为同步输入端,这是因为R、S端的输入信号能否进入触发器而被接收,是是受时钟CP同步控制的 2、

异步输入端是用来预置触发器的初始状态,或者在工作中强行置位和复位触发器触发器, 不工作时, ———————————————————分割线———————————————————— 同步RS触发器的Verilog-HDL描述 module SY_SR_FF( input clk, input R, input S, output Q, output QB ); reg Q; assign QB=~Q; always @(posedge clk)begin case({R,S}) 2'b01:Q |

【本文地址】

公司简介

联系我们