| 《版图笔记》分享 EETOP网友 bearlin12 在 EETOP 博客分享了关于 《版图笔记》的连载,现分享给大家。 博客地址:网页链... | 您所在的位置:网站首页 › 版图dummy管 › 《版图笔记》分享 EETOP网友 bearlin12 在 EETOP 博客分享了关于 《版图笔记》的连载,现分享给大家。 博客地址:网页链... |

《版图笔记》分享 EETOP网友 bearlin12 在 EETOP 博客分享了关于 《版图笔记》的连载,现分享给大家。 博客地址:网页链...

|

来源:雪球App,作者: EETOP,(https://xueqiu.com/4463035516/132182001)

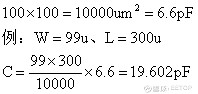

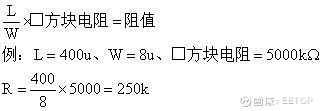

EETOP网友 bearlin12 在 EETOP 博客分享了关于 《版图笔记》的连载,现分享给大家。 博客地址:网页链接 《版图笔记》Part 1 芯愿景导入电路 ① 在Cadence下: File→Export→EDIF 200...→Browe选择文件→Output File 改名→OK 导出edif ,out后叫经理导入到共享,再从共享拉到桌面。 ② 在ChipAnalyzer下: 文件→导出EDIF 200网表格式。 在D/Chiplogic Family/ChipAnalyzer/Bin下找到导出的网表文件。 在D/Chiplogic Family/ChipMaster/Project下复制多一个analogLib1,再建多一个数字电路的文件夹,只要Symbol。 ③ 在ChipMaster下: 新建单元库→导入***.out文件→删除多余单元→再导入***.edif文件→打开顶层文件。 设置顶层文件(右键→设置为顶层文件)→电路→显示线网列表窗口→全选后右键→自动标号化长引线...→填写引线长度阈值→回到顶层文件→调整间距→导出EDIF 200→放到共享上叫经理导入Cadence。 (去掉提图中的悬空线头:工具→选项→单元数阈值:0) ④ 在Cadence下: 导入EDIF 200。 设置点亮线加粗 CIW窗口的Tools→Display Resource Manager...→Edit→Layers下选LSW→分别设置y1 drawing,y2 drawing,y3 drawing……的Line Style。 查找单元器件(电路) Edit→Search→Final 长出nplus\pplus(铝栅) (先画上area层)Verify→DRC→设置Rules File文件(gate.rul)→OK 加载技术文件 Tools→Technology File Manager...→Attach... 回原点 Edit→other→Move Origin 基于Dracula的LVS ① 建立文件 单独建一个run LVS文件夹,在这个文件夹里导入版图的***.gds文件;电路的***.cdl文件;复制好规则文件***.lvs ① vi ***.lvs改写两项 PRIMARY=版图文件名; INDISK=版图文件名.gds; ② LOGLVS →Cir netlist(cdl文件名)→con ...(电路名)→x→PDRACULA→/g ***.lvs→/f→jxrun.com ③ vi lvs.lvs(打开lvs文件,检查错误) 查找Dracula的LVS错误 ① Tools→Dracula Interactive,会出现DRC、LVS工具栏 ② LVS→Setup... ③ 在Dracula Data Path中输出LVS的路径,会跳出View LVS选项卡 *Dracula修改版图后可直接jxrun.com跑LVS,修改电路需重新开始跑LVS。 制成cell Edit→Hierarchy→Make Cell... 打散cell Edit→Hierarchy→Flatten... 切角 Edit→Other→Modify Corner...→chamfer(角) 进入模块编辑 Shift+X 退出:shift+B 看到总模块的情况下编辑指定模块 X 退出:shift+B 生长层 Create→Layer Generation...→在这层的基础上 GROW BY距离 =需要生长层 全范围缩小增大 Edit→other→Size→设置Size Value 电容算法

电阻算法

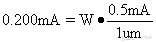

取消查看DRC错误 Verify→Makes→Delete All...→OK Library Manger分类 勾选Show Category→Category下建TOP 从其他路径下加载Library Library Manager下Edit→Library Path→OK→Edit→Add Library→选择Library→Save AS 环线 create→Multipart Path→F3 Subrectangle:(中间孔的设置) Layer:cont Begin offset:-0.3(孔到包围线顶部距离) End offset:-0.3(孔到包围线底部距离) Width:0.8(孔的宽度) Length:0.8(长度) Space:1.2(孔与孔的距离) Separation:-1(孔中心到环中心线的距离,多排孔改这个距离即可) Gap:minimum Fustification:center(中心对称) Enclosure Subpath:(外包层设置) Layer:pplus Begin offset:0.5 Enclosure:-0.5 End offset:0.5 →Apply→save.Template 版图里查找标号 (要有text层!) Shift+S→Search for: label→Add Criteria→text==标号→勾选Zoom To Figure→Apply或者next 识别线名 (在Dracula LVS时)View LVS→选中线→Cursor Pick 从Library里移除或引进的Library (只看不见,不删除!) Library Manager下的Edit→Library Path→OK→选中其中一个Library→Edit→Remove Library Definition 替换电阻电容(电路) 在Library Manager下复制analogLib的电阻电容。 在CIW下:Tools→CDF→Edit→CDF Type:Base→Browse→选择复制到的Library下的电阻电容→下拉到Simulation Information→Edit→Choose Simulator:auCdl→修改Malel Name 做Pcell基本操作 添加图层:LSW下Edit→Set Valid Layers...→选Stretch dgþ→OK 版图窗口下:Tools→Pcell→Stretch→【Stretch in X(X方向拉伸)、Stretch in Y(Y方向拉伸)、Qualify(指定对象)、Modify(修改)、Redefine..(重新定义)】 Stretch in X——沿X方向拉伸(垂线) Stretch in Y——沿Y方向拉伸(横线) 查看:Pcell→Parameters→Summarize 修改:Pcell→Stretch→Modify→选择Stretch线进行修改 保存:Pcell→Compile→To Pcell或点保存 查看版图里的库 Shift+T 查找版图DRC错误 Verify→Markers→Find...→勾选Zoom To Markers 版图复制Layout里自动变换成当前Library 复制Layout→To下的Library改成目标Library→勾选Copy Hierarchical 和Update Instances→OK→选Overwirte All(覆盖)或Fix Erros(命名)→OK 修改Netlist 搜索:/NP→(大写N向上翻,小写n向下翻)查找所有NP→:%/NP/PM/g→:wq range 指范围,1,7指第一行至第七行,1,$指从第一行至最后一行,就是整篇文章, 也可以%代替。%是目前编辑的文章,#是前一次编辑的文章。 pattern 指要被换掉的字串,可以用regexp来表示。 string 将Pattern由String所取代 c Confirm,每次替换前询问 e 不显示error g globe,不询问,整行替换前询问 i ignore不分大小写。 LVS跳线设置 LVS Options→Connect→勾选Connet nets with...(:) 打开Calibre运行LVS、DRC 在/home/lcm 0315下Vi .bashrc→复制/user/local/eda/……/license.dat到/home/lcm0315→回车运行 《版图笔记》Part 2 华润工艺转换方正工艺 在做好的Library下:cell复制cell_copy→打散cell_copy→T2改成A2→新建Library→再复制打散的cell_copy到新Library下→在cell_copy上生长gate.rul(最好单独一层)→跑DRC→根据错误,在原Library的cell里改错→再重复转换步骤,如此往复,直到修改完成。 转换工艺文件 在新建Library下复制方正工艺的三个文件(diva.rul、gate.rul、techfile.cds)。技术加载本地技术文件。 全部打散 在版图可见下全选→Edit→Hierarchy→Flatten→设置Flatten Mode:displayed levelsþ→Flatten Pcellsþ其它不用勾选→OK 创建接触孔(Pcell) 规则(Pcont_08):铝线包孔0.3u,孔间距1.2u,孔大小为0.8ux0.8u 设X、Y方向孔的个数:XM为X方向孔的参数,YM为Y方向孔的参数 设置复制属性: ① 设置孔的参数: 选中孔层(cont)→Pcell→Repetition→Repeat in X and Y X Stepping Distance:2 (孔间距+孔大小) Y Stepping Distance:2 Number of X Repetition:XM Number of Y Repetition:YM Adjustment to X Stretch:((fix(pcRepeat X)-1*pcStepX) Adjustment to Y Stretch:((fix(pcRepeat Y)-1*pcStepY) ② 设置控制线(让铝随孔的增加自动增大) 分别选择Stretch in X和Stretch in Y,两条控制线分别穿过孔的中心点 设置X的参数:(控制线垂直画) Pcell→Stretch→Stretch in X...→画线→双击或Enter→Name or Express for Stretch:((XM*2)-1.2)【(XM*步长)-孔间距】 设置Y的参数:(控制线水平画) Pcell→Stretch→Stretch in Y...→画线→双击或Enter→Name or Express for Stretch:((YM*2)-1.2)【(YM*步长)-孔间距】 (不能勾选Stretch Horizontally Repeated Figures!) ③ 设置XM和YM的最小值 Pcell→Parameters→Edit Parameters... 计算电流密度 一条导线所能承受的电流(I)等于金属线的宽度x承受电流常数(In),这个常数可以在工艺手册中查到。

例如: 闪退cell被锁 如果闪退后cell被锁,进入cell的路径下,删掉layout.cdb.cdslck文件。原理图同理。 什么情况不形成二极管 PN结形成二极管。P的电流>N的电流,正向二极管。N的电流 不同工艺替换(层次替换) 版图layout下calibre→Setup→Layout Export→Layout Map File:……/gds.tbl 导出gds→加载gds→加载工艺 (加载gds要写Run Directory Input File、Library Name Top Cell Name!) (要有techfile.cds才可以转换工艺!) gds.tbl文件编写 当前工艺层 层次属性 更换之后层次号 data type BN drawing 1 0 TO drawing 12 0 TB drawing 10 0 GT drawing 16 0 ………………………………………………………… ………………………………………………………… Cadence中将Dracula规则文件转换为Calibre文件 (旧版本)输入命令:drac_cvt drac.file calibre.file 画线自带标尺 Create→Microwave→Trl (F3设置宽度) Calibre SVS(在bash下) 输入Calibre -gui打开SVS→选LVS→Input选项卡选Netlist VS Netlist→选中两个电路(注:先导出两个Netlist!)→Run (或者在版图下打开Calibre) Chiplogic layeditor提版图 ① 在工程选项框内的工作区右键“创建工作区” 填写名称:layout→确定 设置格点:工具→选项...→显示→设置所需格点 ② 在版图层框中右键“添加版图层” 填写层名:ACT GDS号:2 尺寸:0.8 显示:随意 勾选可显示,可选中,显示边框 (注:GDS号必须与所画工艺文件内的GDS一致,尺寸不为0) 高级选项卡中设置连接孔层的定义 一定要添加“VA1、PLCNT、PCNT、NCNT、VA2”层 ③ 添加完版图层后导出版图层,便于以后相同工艺使用 也可以用以前导出的版图层(文件→导入→版图层定义...) 文件→导出→版图层定义...→浏览→选好位置写好文件名→保存→确定(导出了**.tf) ④ 编写映射文件map.txt 桌面新建一个.txt的文件,进入编写: TNSTANCE INSTANCE CONNECTOR CONNECTOR LINE1 PL1 LINE2 ME1 LINE3 MET VIA1 VA1 VIA2 VA2 ... ... 其他根据转换时报的错误添加 ⑤ 转换工作 工程→转投工作区 源Analyzer工作区名称:下拉选择 版图层的映射文件:点击浏览选择写好的map.txt文件→确定 ⑥ 如果转换的是有金属线的版图,再进行自理 1、导出脚本文件:文件→导出脚本格式 (注:导出时只选择“导出单元模板”和“导出单元实例”) 2、在layeditior 里新建一个工作区:layout2,将导出的脚本文件导入。 (此操作基于已经在Analyzer中提好了电路!) 版图数据转换 ① 导出GDSII文件 文件→导出→GDSII...→浏览→选择导出位置并写出文件名→填写顶层单元名称TOP→格点0.05→坐标原点设置:指以整个芯片左上角的原点→¨不导出基本单元的内容,直接引用cadence库中的单元→þ在版图层TEMPLATE上导出单元模板的矩形边框→确定 ② 导入GDSII文件 文件→导入→GDSII...→浏览→选择.gds文件→þ导入顶层单元的版图。顶层单元名称:TOP→þ覆盖已有的单元内部版图→确定 显示版图: 工具→选项→常规→þ显示单元内部版图 注:Chiplogice里没有的单元,不能在Cadence里建,否则再导回Chiplogice会出错。在Cadence放器件,一定要打散,且删掉绿框! Cadence排列器件 ① 选中要排列的器件→Edit→Other→Align→Selection Mode:选择Set reference to align preselected objects→Alignment Direction(二选一):Horizontal(水平)Vertical(垂直)→Align Using:Component BBOX→Spacings:设置距离(器件末端与第2个前端距离)→点击Set New Reference→不要关闭窗口→在layout中点一下 ② Copy法: 选中器件→按C→按F3→设置ROW:Columns:X:Y:的值→Hide 添加层次 在LSW下的Edit→Set Valid Layers...→勾选层次→OK Chiplogic版图操作——排列方法 按C复制→选中单元→将复制单元挪到量好的位置→再按空格键,就能等距离排列了。 Chiplogic版图操作——修改单元内部版图 选中单元右键→打散单元内部版图→修改→全选→Ctrl+A→OK 点亮线Metal1 to Metal2 Connectivity→Mark Net→F3→Via Layers Used by Mark Net:Select Via Layers→Add A1 W2 T2→把A1 W2 T2 up到第一→OK→F3→最后设置Mark Net Hierarchy Range:Current to bottom 版图label查找 Shift+S→Search for“label”in“current to bottom”→点Add Criteria→text==“”→勾选Zoom To Figure→Apply→Next 版图查找坐标 ① 先在版图上按K,先别点击 ② 然后在CIW界面输入坐标,中间用冒号隔开 ③ 在版图上能看到有尺子在那里 LVL(旧版本) 先导出两个.gds文件→在bash的工作状态下输入:compare _gds A.gds A B.gds B diff.db -XOR→查看Calbre -rve diff.db SVS 先导出两Netlist文件→在bash的工作状态下输入:calibre -gui -lvs→选lvs工艺规则文件,Netlist1,Netlist2→设置好后Run LVS LVL(新版本) 先导出两个.gds文件→在bash的工作状态下输入:dbdiff -system GDS -design A.gds A -refdesign B.gds B -write_xor_rules rules.xor _compare text→生成rules.xor文件→再运行:Calibre -drc rules.xor→查看:rules .xor .summary文件 Chiplogic 分模块 在TOP窗口记录4个坐标→创建工作区→名称:Block→取消勾选整个芯片→输入坐标→确定 Chiplogic层次化 在Block窗口下→合并工作区→目标工作区:TOP 原理图与Layout关联:Layout XL 新建与电路一样名字的layout→Tools→layout XL→Design→Gen From Source...→设置为金属1层→只勾选Instances→OK 取消关联 Tools→layout Chiplogic导出脚本 文件→导出→脚本文件 Chiplogic工作区范围更改 在工程选项卡里,右击工作区→工作区属性 直接生成器件存在的问题 ① 无法直接生成版图 重启,重新Attach技术文件,确保电路与版图的技术文件为同一个PDK库。 ② 无法引用已经完成的小模块 需要在LAY库下将电路库的电路复制过来,才能生成LAY库下的模块 《版图笔记》Part 5

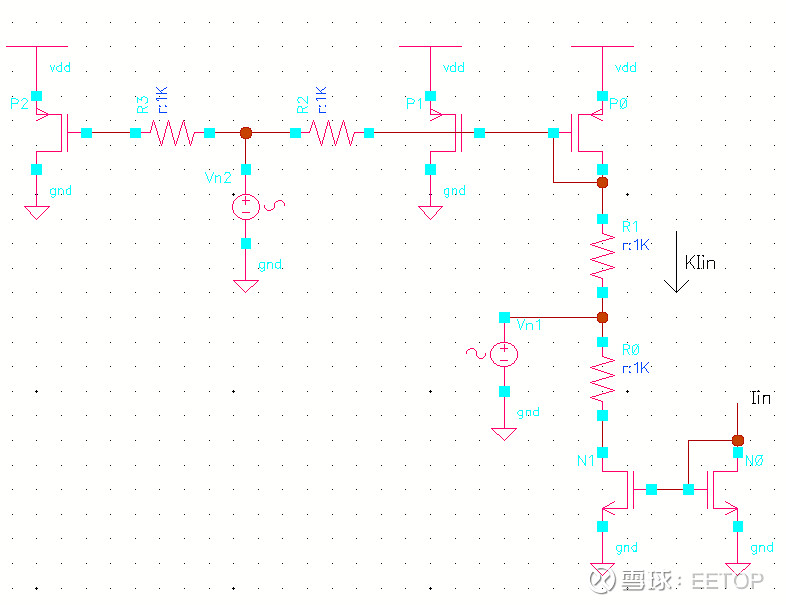

如图所示,假设在版图中N1和P2相隔比较远,需要走一段比较远的距离,这时候可以有两种选择: ① P0、P1、P2画在一起,N1的D端通过长金属连接到P0的S端、P1和P2的G端,这称为电流传输,因为长金属流过的是电流信号。 ② P0、P1、N1画在一起,P0、P1的G端通过长金属连接到P2的G端,这称为电压传输,因为长金属流过的是电压信号。 假设长金属在传输过程中,均受到侧壁电容耦合过来的噪声电压,分别用Vn1和Vn2来模拟,可以看到,电压传输模式中Vn2 P2的栅压,使其电流发生变化,而电流传输模式中Vn1虽然使得N1的漏电压发生变化,但P0的栅压只跟N1电流有关,P2仍复制N1的电流,受到的影响明显比前一种画法小。 信号线的动静相间 动态信号线,如时钟线,快速变化的数据线,如果靠得太近,线与线之间的侧壁电容会大于我们的想象,由此电容耦合产生的干扰是比较严重的干扰。如果动态信号线两侧是静态信号线,甚至是地线或电源线,它们受到的干扰就会小得多,尤其是两侧用同层金属的地线夹住,会起到明显的保护作用。 在条件不允许的情况下,比如地方不够,两边没办法拉出两根地线,则尽量做到动态信号线和静态信号线想到交叠的方式走线。比如,一根时钟线,旁边是一根运放的偏置电流线,再旁边是一根动态信号线,再旁边又是一条偏置电流线,这样的效果比时钟线和动态信号线并排走要好。走电流信号比走电压信号更好。 数字模块和模拟模块的电源隔离 数字和模拟地都连接到衬底上,没办法做到真正的隔离,唯一可采取的措施在于拉远两者地的距离。数字地的diff都可以打细一些,金属保持足够的宽度,以减少与analog之间的串扰。 电源圈顺序 为保险起见,不管是analog还是digital,电源圈都是地在外,电源在内。 混合信号芯片的电源圈顺序 混合信号集成电路中模拟部分和数字部分,都要围两圈电源和地,有时候数字和模拟之间再加一圈地,这样从数字core到模拟core之间隔了五条宽线。按照一般的画法,模拟部分是电源放在内圈,地放在外圈,数字部分也是,都是地放外圈,但是为了使电源和地之间的寄生电容更大,有时需要这五条宽线的电源地交错出现,因此,电源和地谁在外谁在内也可以适当调整。但一般来说,是应该地在外圈,电源在内圈。如果对数字部分不放心,可将其多围几圈围得像水桶一样,这样更稳妥。 Digital电源线用多宽 SE(自动布局布线软件)没有电源分析功能,如果使用SE作PR(数字后端:自动布局布线Automatic place and route),电源线的宽度要自己人为设计,是否能够用也只能根据经验主观判断,工具也没有办法验证电源的线宽是否够用。因此,数字PR的线宽基本的概念还是很重要的。根据一般情况,digital部分的电源地线宽约为digital部分总面积的1/100比较合适,digital部分中间根据需要拉一些Strip,Strip的宽度可以适当减小一些,比如10um或者8um。对于0.5um工艺,每隔800um设一条Strip比较合适。 CMOS工艺中的浮阱处理 为了避免沟道调制效应,有些MOS管的衬底和源接在一起,如果这时MOS的源不在电源或地,则衬底需要一个单独的阱,称为浮阱。浮阱需要单独围起来,这圈地不能再围其他不同电位的浮阱,稳妥的做法是浮阱边缘n阱以内打一圈p_sub接地,之外再打一圈n_sub_ring接电源,即形成三圈guard ring。不同电位的浮阱是不能放在同一个guard ring中的。 宽metal开槽的两个解释 在0.5um工艺中,金属线超过30um,长超过500um中间要开槽,有机械的和电气两方面的原因。 机械原因:金属太宽,生产出来后更容易发生形变,容易“翘”起来,损坏芯片,开槽后,金属局部变细,不易“翘”。 电气原因:宽金属中电流在走电流的时候都是趋向边缘流动,金属中央的电流小,开槽后有效增加了电流的流通途径,减少了金属被电子撞断(电迁移)的危险。这个原理解释了为什么金属和金属之间的via要打很多小的via,而不是一整片大的via,因为很多小的via在一起,它们的周长加起来比一个大的via大得多,有效导通了电流。 运放版图的布局有哪些讲究 运放的输入级都用差分形式,讲究是做好对称和防止外来干扰。具体做法是用二维的中心对称,在输入管的两侧加dummy,在最外围加上厚一点的guard ring。对称管的连线比较绕,连线的时候让线从管子的外围绕,尽量不要在中心绕。因为中心绕线总要占用一些面积,这样对管就要拉开一些,这样不好。匹配性要求高的管子 尽量靠得近一些。如果放大级也用差分形式的电路,则比照处理。电流偏置的管子单独画在一起,用guard ring包起来,用作比较器的运放只对输入级要求较高,其它部分可灵活处理。 数模混合版图中数字外围该打substrate cont吗? 常规做法应该是打上substrate cont,因为数字部分内部噪声最大,如果这些噪声泄露出来,会对模拟版图有比较大的负面影响。把电源地用sub_cont打开到阱和衬底上可以把噪声都包围在数字版图内部。但数字地和模拟地都打到了sub_cont,那么数字和模拟地都接到一块儿了?一般还是建议数字电源地打sub_cont,还有一个比较好的做法就是在模拟版图的周围除了自身的电源地之外还打上额外的一层衬底接触的地,越厚越好,这一圈地什么都不接,直接接到gnd的PAD上,这样能更好的避免模拟部分被干扰。 Layout空白处ESD保护管周围不宜填充MOS电容 在版图工作后期,会有一些空白留出,可以填充一些电容来增加电源的洁净程度。如果芯片core limited,则PAD与PAD之间会突出一些空间,这些空间靠近ESD保护管,如果空间不够大,不足以让MOS电容和ESD保护管之间有足够距离避免latch_up。因此,在ESD保护管周围填充电容只能是POLY电容,或其它形式的不带diff电容。 版图空白处的利用 ① 打上到地或到电源的接触孔 ② 画上电源到地之间的电容 ③ 添加电源到地的ESD保护管 芯片的sealring简介 Sealring很容易和划片槽弄混。划片槽叫Scribe line,是把芯片从晶圆切下来的线,而sealring是围在芯片周围的一圈,从衬底到最上层金属全部都打一圈的保护圈。Sealring作用: ① 防止芯片在切割的时候的机械损伤,尤其是芯片的四角,一般不能放重要器件。 ② Sealring接地,屏蔽芯片外的干扰。 Sealring从衬底,到pdiff,contact,metal1,via,metal2...直到TOP金属,这样芯片中每一层都有一个圈圈拦截,能很好地受到机械和电气保护。 Sealring问题 Sealring中不是所有层次都做,有两类情况: 一类是考虑连接,如P注入,cont,metal1,via,metal2,这些层使得sealring最终跟上层的地连接; 另一类与Scribelane层次一致而且相连接,考虑到尽量减少Scribelane的厚度(包括Scribelane和sealring外面半圈),譬如pad,comp这些在工艺中实际上会腐蚀掉厚的场氧化层或者最后的钝化层。 PAD层通常不是加在整个Sealring上面的,而是沿着sealring的边沿加的,同时在design rule里面可以看到划片道上的pad区域mask的操作是clear的,也就是说,在工艺中,划片道上面的钝化层是被吃掉的,在sealring上面加PAD层是为了在划片时减小崩片和裂片的风险。 Sealring上的PAD层确定只是靠边缘很窄的一圈。 版图中电源地线的布局 数模混合中电源走线分三类:模拟电路的供电,数字电路的供电,ESD保护管的供电。 整个模拟版图外圈围上电源和地,电源内圈,地外圈。根据线路的功能,将模拟版图分成一个一个子块,这些子块的外圈再围上电源和地。功能类似,或者不会引起干扰的子块放在一起。电源是连接到N阱上的,比衬底要浅,对噪声的吸引效果比较弱,因此干扰源周围加比较宽的地连接。在空出来的地方根据需要交错加上电源和地的cont,注意连线的走向和尖角的倒角处理。模拟版图放到芯片的一角,而不要放在中央数字部分包围。bandgap中的pnp尽量放在远离数字版图的地方。 浅谈ADC中电阻电容的画法 ADC(模拟信号转数字输出)中电阻起到取样作用,对具体值不敏感,因此匹配性比较重要,要保证电阻链上从电源到地的电势均衡分配。在电阻的摆放上面要注意,避免工艺梯度造成的影响。最理想的匹配方案是将电阻从上而下摆放好,采用回形连接的方法,最上面的电阻条串到最下面的电阻条上,然后再往上,串到第二个电阻条上再往下,串到倒数第二根电阻条上,直到所有电阻条连接完毕。这样的电阻链受工艺梯度的影响最小。这样的连接方式连接较多,比较占面积。如果线路对取样精度要求不高,也可采用简化一点的蛇形连接方式。具体为,将从上至下的电阻条依次连接,再镜像复制这些电阻条,电源和地分别从这两列电阻条的最下方的电阻条连接,其它电平中间抽取。 ADC中的电容值呈金字塔分布,即从最大值电容,到最小值电容依次递减,在画这些电容时,同样要考虑到工艺梯度的影响。可将最小值电容画中间,值稍大的电容依次围在周围,在最外围加上dummy电容。连接电容最理想地避免了工艺梯度的影响,但在连接这些电容时,可适当用较细的连线从空隙处连接出来,不必多考虑连线电阻。 LDD工艺 在中芯国际0.18(或者别的工艺也有)中的层有:NLL(1.8V NLDD implantation)、PLL(1.8V PLDD implantation)、NLH(3.3V NLDD implantation)、PLH(3.3V PLDD implantation)、DG(Dual GATE)等层表示什么意思,该如何使用? LDD:Ligthly doped Drain浅掺杂源漏 目的:在短沟道条件下,减小漏端电场强度避免DIBL效应(Drain Induced Barrier Lowering) 这是短沟道器件制作过程中目前都会用到的工艺。 至于3.3V/1.8V则是对应不同VT管子,在制作LDD结构中掺杂浓度不同的,所以需要不同的MASK来区分。 短沟道效应 (short channel effcts) ① 短沟道效应主要是指阈值电压与沟道相关到非常严重的程度。 ② 沟道长度减小到一定程度后出现的一系列二级物理效应统称为短沟道效应。如漏致势垒降低(DIBL),随着漏源电压的增大,漏衬反偏PN结空间电荷区展宽,则沟道的有效长度减小,此在短沟道中尤为明显,严重会导致源漏穿通器失效。 DIBL效应 当漏极加上高电压时,由于栅很短,源极同时受到漏极影响,在此电场影响下,源结势垒降低。且漏极耗尽层打底,甚至跟源结的耗尽区相连,至使器件无法判断。 为降低二级物理效应的影响,实现短沟道器件,要在器件结构上加以改进。一方面设法降低沟道电场,尤其是漏端电场;另一方面要消除PN结之间,器件之间的相互作用。因此出现了轻掺杂漏MOS结构(LDD)和绝缘衬底上硅结构(SOI)。 RF PAD为什么都用DIOE? Diode用来做ESD效率相对低一些,为了达到较强的效果,通常面积会很大。但通常是DIODE配合MOS使用,面积过大相应寄生就大,需要平移,二极管的寄生不是很大吗?为什么在RF里面都用这个?二极管可以缺载高密度电流,面积相对MOS要小,短时间起作用,对CDM(带电器件的静电放电模型)特别有效。 为什么两个不同电位的阱放在一起更容易发生latch up? 两个NWELL和P型衬底形成一个NPN三极管,由于两个NWELL的电位不同,也就有了VCE电压,如果衬底有载流子经过使得三极管的VBE达到导通电压,那么三极管就会导通,从而发生latch up。 为了防止这个寄生的三极管导通,应该怎么做呢?在两个阱电位之间加P型环,这个P型环有两个作用:一个是降低衬底的电阻,使三极管不容易导通,第二个是吸收多数载流子也就是空穴。 为什么metal2的厚度会变薄? 一些老工艺因为平坦化做的不好,形成poly或metal的台阶,所以上层金属在跨过这些部分的时候,厚度可能受到影响,从而影响过流能力,所以这部分金属有过流要求的时候尽量不要用Min width可以适当加宽一点。 以上分享仅为作者《版图笔记》的一部分,需要查看更多内容,请在文末点击 阅读原文。或拷贝链接浏览器打开查看:网页链接 作者博客截图:

|

【本文地址】

amps(安培)

amps(安培) (安培)

(安培)