| 【FPGA & Verilog】模60计数器(原理图输⼊设计) | 您所在的位置:网站首页 › 模为60的8421bcd码计数器 › 【FPGA & Verilog】模60计数器(原理图输⼊设计) |

【FPGA & Verilog】模60计数器(原理图输⼊设计)

|

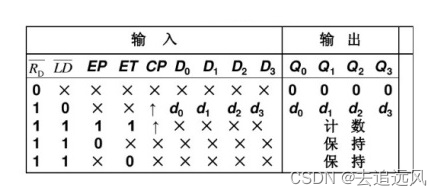

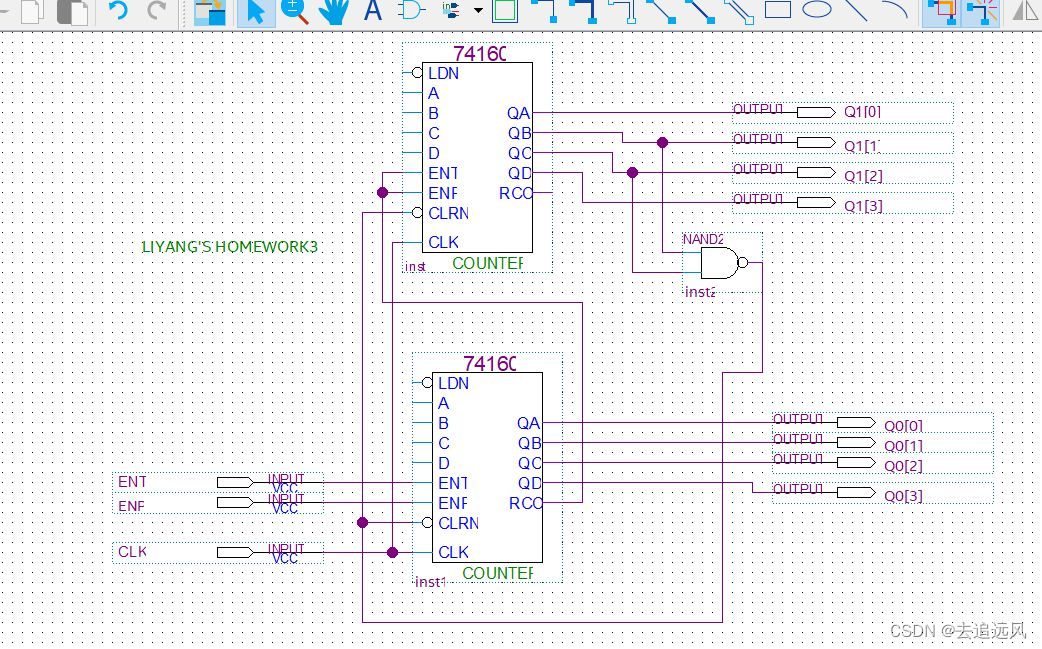

⼀ 实验⽬的 1. 掌握时序逻辑电路的设计⽅法 2. 掌握Quartus II软件原理图输⼊设计的流程 ⼆ 实验内容 2.1 设计输⼊ 1. 将时钟CLK作为电路输⼊端,Q[7:0]端作为输出。 2. 其余引脚按照计数器电路功能要求连接。 2.2 电路仿真1. 激励⽂件的输⼊包含时钟 CLK 2. 激励⽂件的输出为 Q 3. 功能仿真 三 实验报告 1. 设计思路及电路原理、所选器件功能及真值表、状态转移图等 2. 仿真结果Q[7:0]采⽤⼗进制⽆符号数⽅式显示。若输出采⽤BCD码,可以将Q[7:0]分为两个4bit⼗进制⽆符号数分组显示 3. 报告中附上电路原理图和仿真结果两个截图 设计思路: 1.选择的芯片是74LS160 同步10进制计数器 X 2 (高位,低位) 2.其中高位是采用异步清零的模6计数器,低位是正常的模10计数器,组成模60计数器 3.低位计数时,产生进位信号Co,接至高位模6的EP,ET端,促使高位+1 4.两者时钟信号为同一CLK 5.高位的输出Qd,Qc,Qb,Qa的四位二进制,仿真时选择无符号的十进制表示,即高位(0~5) 低位的输出Qd,Qc,Qb,Qa的四位二进制,仿真时选择无符号的十进制表示,即低位(0~9) 步骤: 1. 74ls160逻辑功能表

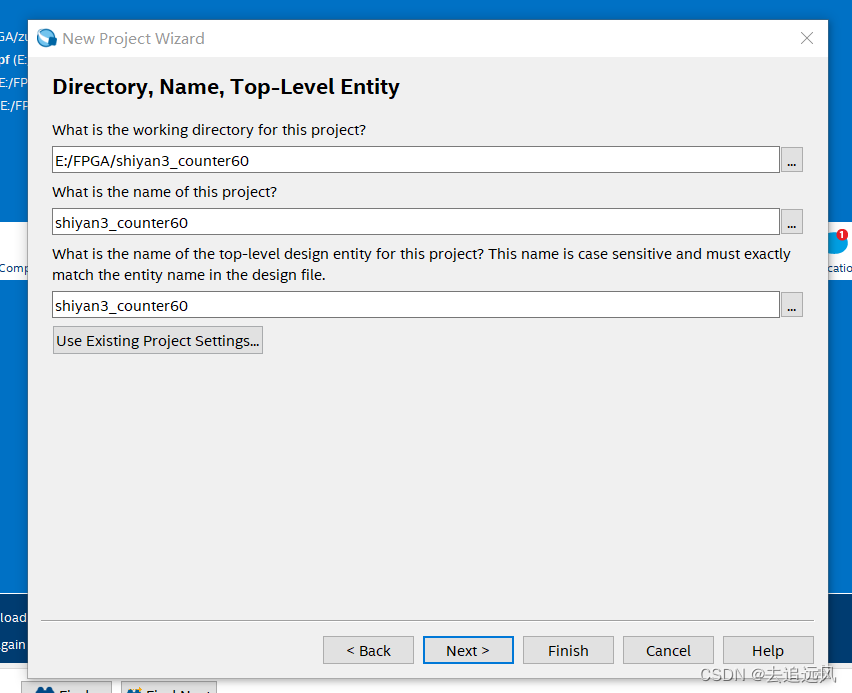

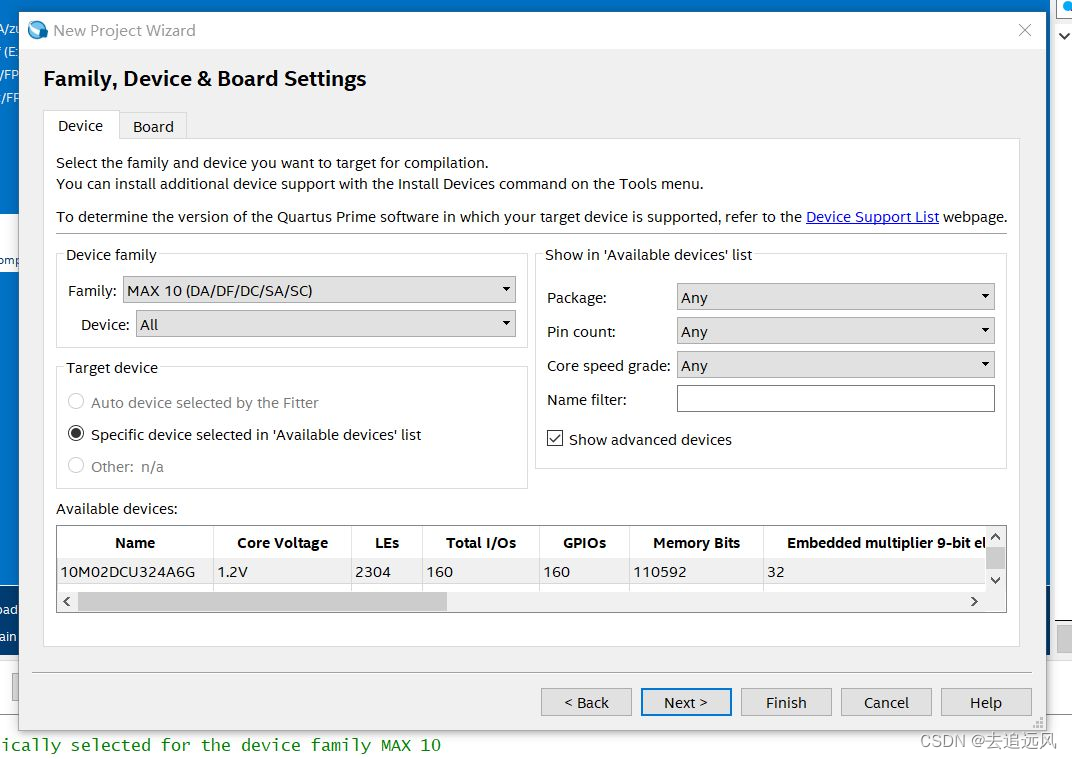

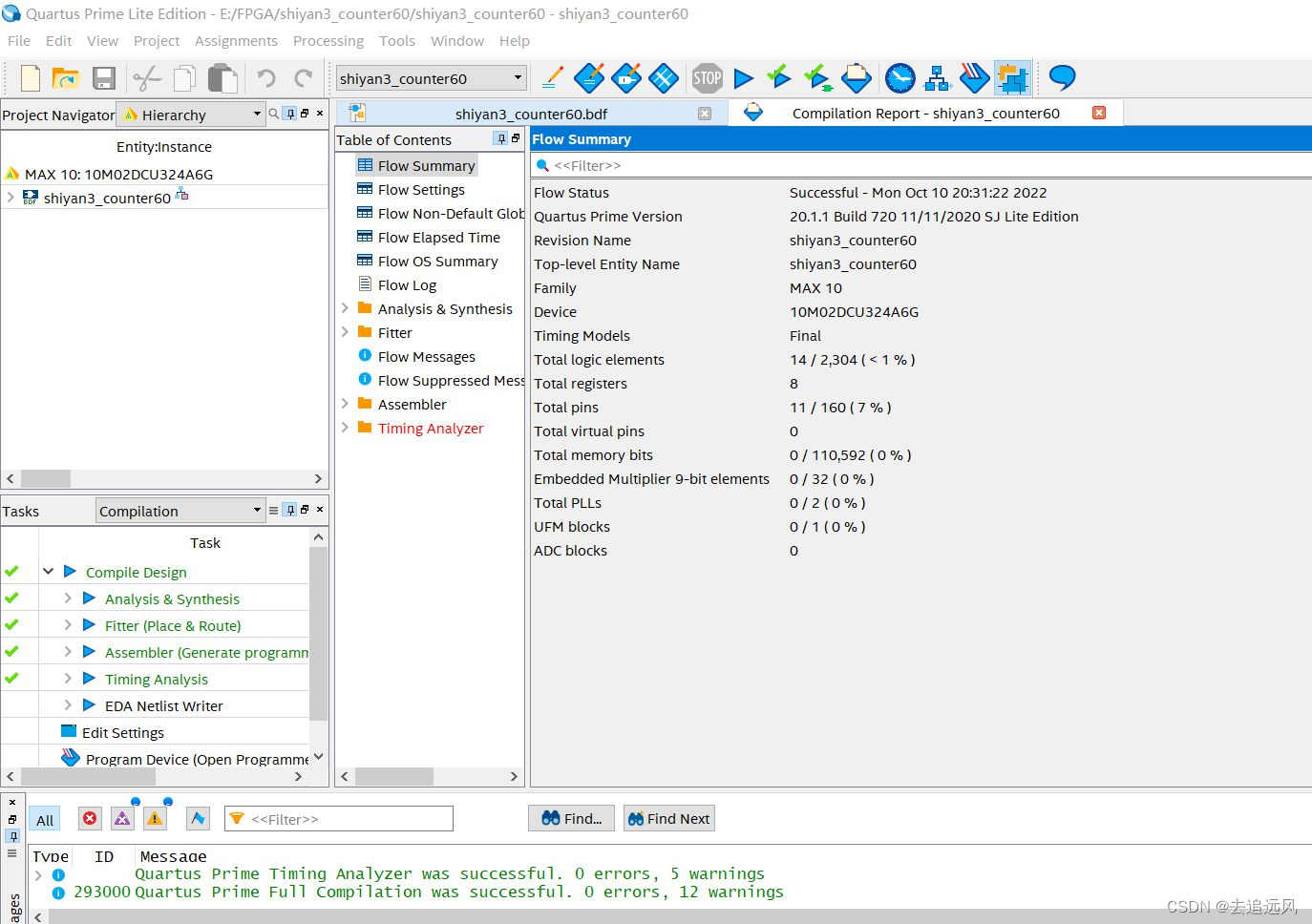

2.路径设置&器件选择

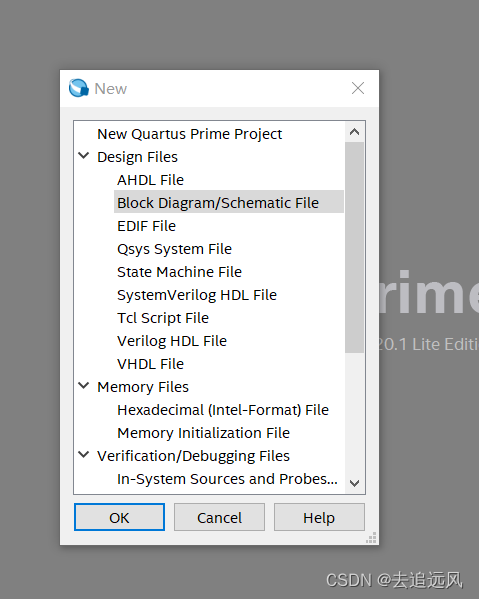

3.创建BDF文件&设计原理图

模6计数器设计: 采用了异步清零,将QB和QC接入二输入与非门,输出接至CLRN,当QB和QC都为1时,可使 CLRN 拉低,即,高位计数到6时,立即产生清零信号,使整个计数器归 0,不需要等待时钟CLK的到来 模10和模6级联设计: 低位模10的EP,ET要保持为11,计数状态,而高位模6的EP,ET要由低位模10的进位RCC作为输入 模60的输入: 时钟CLK,ENT,ETP 模60计数器的输出: 高位:模6的Qd,Qc,Qb,Qa 低位:模10的Qd,Qc,Qb,Qa 4.编译结果

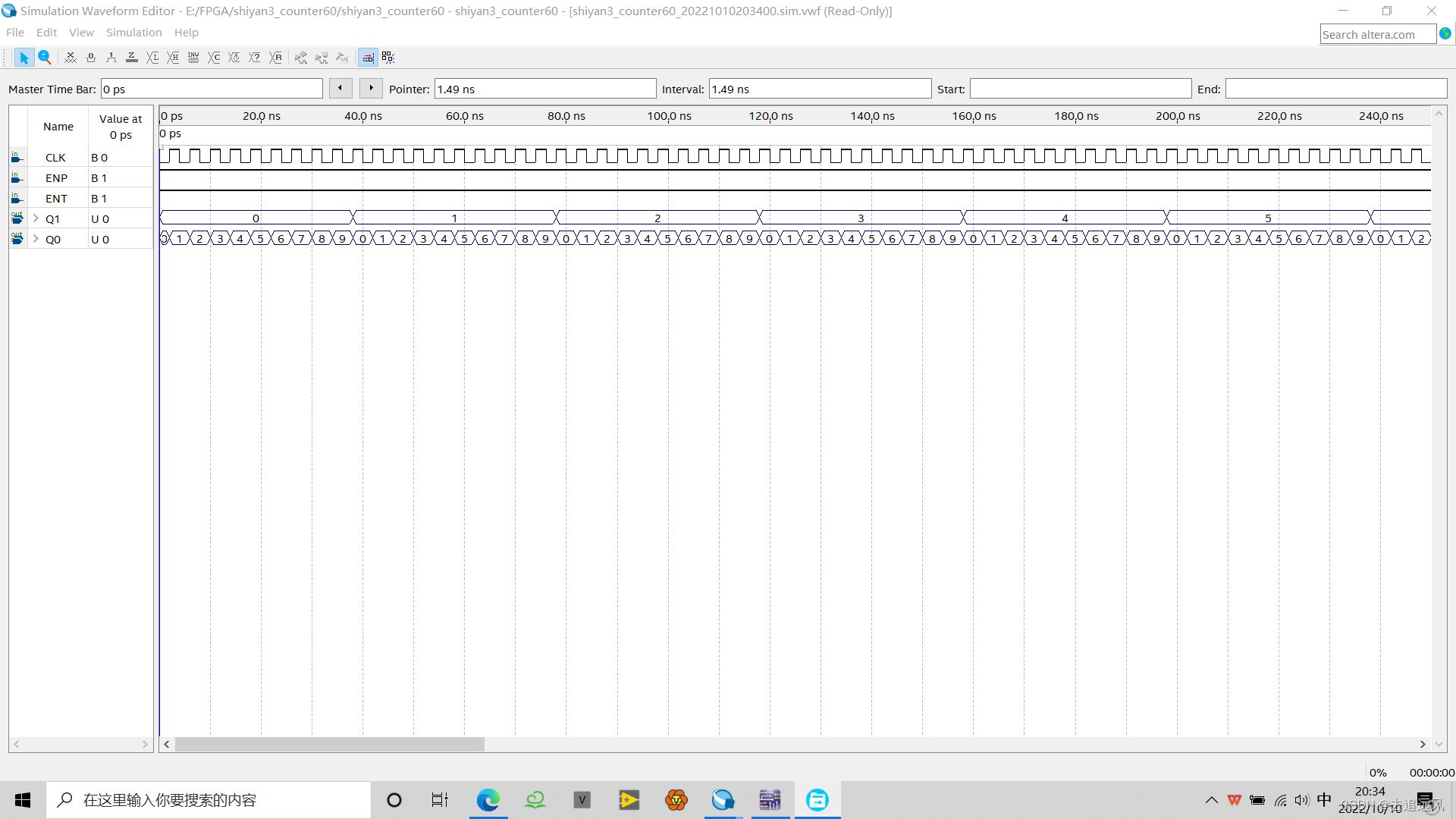

5.创建VWF文件进行仿真

波形分析:输出采⽤了BCD码,Q[7:0]分为两个4bit⼗进制⽆符号数分组显示 其中Q1为高位,数值范围0~5 其中Q0为低位,数值范围0~9 综合来看,计数范围为0~59 关注私信获取项目文件 |

【本文地址】