|

FPGA的Zynq 7000学习–基于黑金AX7010开发板的Hello World 实验

/9月开学入手了黑金AX7010开发板,自己也没有学到很多,但是还是想一步一步记录自己的进步,所以开了博客,也想好好归纳归纳,让自己尽快成长起来,谢谢。/ 大家学习C语言或者51单片机,相信也是从最基本的“Hello World实验”开始的。不过ZYNQ 7000又有一点不同,就是它是分为PL和PS两个部分,按道理我们应该先学习PL是什么?干什么用?怎么用?PS又是是什么?干什么用?怎么用? 但是我想,让大家先看到一个实验结果,相比会更加直观性,关于FPGA的相关知识点以及用到的原理有时间我会整理好,发出来。 现在,我们将在AX7010/AX7020开发板上创建一个简单的ZYNQ嵌入式系统(软核),然后我们将会使用SDK创建一个简单的软件应用程序,并下载到ZYNQ的ARM处理器中,实现串口的字符打印。 开始吧! 硬件平台:黑金AX7010开发板 vivado版本:Vivado 2017.4 SDK平台:SDK 2017.4 注:本实验只用到PS(ARM)部分,Vivado部分只是用来配置PS部分的引脚

1、 Vivado工程创建

1.1:打开Vivado的界面,在Vivado开发环境中双击Create New Project图标,创建一个新的工程。 1.2:弹出一个Vivado工程向导,点击Next按钮。 1.2:弹出一个Vivado工程向导,点击Next按钮。  1.3:在弹出的对话框中输入工程名和工程存放目录,我们这里取一个helloworld的工程名。点击Next按钮(注意:在create project subdirectory前面打勾,说明工程文件会在工程路径下新建一个工程名project name的文件夹下,不打勾就是工程会直接在project location的文件夹下)。 1.3:在弹出的对话框中输入工程名和工程存放目录,我们这里取一个helloworld的工程名。点击Next按钮(注意:在create project subdirectory前面打勾,说明工程文件会在工程路径下新建一个工程名project name的文件夹下,不打勾就是工程会直接在project location的文件夹下)。 1.4:在下面的对话框中默认选择RTL Project, 即生成RTL寄存器转换级的工程(具体的知识点以后会更新,现在看到别方),点击NEXT。 1.4:在下面的对话框中默认选择RTL Project, 即生成RTL寄存器转换级的工程(具体的知识点以后会更新,现在看到别方),点击NEXT。  1.5:添加源文件,即RTL的.v文件,因为我们这次只是演示,没必要自己写.v文件,所以暂时不选,点击NEXT。 1.5:添加源文件,即RTL的.v文件,因为我们这次只是演示,没必要自己写.v文件,所以暂时不选,点击NEXT。 1.6:添加约束文件,即.sdc文件,也暂时不选,点击NEXT。 1.6:添加约束文件,即.sdc文件,也暂时不选,点击NEXT。 1.7:在接下来的对话框选择所用的FPGA器件,以及进行一些配置。FPGA芯片型号一定要跟开发板上的型号一致,我这里是黑金的AX7010。首先在Family里选择Zynq-7000, Speed grade选择-1, Temp grade选择C,在Package选择clg400,然后在下面的列表中选择xc7z010clg400-1。(AX7020用户选择xc7z020clg400-2)。 1.7:在接下来的对话框选择所用的FPGA器件,以及进行一些配置。FPGA芯片型号一定要跟开发板上的型号一致,我这里是黑金的AX7010。首先在Family里选择Zynq-7000, Speed grade选择-1, Temp grade选择C,在Package选择clg400,然后在下面的列表中选择xc7z010clg400-1。(AX7020用户选择xc7z020clg400-2)。  1.8:再次确认一下板子型号有没有选对,没有问题再点击“Finish”完成工程创建。 1.8:再次确认一下板子型号有没有选对,没有问题再点击“Finish”完成工程创建。 1.9:工程创建后,图形化界面如下图所示,这就是Vivado的主界面了,一般的IP设计和.v文件的设计就是在这界面进行的: 1.9:工程创建后,图形化界面如下图所示,这就是Vivado的主界面了,一般的IP设计和.v文件的设计就是在这界面进行的:

2、建立原理图

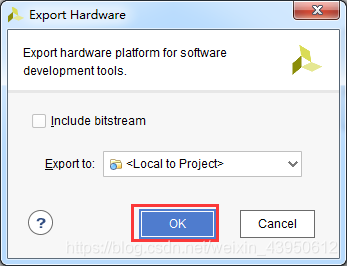

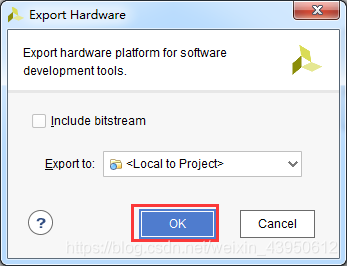

2.1 ZYNQ的嵌入式系统开发一般有原理框图的形式来设计,这样硬件的连接看起来会更加直观。点击“Create Block Design”按钮来添加原理图设计文件。  2.2:“Design name ”这里不做修改,保持默认 “design_1 ”,这里可以根据需要修改,不过名字要尽量简短,否则在 Windows 下编译会有问题。 2.2:“Design name ”这里不做修改,保持默认 “design_1 ”,这里可以根据需要修改,不过名字要尽量简短,否则在 Windows 下编译会有问题。  2.2:点击“ Add IP ”即“+”快捷图标。 2.2:点击“ Add IP ”即“+”快捷图标。  2.3:搜索“ zynq ”或者其他“system”等关键字,在搜索结果列表中双击 “ZYNQ7 Processing System”。(不要选择后面带BFM(总线功能模型)的,带BFM的IP 为先前的IP处理器版本)。 2.3:搜索“ zynq ”或者其他“system”等关键字,在搜索结果列表中双击 “ZYNQ7 Processing System”。(不要选择后面带BFM(总线功能模型)的,带BFM的IP 为先前的IP处理器版本)。  2.4:双击 Block 图中的“ processing_system7_0 ”模块,配置相关参数。 2.4:双击 Block 图中的“ processing_system7_0 ”模块,配置相关参数。  2.5:在“ PS PL Configuration ”选项中展开所有项目 。 其中Page Navigator界面下有8个子项,分别为Zynq Block Design, PS-PL Configuration,Peripheral I/O Pins, MIO Configration, Clock Configuration, DDR Configuration, SMCTiming Calculation, Interrupts。这些页面选项是针对ZYNQ的不同硬件模块的配置,其中PS_PL页面提供了PS到PL的相关接口配置信息以及PS部分一些配置信息;Peripheral I/O Pins页面主要是对一些通用外设接口的配置;MIO Configruation页面主要是对MIO已经EMIO的分配控制;Clock Configruation页面主要是对PS端时钟资源的配置和管理;DDR Configration页面主要是对DDR控制器一些参数的配置;Interrupts页面主要是对中断进行配置管理。 2.5:在“ PS PL Configuration ”选项中展开所有项目 。 其中Page Navigator界面下有8个子项,分别为Zynq Block Design, PS-PL Configuration,Peripheral I/O Pins, MIO Configration, Clock Configuration, DDR Configuration, SMCTiming Calculation, Interrupts。这些页面选项是针对ZYNQ的不同硬件模块的配置,其中PS_PL页面提供了PS到PL的相关接口配置信息以及PS部分一些配置信息;Peripheral I/O Pins页面主要是对一些通用外设接口的配置;MIO Configruation页面主要是对MIO已经EMIO的分配控制;Clock Configruation页面主要是对PS端时钟资源的配置和管理;DDR Configration页面主要是对DDR控制器一些参数的配置;Interrupts页面主要是对中断进行配置管理。  2.6:取消“ M AXI GP0 interface ”接口,这个接口可以扩展 PL 端的 AXI 接口外设,所以 PL 如果要和 PS 进行数据交互,都要按照 AXI 总线协议进行, xilinx 为我们提供了大量的 AXI 接口的 IP 核。 2.6:取消“ M AXI GP0 interface ”接口,这个接口可以扩展 PL 端的 AXI 接口外设,所以 PL 如果要和 PS 进行数据交互,都要按照 AXI 总线协议进行, xilinx 为我们提供了大量的 AXI 接口的 IP 核。  2.7:UART配置 从原理图中我们可以找到串口连接在 PS 的 MIO 48 MIO 49 上,所以在“ Peripheral I/OPins ”选项中使能 UART1 MIO 48 MIO49 Bank 0 电压选择“ LVCMOS3.3V Bank 1 电压选择“ LVCOMS 1.8 V ”,本实验仅仅使用了一个串口功能,这里就不再使用其他设备。 2.7:UART配置 从原理图中我们可以找到串口连接在 PS 的 MIO 48 MIO 49 上,所以在“ Peripheral I/OPins ”选项中使能 UART1 MIO 48 MIO49 Bank 0 电压选择“ LVCMOS3.3V Bank 1 电压选择“ LVCOMS 1.8 V ”,本实验仅仅使用了一个串口功能,这里就不再使用其他设备。  2.8:时钟配置 在“ Clock Configuration ”选项卡中我们可以配置 PS 时钟输入 频率,这里默认是33.333333 ,和板子上一致,不用修改 CPU 频率默认 666.666666Mhz ,这里也不修改。同时 PS 还可以给 PL 端提供 4 路时钟,频率可以配置,这里不需要,所以保持默认即可。 2.8:时钟配置 在“ Clock Configuration ”选项卡中我们可以配置 PS 时钟输入 频率,这里默认是33.333333 ,和板子上一致,不用修改 CPU 频率默认 666.666666Mhz ,这里也不修改。同时 PS 还可以给 PL 端提供 4 路时钟,频率可以配置,这里不需要,所以保持默认即可。  2.9:DDR3配置 在“ DDR Configuration ”选项卡中可以配置 PS 端 ddr 的参数, AX7010 配 置 DDR3 型号为“MT41J128M16 HA 125” AX7020 配置 DDR3 型号为“ MT41J256M16 RE 125” 这里ddr3 型号并不是板子上的 ddr3 型号,而是参数最接近的型号 。 “Effective DRAM BusWidth ”,选择 32 Bit。 2.9:DDR3配置 在“ DDR Configuration ”选项卡中可以配置 PS 端 ddr 的参数, AX7010 配 置 DDR3 型号为“MT41J128M16 HA 125” AX7020 配置 DDR3 型号为“ MT41J256M16 RE 125” 这里ddr3 型号并不是板子上的 ddr3 型号,而是参数最接近的型号 。 “Effective DRAM BusWidth ”,选择 32 Bit。  2.9:点击“ Run Block Automation vivado 软件会自动完成一些导出端口的工作。 2.9:点击“ Run Block Automation vivado 软件会自动完成一些导出端口的工作。  2.10:点击“ OK”。 2.10:点击“ OK”。  2.11:点击“ OK ”以后我们可以看到 PS 端导出一些管脚,包括 DDR 还有 FIXED_IO ,按键 Ctrl +s ”保存设计。 2.11:点击“ OK ”以后我们可以看到 PS 端导出一些管脚,包括 DDR 还有 FIXED_IO ,按键 Ctrl +s ”保存设计。  2.12:选择 Block 设计,右键“ Create HDL Wrapper… 创建一个 Verilog 或 VHDL 文件。 2.12:选择 Block 设计,右键“ Create HDL Wrapper… 创建一个 Verilog 或 VHDL 文件。  2.13:保持默认选项,点击“ OK”。 2.13:保持默认选项,点击“ OK”。  2.14:展开设计可以看到 PS 被当成一个普通 IP 来使用。 2.14:展开设计可以看到 PS 被当成一个普通 IP 来使用。  2.15:选择 block 设计,右键“ Generate Output Products” 2.15:选择 block 设计,右键“ Generate Output Products”  2.16:点击“ Generate”。 2.16:点击“ Generate”。  2.17:在菜单栏“ File --> Export --> Export Hardware…”导出硬件信息,这里就包含了 PS 了的配置信息。 2.17:在菜单栏“ File --> Export --> Export Hardware…”导出硬件信息,这里就包含了 PS 了的配置信息。  2.18:在弹出的对话框中点击“ OK ”,因为实验仅仅是使用了 PS 的串口,不需要 PL 参与,这里就没有使能“ Include bitstream”(将来比较复杂的设计就要添加进来了)。 2.18:在弹出的对话框中点击“ OK ”,因为实验仅仅是使用了 PS 的串口,不需要 PL 参与,这里就没有使能“ Include bitstream”(将来比较复杂的设计就要添加进来了)。

3、SDK调试部分

3.1:点击 Vivado 菜单“ File --> Launch SDK ”,启动 SDK。  3.2:启动 SDK 后我们会看到一个文件夹,有一个名为 "system.hdf ”文件,这个文件就包含了Vivado 硬件设计的信息,可以给软件开发使用,也可以看到 PS 端外设的寄存器列表。 3.2:启动 SDK 后我们会看到一个文件夹,有一个名为 "system.hdf ”文件,这个文件就包含了Vivado 硬件设计的信息,可以给软件开发使用,也可以看到 PS 端外设的寄存器列表。  3.3:在 SDK 的菜单“ New --> Application Project ”,建立一个 APP 工程。 3.3:在 SDK 的菜单“ New --> Application Project ”,建立一个 APP 工程。  3.4:“Project name ”填写 “hello ”,其他默认,点击 Next。 3.4:“Project name ”填写 “hello ”,其他默认,点击 Next。  3.5:模板选择“ Hello World ”,点击 Finish。 3.5:模板选择“ Hello World ”,点击 Finish。  3.6:可以看到 SDK 创建了一个“ hello ”目录,还有一个 hello_bsp ”的目录,在 hello_bsp目录中可以找到很多有用的信息,其中有“ BSP Documentation ”包含了一些 PS 外设的 API说明。 3.6:可以看到 SDK 创建了一个“ hello ”目录,还有一个 hello_bsp ”的目录,在 hello_bsp目录中可以找到很多有用的信息,其中有“ BSP Documentation ”包含了一些 PS 外设的 API说明。  3.7:双击“ system.mss ””,还可以看到有些 PS 外设还提供了例程,这是用来了解学习这些外设的第一手资料。 3.7:双击“ system.mss ””,还可以看到有些 PS 外设还提供了例程,这是用来了解学习这些外设的第一手资料。  3.8:连接 JTAG 线 到开发板 、 UART 的 USB 线 到 PC。 3.9:使用 PuTTY 软件做为串口终端调试工具, PuTTY 是一个免安装的小软件(其他的串口软件也可以的,只要波特率设置为默认的115200就行)。 3.8:连接 JTAG 线 到开发板 、 UART 的 USB 线 到 PC。 3.9:使用 PuTTY 软件做为串口终端调试工具, PuTTY 是一个免安装的小软件(其他的串口软件也可以的,只要波特率设置为默认的115200就行)。  3.10:选择 Serial Serial line 填写 COM3 Speed 填写 115200 COM3 串口号根据设备管理器里显示的填写 ,点击 Open。 3.10:选择 Serial Serial line 填写 COM3 Speed 填写 115200 COM3 串口号根据设备管理器里显示的填写 ,点击 Open。  3.11:在上电之前最好将开发板的启动模式设置到 JTAG 模式。 3.11:在上电之前最好将开发板的启动模式设置到 JTAG 模式。  3.12:给开发板上电,准备运行程序,开发板出厂时带有程序, 这里可以把运行模式选择 JTAG模式 然后重新上电 。选择“ hello ”,右键,可以看到很多选项,本实验要用到这里的Run as ”,就是把程序运行起来 Run as ”里又有很对选项,选择第一个 Launch onHardware(System Debuger) Debuger)”,使用系统调试,直接运行程序。 3.12:给开发板上电,准备运行程序,开发板出厂时带有程序, 这里可以把运行模式选择 JTAG模式 然后重新上电 。选择“ hello ”,右键,可以看到很多选项,本实验要用到这里的Run as ”,就是把程序运行起来 Run as ”里又有很对选项,选择第一个 Launch onHardware(System Debuger) Debuger)”,使用系统调试,直接运行程序。  3.13:这个时候观察 PuTTY 软件,可能有输出显示,也 可能 没有 输出。 3.13:这个时候观察 PuTTY 软件,可能有输出显示,也 可能 没有 输出。  3.14:为了保证系统的可靠调试,需要添加一个配置,右键“ Run As --> Run。 3.14:为了保证系统的可靠调试,需要添加一个配置,右键“ Run As --> Run。  3.15:选择“ Reset entire system ”复位整个系统,如果系统中还有 P L 设计,还必须选择Program FPGA ”,再次点击 Run。 3.15:选择“ Reset entire system ”复位整个系统,如果系统中还有 P L 设计,还必须选择Program FPGA ”,再次点击 Run。  3.16:点击“ OK ”,确认重新运行。 3.16:点击“ OK ”,确认重新运行。  3.17:这次就可以看到熟悉的“ Hello World ”显示出来了。 3.17:这次就可以看到熟悉的“ Hello World ”显示出来了。  3.18:除了“ Run As ”,还可以 Debug As ”,这样可以设置断点,单步运行。 3.18:除了“ Run As ”,还可以 Debug As ”,这样可以设置断点,单步运行。  3.19:进入 Debug 模式。 3.19:进入 Debug 模式。  3.20:和其他 C 语言调试模式一样,可以逐步运行、设置断点等。 3.20:和其他 C 语言调试模式一样,可以逐步运行、设置断点等。 3.22:右上角可以切换 IDE 模式。 3.22:右上角可以切换 IDE 模式。  至此,整个实验就完成了。本次实验通过一个简单的 Hello World 讲解了 SDK 的使用, SDK 拥有很强大的功能,不能一 一讲解,在我们不断的使用中逐渐掌握。 本次实验主要是依照黑金的教程来做,黑金基础教程只是第一步,这第一步一定得做好,每一步都走好,尽量掌握每一步为什么要这么做,硬件设计就是积累的过程,慢慢学吧,有疑问的欢迎一起交流,谢谢! 至此,整个实验就完成了。本次实验通过一个简单的 Hello World 讲解了 SDK 的使用, SDK 拥有很强大的功能,不能一 一讲解,在我们不断的使用中逐渐掌握。 本次实验主要是依照黑金的教程来做,黑金基础教程只是第一步,这第一步一定得做好,每一步都走好,尽量掌握每一步为什么要这么做,硬件设计就是积累的过程,慢慢学吧,有疑问的欢迎一起交流,谢谢!

|  1.2:弹出一个Vivado工程向导,点击Next按钮。

1.2:弹出一个Vivado工程向导,点击Next按钮。  1.3:在弹出的对话框中输入工程名和工程存放目录,我们这里取一个helloworld的工程名。点击Next按钮(注意:在create project subdirectory前面打勾,说明工程文件会在工程路径下新建一个工程名project name的文件夹下,不打勾就是工程会直接在project location的文件夹下)。

1.3:在弹出的对话框中输入工程名和工程存放目录,我们这里取一个helloworld的工程名。点击Next按钮(注意:在create project subdirectory前面打勾,说明工程文件会在工程路径下新建一个工程名project name的文件夹下,不打勾就是工程会直接在project location的文件夹下)。 1.4:在下面的对话框中默认选择RTL Project, 即生成RTL寄存器转换级的工程(具体的知识点以后会更新,现在看到别方),点击NEXT。

1.4:在下面的对话框中默认选择RTL Project, 即生成RTL寄存器转换级的工程(具体的知识点以后会更新,现在看到别方),点击NEXT。  1.5:添加源文件,即RTL的.v文件,因为我们这次只是演示,没必要自己写.v文件,所以暂时不选,点击NEXT。

1.5:添加源文件,即RTL的.v文件,因为我们这次只是演示,没必要自己写.v文件,所以暂时不选,点击NEXT。 1.6:添加约束文件,即.sdc文件,也暂时不选,点击NEXT。

1.6:添加约束文件,即.sdc文件,也暂时不选,点击NEXT。 1.7:在接下来的对话框选择所用的FPGA器件,以及进行一些配置。FPGA芯片型号一定要跟开发板上的型号一致,我这里是黑金的AX7010。首先在Family里选择Zynq-7000, Speed grade选择-1, Temp grade选择C,在Package选择clg400,然后在下面的列表中选择xc7z010clg400-1。(AX7020用户选择xc7z020clg400-2)。

1.7:在接下来的对话框选择所用的FPGA器件,以及进行一些配置。FPGA芯片型号一定要跟开发板上的型号一致,我这里是黑金的AX7010。首先在Family里选择Zynq-7000, Speed grade选择-1, Temp grade选择C,在Package选择clg400,然后在下面的列表中选择xc7z010clg400-1。(AX7020用户选择xc7z020clg400-2)。  1.8:再次确认一下板子型号有没有选对,没有问题再点击“Finish”完成工程创建。

1.8:再次确认一下板子型号有没有选对,没有问题再点击“Finish”完成工程创建。 1.9:工程创建后,图形化界面如下图所示,这就是Vivado的主界面了,一般的IP设计和.v文件的设计就是在这界面进行的:

1.9:工程创建后,图形化界面如下图所示,这就是Vivado的主界面了,一般的IP设计和.v文件的设计就是在这界面进行的:

2.2:“Design name ”这里不做修改,保持默认 “design_1 ”,这里可以根据需要修改,不过名字要尽量简短,否则在 Windows 下编译会有问题。

2.2:“Design name ”这里不做修改,保持默认 “design_1 ”,这里可以根据需要修改,不过名字要尽量简短,否则在 Windows 下编译会有问题。  2.2:点击“ Add IP ”即“+”快捷图标。

2.2:点击“ Add IP ”即“+”快捷图标。  2.3:搜索“ zynq ”或者其他“system”等关键字,在搜索结果列表中双击 “ZYNQ7 Processing System”。(不要选择后面带BFM(总线功能模型)的,带BFM的IP 为先前的IP处理器版本)。

2.3:搜索“ zynq ”或者其他“system”等关键字,在搜索结果列表中双击 “ZYNQ7 Processing System”。(不要选择后面带BFM(总线功能模型)的,带BFM的IP 为先前的IP处理器版本)。  2.4:双击 Block 图中的“ processing_system7_0 ”模块,配置相关参数。

2.4:双击 Block 图中的“ processing_system7_0 ”模块,配置相关参数。  2.5:在“ PS PL Configuration ”选项中展开所有项目 。 其中Page Navigator界面下有8个子项,分别为Zynq Block Design, PS-PL Configuration,Peripheral I/O Pins, MIO Configration, Clock Configuration, DDR Configuration, SMCTiming Calculation, Interrupts。这些页面选项是针对ZYNQ的不同硬件模块的配置,其中PS_PL页面提供了PS到PL的相关接口配置信息以及PS部分一些配置信息;Peripheral I/O Pins页面主要是对一些通用外设接口的配置;MIO Configruation页面主要是对MIO已经EMIO的分配控制;Clock Configruation页面主要是对PS端时钟资源的配置和管理;DDR Configration页面主要是对DDR控制器一些参数的配置;Interrupts页面主要是对中断进行配置管理。

2.5:在“ PS PL Configuration ”选项中展开所有项目 。 其中Page Navigator界面下有8个子项,分别为Zynq Block Design, PS-PL Configuration,Peripheral I/O Pins, MIO Configration, Clock Configuration, DDR Configuration, SMCTiming Calculation, Interrupts。这些页面选项是针对ZYNQ的不同硬件模块的配置,其中PS_PL页面提供了PS到PL的相关接口配置信息以及PS部分一些配置信息;Peripheral I/O Pins页面主要是对一些通用外设接口的配置;MIO Configruation页面主要是对MIO已经EMIO的分配控制;Clock Configruation页面主要是对PS端时钟资源的配置和管理;DDR Configration页面主要是对DDR控制器一些参数的配置;Interrupts页面主要是对中断进行配置管理。  2.6:取消“ M AXI GP0 interface ”接口,这个接口可以扩展 PL 端的 AXI 接口外设,所以 PL 如果要和 PS 进行数据交互,都要按照 AXI 总线协议进行, xilinx 为我们提供了大量的 AXI 接口的 IP 核。

2.6:取消“ M AXI GP0 interface ”接口,这个接口可以扩展 PL 端的 AXI 接口外设,所以 PL 如果要和 PS 进行数据交互,都要按照 AXI 总线协议进行, xilinx 为我们提供了大量的 AXI 接口的 IP 核。  2.7:UART配置 从原理图中我们可以找到串口连接在 PS 的 MIO 48 MIO 49 上,所以在“ Peripheral I/OPins ”选项中使能 UART1 MIO 48 MIO49 Bank 0 电压选择“ LVCMOS3.3V Bank 1 电压选择“ LVCOMS 1.8 V ”,本实验仅仅使用了一个串口功能,这里就不再使用其他设备。

2.7:UART配置 从原理图中我们可以找到串口连接在 PS 的 MIO 48 MIO 49 上,所以在“ Peripheral I/OPins ”选项中使能 UART1 MIO 48 MIO49 Bank 0 电压选择“ LVCMOS3.3V Bank 1 电压选择“ LVCOMS 1.8 V ”,本实验仅仅使用了一个串口功能,这里就不再使用其他设备。  2.8:时钟配置 在“ Clock Configuration ”选项卡中我们可以配置 PS 时钟输入 频率,这里默认是33.333333 ,和板子上一致,不用修改 CPU 频率默认 666.666666Mhz ,这里也不修改。同时 PS 还可以给 PL 端提供 4 路时钟,频率可以配置,这里不需要,所以保持默认即可。

2.8:时钟配置 在“ Clock Configuration ”选项卡中我们可以配置 PS 时钟输入 频率,这里默认是33.333333 ,和板子上一致,不用修改 CPU 频率默认 666.666666Mhz ,这里也不修改。同时 PS 还可以给 PL 端提供 4 路时钟,频率可以配置,这里不需要,所以保持默认即可。  2.9:DDR3配置 在“ DDR Configuration ”选项卡中可以配置 PS 端 ddr 的参数, AX7010 配 置 DDR3 型号为“MT41J128M16 HA 125” AX7020 配置 DDR3 型号为“ MT41J256M16 RE 125” 这里ddr3 型号并不是板子上的 ddr3 型号,而是参数最接近的型号 。 “Effective DRAM BusWidth ”,选择 32 Bit。

2.9:DDR3配置 在“ DDR Configuration ”选项卡中可以配置 PS 端 ddr 的参数, AX7010 配 置 DDR3 型号为“MT41J128M16 HA 125” AX7020 配置 DDR3 型号为“ MT41J256M16 RE 125” 这里ddr3 型号并不是板子上的 ddr3 型号,而是参数最接近的型号 。 “Effective DRAM BusWidth ”,选择 32 Bit。  2.9:点击“ Run Block Automation vivado 软件会自动完成一些导出端口的工作。

2.9:点击“ Run Block Automation vivado 软件会自动完成一些导出端口的工作。  2.10:点击“ OK”。

2.10:点击“ OK”。  2.11:点击“ OK ”以后我们可以看到 PS 端导出一些管脚,包括 DDR 还有 FIXED_IO ,按键 Ctrl +s ”保存设计。

2.11:点击“ OK ”以后我们可以看到 PS 端导出一些管脚,包括 DDR 还有 FIXED_IO ,按键 Ctrl +s ”保存设计。  2.12:选择 Block 设计,右键“ Create HDL Wrapper… 创建一个 Verilog 或 VHDL 文件。

2.12:选择 Block 设计,右键“ Create HDL Wrapper… 创建一个 Verilog 或 VHDL 文件。  2.13:保持默认选项,点击“ OK”。

2.13:保持默认选项,点击“ OK”。  2.14:展开设计可以看到 PS 被当成一个普通 IP 来使用。

2.14:展开设计可以看到 PS 被当成一个普通 IP 来使用。  2.15:选择 block 设计,右键“ Generate Output Products”

2.15:选择 block 设计,右键“ Generate Output Products”  2.16:点击“ Generate”。

2.16:点击“ Generate”。  2.17:在菜单栏“ File --> Export --> Export Hardware…”导出硬件信息,这里就包含了 PS 了的配置信息。

2.17:在菜单栏“ File --> Export --> Export Hardware…”导出硬件信息,这里就包含了 PS 了的配置信息。  2.18:在弹出的对话框中点击“ OK ”,因为实验仅仅是使用了 PS 的串口,不需要 PL 参与,这里就没有使能“ Include bitstream”(将来比较复杂的设计就要添加进来了)。

2.18:在弹出的对话框中点击“ OK ”,因为实验仅仅是使用了 PS 的串口,不需要 PL 参与,这里就没有使能“ Include bitstream”(将来比较复杂的设计就要添加进来了)。

3.2:启动 SDK 后我们会看到一个文件夹,有一个名为 "system.hdf ”文件,这个文件就包含了Vivado 硬件设计的信息,可以给软件开发使用,也可以看到 PS 端外设的寄存器列表。

3.2:启动 SDK 后我们会看到一个文件夹,有一个名为 "system.hdf ”文件,这个文件就包含了Vivado 硬件设计的信息,可以给软件开发使用,也可以看到 PS 端外设的寄存器列表。  3.3:在 SDK 的菜单“ New --> Application Project ”,建立一个 APP 工程。

3.3:在 SDK 的菜单“ New --> Application Project ”,建立一个 APP 工程。  3.4:“Project name ”填写 “hello ”,其他默认,点击 Next。

3.4:“Project name ”填写 “hello ”,其他默认,点击 Next。  3.5:模板选择“ Hello World ”,点击 Finish。

3.5:模板选择“ Hello World ”,点击 Finish。  3.6:可以看到 SDK 创建了一个“ hello ”目录,还有一个 hello_bsp ”的目录,在 hello_bsp目录中可以找到很多有用的信息,其中有“ BSP Documentation ”包含了一些 PS 外设的 API说明。

3.6:可以看到 SDK 创建了一个“ hello ”目录,还有一个 hello_bsp ”的目录,在 hello_bsp目录中可以找到很多有用的信息,其中有“ BSP Documentation ”包含了一些 PS 外设的 API说明。  3.7:双击“ system.mss ””,还可以看到有些 PS 外设还提供了例程,这是用来了解学习这些外设的第一手资料。

3.7:双击“ system.mss ””,还可以看到有些 PS 外设还提供了例程,这是用来了解学习这些外设的第一手资料。  3.8:连接 JTAG 线 到开发板 、 UART 的 USB 线 到 PC。 3.9:使用 PuTTY 软件做为串口终端调试工具, PuTTY 是一个免安装的小软件(其他的串口软件也可以的,只要波特率设置为默认的115200就行)。

3.8:连接 JTAG 线 到开发板 、 UART 的 USB 线 到 PC。 3.9:使用 PuTTY 软件做为串口终端调试工具, PuTTY 是一个免安装的小软件(其他的串口软件也可以的,只要波特率设置为默认的115200就行)。  3.10:选择 Serial Serial line 填写 COM3 Speed 填写 115200 COM3 串口号根据设备管理器里显示的填写 ,点击 Open。

3.10:选择 Serial Serial line 填写 COM3 Speed 填写 115200 COM3 串口号根据设备管理器里显示的填写 ,点击 Open。  3.11:在上电之前最好将开发板的启动模式设置到 JTAG 模式。

3.11:在上电之前最好将开发板的启动模式设置到 JTAG 模式。  3.12:给开发板上电,准备运行程序,开发板出厂时带有程序, 这里可以把运行模式选择 JTAG模式 然后重新上电 。选择“ hello ”,右键,可以看到很多选项,本实验要用到这里的Run as ”,就是把程序运行起来 Run as ”里又有很对选项,选择第一个 Launch onHardware(System Debuger) Debuger)”,使用系统调试,直接运行程序。

3.12:给开发板上电,准备运行程序,开发板出厂时带有程序, 这里可以把运行模式选择 JTAG模式 然后重新上电 。选择“ hello ”,右键,可以看到很多选项,本实验要用到这里的Run as ”,就是把程序运行起来 Run as ”里又有很对选项,选择第一个 Launch onHardware(System Debuger) Debuger)”,使用系统调试,直接运行程序。  3.13:这个时候观察 PuTTY 软件,可能有输出显示,也 可能 没有 输出。

3.13:这个时候观察 PuTTY 软件,可能有输出显示,也 可能 没有 输出。  3.14:为了保证系统的可靠调试,需要添加一个配置,右键“ Run As --> Run。

3.14:为了保证系统的可靠调试,需要添加一个配置,右键“ Run As --> Run。  3.15:选择“ Reset entire system ”复位整个系统,如果系统中还有 P L 设计,还必须选择Program FPGA ”,再次点击 Run。

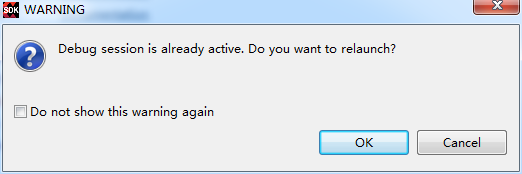

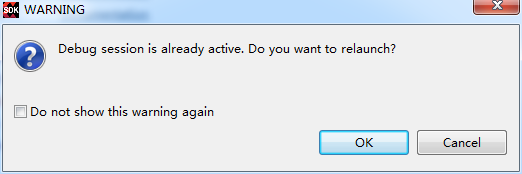

3.15:选择“ Reset entire system ”复位整个系统,如果系统中还有 P L 设计,还必须选择Program FPGA ”,再次点击 Run。  3.16:点击“ OK ”,确认重新运行。

3.16:点击“ OK ”,确认重新运行。  3.17:这次就可以看到熟悉的“ Hello World ”显示出来了。

3.17:这次就可以看到熟悉的“ Hello World ”显示出来了。  3.18:除了“ Run As ”,还可以 Debug As ”,这样可以设置断点,单步运行。

3.18:除了“ Run As ”,还可以 Debug As ”,这样可以设置断点,单步运行。  3.19:进入 Debug 模式。

3.19:进入 Debug 模式。  3.20:和其他 C 语言调试模式一样,可以逐步运行、设置断点等。

3.20:和其他 C 语言调试模式一样,可以逐步运行、设置断点等。 3.22:右上角可以切换 IDE 模式。

3.22:右上角可以切换 IDE 模式。  至此,整个实验就完成了。本次实验通过一个简单的 Hello World 讲解了 SDK 的使用, SDK 拥有很强大的功能,不能一 一讲解,在我们不断的使用中逐渐掌握。 本次实验主要是依照黑金的教程来做,黑金基础教程只是第一步,这第一步一定得做好,每一步都走好,尽量掌握每一步为什么要这么做,硬件设计就是积累的过程,慢慢学吧,有疑问的欢迎一起交流,谢谢!

至此,整个实验就完成了。本次实验通过一个简单的 Hello World 讲解了 SDK 的使用, SDK 拥有很强大的功能,不能一 一讲解,在我们不断的使用中逐渐掌握。 本次实验主要是依照黑金的教程来做,黑金基础教程只是第一步,这第一步一定得做好,每一步都走好,尽量掌握每一步为什么要这么做,硬件设计就是积累的过程,慢慢学吧,有疑问的欢迎一起交流,谢谢!