| 时钟树综合(1) | 您所在的位置:网站首页 › 时钟树综合工具 › 时钟树综合(1) |

时钟树综合(1)

|

时钟树综合 学习

背景

时钟信号是数据传输的基准,他对于同步数字系统的功能、性能、稳定性起决定性作用。时钟信号通常是整个芯片中有最大扇出、通过最长距离、以最高速度运行的信号。时钟信号必须要保证在最差的条件下,关键的时序要求能够满足,否则对时钟信号的任何不当的控制都可能导致紊乱情况,将错误的数据信号索存到寄存器,从而导致系统功能的错误。 时钟信号怎么产生的时钟信号源一般是从晶体(石英晶体、陶瓷晶体)产生的。IC设计时通常会使用晶体振荡器来提供时钟源信号。一般会使用PLL加上晶体振荡器来给芯片内部电路提供倍频或相位的时钟信号。 时钟信号特征

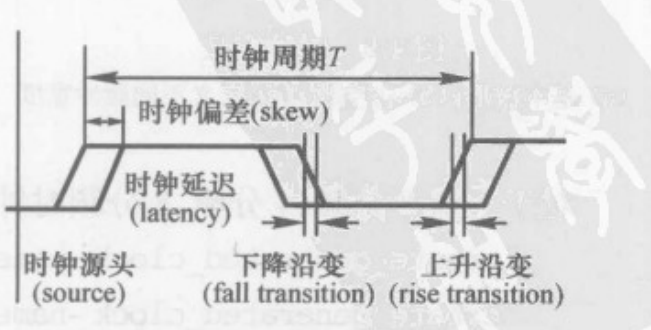

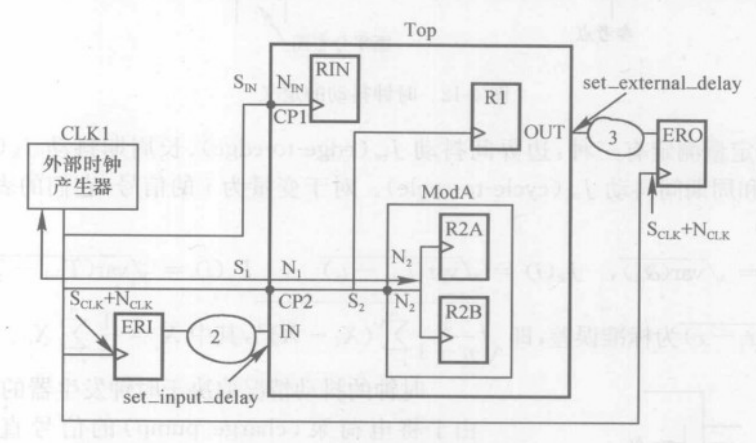

时钟的周期(频率)、时钟延迟、时钟信号的不确定性是时钟的三个主要特征要素。 时钟信号延迟时钟信号延迟(latency)又称为插入延迟(insertion delay), 包括时钟源插入延迟和时钟网络插入延迟。 时钟源插入延迟是来自系统到当前芯片(当前模块)时钟根节点(clock root pin)之间的延迟,时钟网络插入延迟是时钟树的延迟。

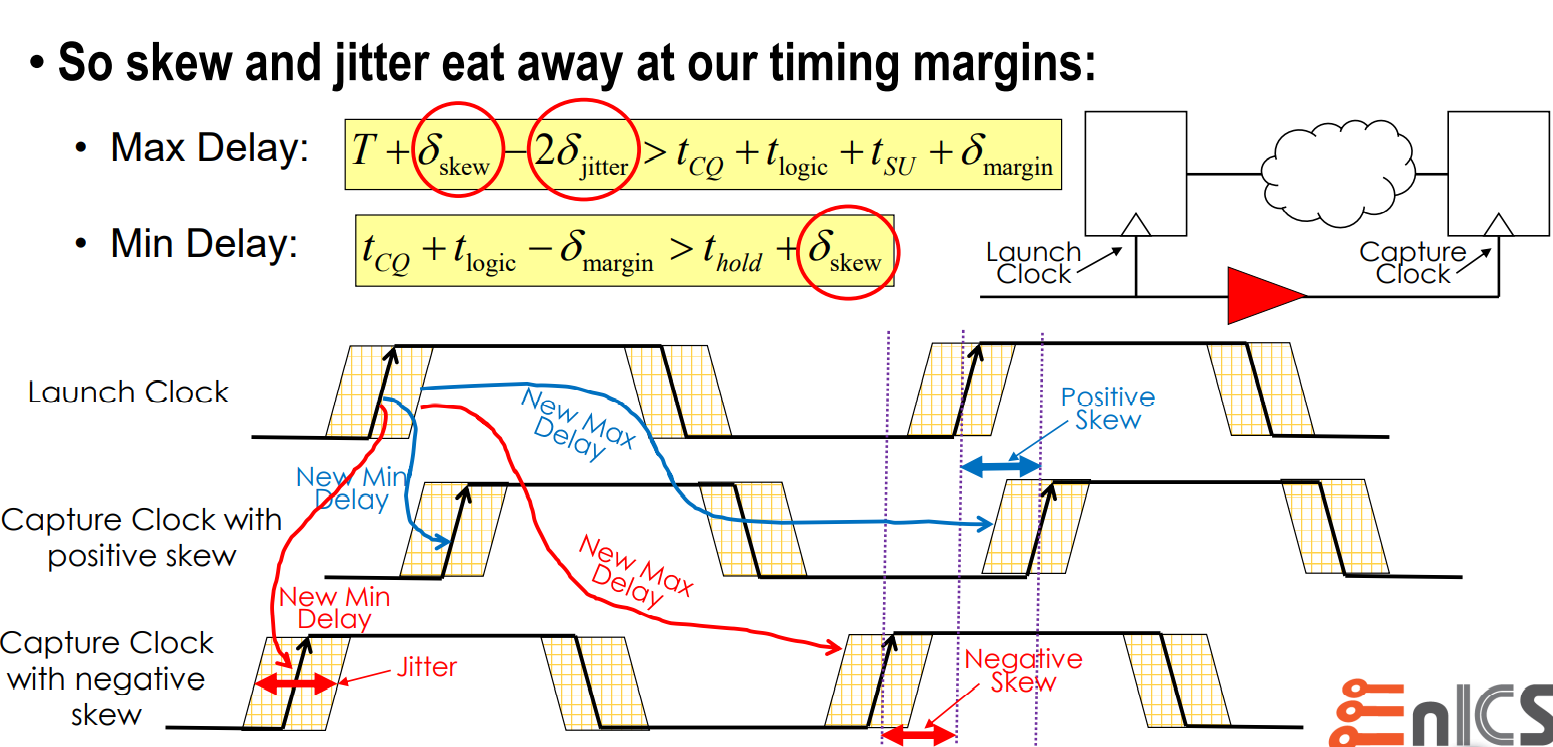

时钟信号不确定性 时钟信号的不确定性主要是有时钟信号抖动引起的,时钟抖动是先天存在的,所以在时钟树综合的时候只能考虑起影响,无法消除。时钟抖动是信号实际时间与理想时间的偏差,抖动中含有确定抖动成分和随机抖动的成分【抖动】。 时钟信号偏差 时钟信号偏差是指同一时钟达到该时钟域内的不同寄存器之间的时间偏差,也即是 $$skew = max(|t_i - t_j|)$$

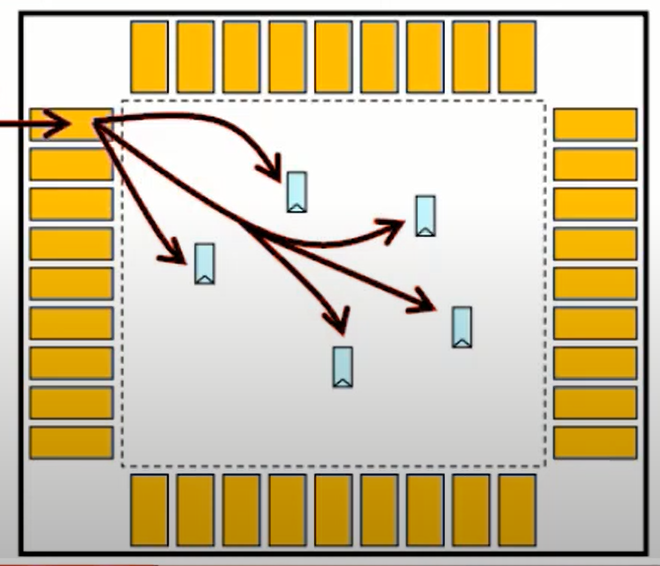

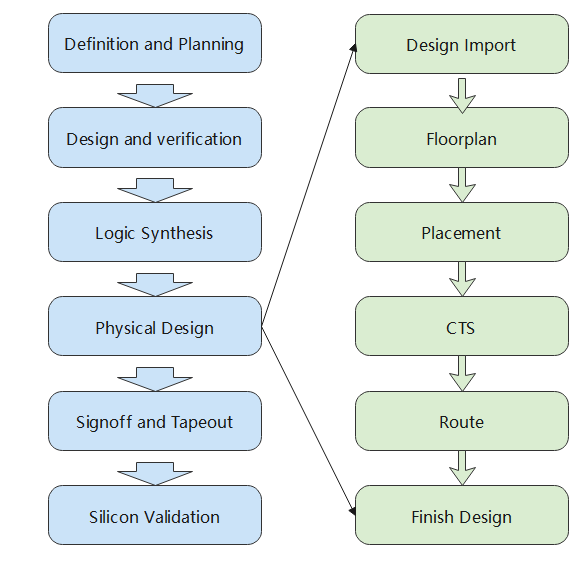

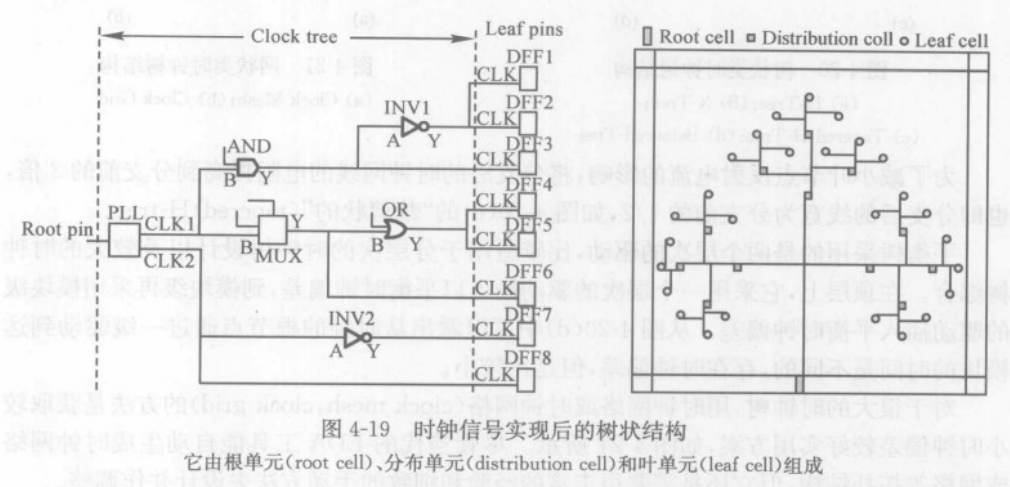

产生时钟偏差的原因有多种:时钟源到各个时钟端点的路径长度不同、各个端点负载不同、在时钟网中插入的缓冲器不同等。 在什么时候做时钟树综合: 如下图所示,通常在物理设计布局完成之后布线之前进行时钟树综合。在此之前所有的寄存器时钟信号是由同一个时钟pin驱动的,具有相同的延时的理想时钟。 已经生成了gatelevel 的netlist 已经有一个初步的版图规划,每个逻辑门包括时序器件都有一个具体的位置。 已经基于理想时钟完成了时序优化设计。

目标 解决什么问题 给定一个源节点和N个目标节点,时钟树综合就是生成一个连接方案,将源节点和这N个目标节点连接起来。通过插入反相器或者buffer平衡时钟各个路径分支上的延时,也就是skew足够的小,同时又要尽量减少延时;另外还要满足整体的SDC约束例如:maximum transition time. maximum load capacitance. maximum fanout 。工具同时还要考虑时钟树综合方案对于功耗、面积等的影响。 通常增加时钟路径延迟,在时钟树不同路径上插入buffer,可以保证各个路径的延时接近,也就可以降低skew, 但是引入buffer会增加功耗和面积。所以skew和延迟是一个矛盾的约束,需要设计者根据目标来决定。例如在skew要求没那么严格的场景下,可以极少延时来降低功耗和面积;在高速集成设计的场景,时钟频率高,对skew敏感,则要首先满足skew的要求。

As all sequential logic is designed to change state in temporal reference to the clock, minimizing the clock delay and clock skew between different points in the chip is crucial for reliable operation Clock timing skew is both systematic and random, but the former can be mitigated through good design. Different approaches to clock distribution have been developed based on chip requirements such as clock frequency, permissible skew, physical die area and the power budget。 对于timing的影响分析

现有技术介绍

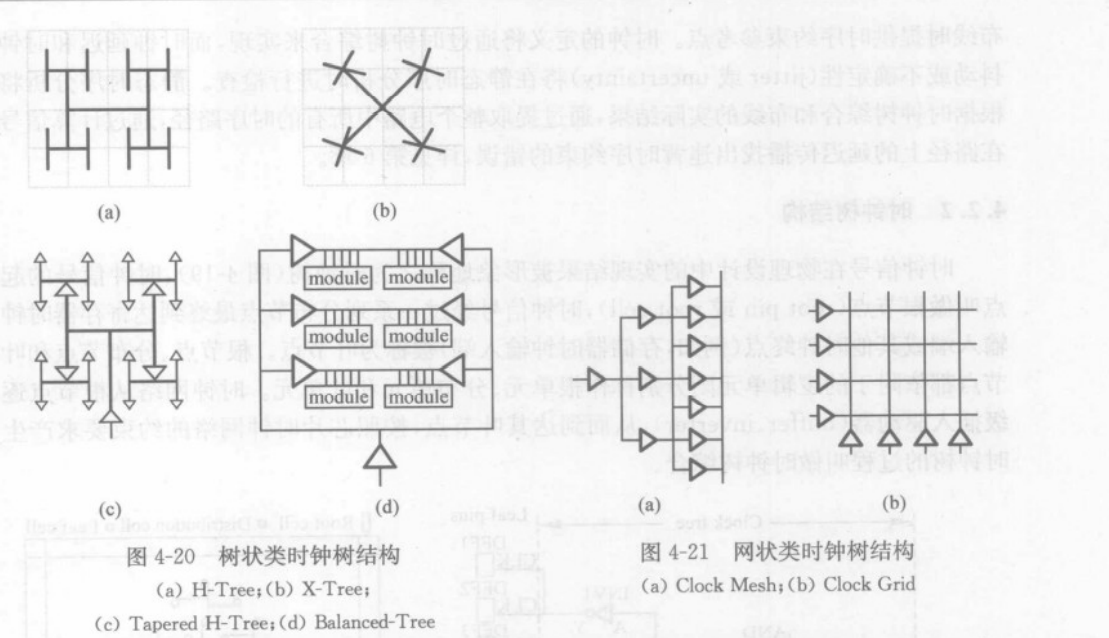

时钟树根据其在芯片内的分布特征,分为H树、X树、平衡树、以及梳状或脊柱状时钟网(clock tree mesh, comb or spine).

H-tree

在H树形结构中,时钟源一般是放在中心。时钟信号先到达四角的缓冲器,然后又作为下一级H树的输入,如此类推。最后一级Htree作为局部区域类寄存器的输入缓冲器。这种对称架构保证了从时钟源到最后一级的缓冲器连线长度是相等的,在理想情况下,从时钟源到每个寄存器的延迟是相等的,skew也就等于0;但是实际情况下,由于工艺不确定性,还是会有偏差的。 缺点:H树虽然简洁优美,但是对布线要求较高,为了减少时钟延迟,水平和垂直的互连线只能处于相邻的布线层,灵活性较低。 二叉树结构

时钟源作为整棵树的根节点,底下每一级buffer作为树的分支,最后寄存器是整棵树的叶子节点。 优点:分支的buffer起到了隔绝前后级的作用,同时有利于恢复时钟信号强度,能够有效改善transition time, 进而有利于控制skew和整体的时钟延迟。 缺点:多级buffer,晶体管本身对于PVT/环境参数敏感,实际实现的clock tree效果和预期会有差异。 网格结构

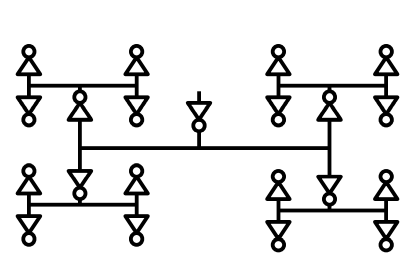

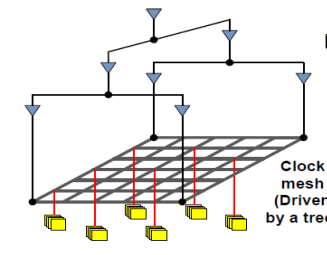

grid clock tree由于他有比较多冗余结构,可以有比较强的抗干扰能力和较小的skew. 如上图所示是一种典型的Htree+grid的时钟树结构,另外还有二叉树加上grid的结构。通常是在树的叶子节点有一个buffer, 该buffer同时出入网格的交叉点上。 优点:通常会有较小的skew, 并且有较好的抗干扰能力。 缺点:因为有比较多的冗余的互联,功耗会增加;芯片布局通常会有限制,比如会有电源线和布线障碍区,所以可能会出现无法实现grid的情况。 脊柱结构

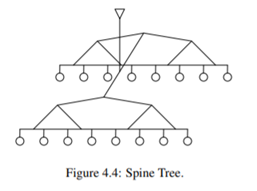

Clock spine(脊柱)是一个线上连接多个触发器,看上去就像一根脊柱一样,一般设计里面会有多个clock spine, 如右图所示有两个spine。

优点:通常会有较小的skew, 并且有较好的抗干扰能力。

缺点:clock spine 的叶子节点还需要加上连线优化到触发器才能满足skew要求。 参考 《数字集成电路物理设计》 《Digital vlsi design》 https://www.bilibili.com/video/BV1Dy4y187wL?p=8

https://www.physicaldesign4u.com/search/label/what%20is%20floorplanning?&max-results=7 https://zhuanlan.zhihu.com/p/96164213 https://www.vlsi4freshers.com/2020/01/clock-tree-synthesis-cts.html https://ivlsi.com/clock-tree-synthesis-cts-vlsi-physical-design/ https://vlsi-backend-adventure.com/cts.html https://core.ac.uk/download/pdf/190335797.pdf https://www.design-reuse.com/articles/21019/clock-mesh-benefits-analysis.html

|

【本文地址】

| 今日新闻 |

| 推荐新闻 |

| 专题文章 |