| 浅谈LVDS电路板设计 | 您所在的位置:网站首页 › 差分sstl › 浅谈LVDS电路板设计 |

浅谈LVDS电路板设计

|

随着集成电路的发展和对更高数据速率的要求,低压供电成为急需。降低供电电压不仅减少了高密度集成电路的功率消耗,而且减少了芯片内部的散热,有助于提高集成度。减少供电电压和逻辑电压摆幅的一个极好例子是低压差分信号(Low Voltage Differential Signaling LVDS)。低电压差分信号(LVDS)是一种高速点到点应用通信标准。 多点LVDS (M-LVDS)则是一种面向多点应用的类似标准。LVDS和M-LVDS均使用差分信号,通过这种双线式通信方法,接收器将根据两个互补电信号之间的电压差检测数据。这样能够极大地改善噪声抗扰度,并将噪声辐射降至最低。 LVDS是一种用于替代发射极耦合逻辑(ECL)或正发射极耦合逻辑(PECL)的低功 耗逻辑 。LVDS的主要标准是TIA/EIA-644。有时也会对LVDS使用另一种标准,即IEEE 1596.3—SCI(可扩展一致性接口)。LVDS广泛用于高速背板、电缆和板到板数据传输与时钟分配,以及单个PCB内的通信链路。 LVDS的优势包括: •通信速度高达1 Gbps或以上•电磁辐射更低•抗扰度更高•低功耗工作•共模范围允许高达±1的接地失调差额 差分传输 LVDS采用差分传输方案,这意味着每个LVDS信号都使用两条线路。这两条线路之间的电压差定义了LVDS信号的值。为了通过差分迹线成功传输LVDS信号,在布置电路板时应遵循以下指南。 为了确保反射最小,并保持接收器的共模噪声抑制,在差分迹线离开驱动IC后,尽可能靠近它们。此外,为了避免差分阻抗的不连续性,差分LVDS信号之间的距离应在迹线的整个长度上保持恒定。 为了最大限度地减少偏斜,差分LVDS迹线之间的电气长度应相同。其中一个信号在另一个信号之前到达会在信号对之间产生相位差,这会通过减少可用的接收器偏斜裕度(RSKM)来损害系统性能。 最小化信号路径上的过孔或其他不连续性的数量。 任何寄生负载,例如电容,必须以相等的量存在于差分对的每条线上。 .为避免信号不连续、电弧或45°建议使用迹线而不是90°转弯。阻抗匹配 由于LVDS的高速性,阻抗匹配非常重要,即使在很短的运行时间内也是如此。差分LVDS迹线中的任何不连续性都将导致信号反射,从而降低信号质量。这些不连续性还会增加共模噪声,并将作为EMI辐射。LVDS输出是电流模式输出,需要一个端接电阻器来闭合回路,没有电阻器端接将无法工作。这个的价值终端电阻器被选择为匹配传输线的差分阻抗,并且可以在90Ω至110Ω(通常为100Ω),图1显示了终端电阻器的正确使用。

选择LVDS通道的终端电阻器时,应注意以下指南 将端接电阻器放置在差分互连远离变送器的远端。单个100Ω电阻器就足够了。 使用表面贴装厚膜0603或0805尺寸的片式电阻器。 将端接电阻器安装在接收器7 mm范围内,尽可能靠近接收器。LVDS和单端信号之间的串扰 为了减少LVDS和单端信号如LVTTL、SSTL-3、SSTL-2和类似标准之间的串扰,差分LVDS信号必须与单端信号隔离。如果LVDS和单端信号没有彼此充分分开放置,则单端信号可能会对差分对造成一些干扰。最靠近单端信号轨迹的LVDS信号将比更远的信号轨迹受到更大的影响,从而产生不会被LVDS接收器作为共模噪声拒绝的差异。这种干扰不太可能导致LVDS接收器错误触发﹔然而,它将降低LVDS信号的信号质量,从而降低噪声容限。在同一PCB层上,单端信号应放世在距离LVDS信号至少12mm的位置,以避免串扰效应。vcc和接地平面也可用于将LVDS信号层与单端信号层隔离。图2显示了使用电源平面对LVDS层与单端层的屏蔽。

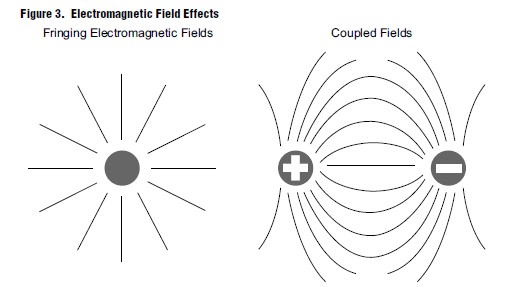

电磁干扰 电磁辐射通常引起设计者的关注,因为这种辐射可以通过横向电磁波传播。这些波可以通过屏蔽逃逸,导致系统无法通过电磁兼容性(EMC)测试。对于单端传输,如CMOS或TTL,几乎所有的场线都可以自由地从导体辐射出去。其中一些场线可以作为TEM波传播,这可能会逃离系统,从而导致EMC问题。 对于LVDS差分信号,场线往往相互抵消,电场往往耦合。这些耦合的场彼此捆绑在一起,因此不允许逃逸。只有少数边缘场从这种耦合中逸出。因此LVDS作为差分传输系统与CMOS或TTL信号相比产生更少的EMI。图3显示了单端迹线和差分对中的电磁场效应。  LVDS信号可以在PCB微波带(外层)和带状线(中间层)上布线。图4显示了LVDS在外层和中间层的电磁场辐射。

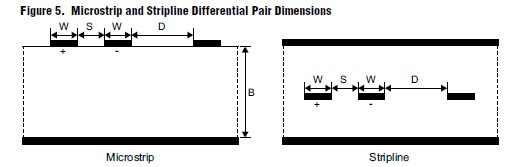

对于外层,下面的接地平面耦合额外的场线,从而束缚更多的场线并减少EMI效应。中间层耦合所有场线,从而显著降低EMI,但也有以下缺点∶ 比外层的传播时间高得多(通常是一倍半) 需要额外的过孔 需要更多层 难以达到100Ω精确微分阻抗 为了使磁力线具有最大耦合,差分对的两个导体之间的空间应保持在最小值。图5显示了中间层和外层线对的尺寸。 为了在差分对内获得更好的耦合,使S |

【本文地址】