| 异步FIFO学习 | 您所在的位置:网站首页 › 声母23个怎么读 › 异步FIFO学习 |

异步FIFO学习

|

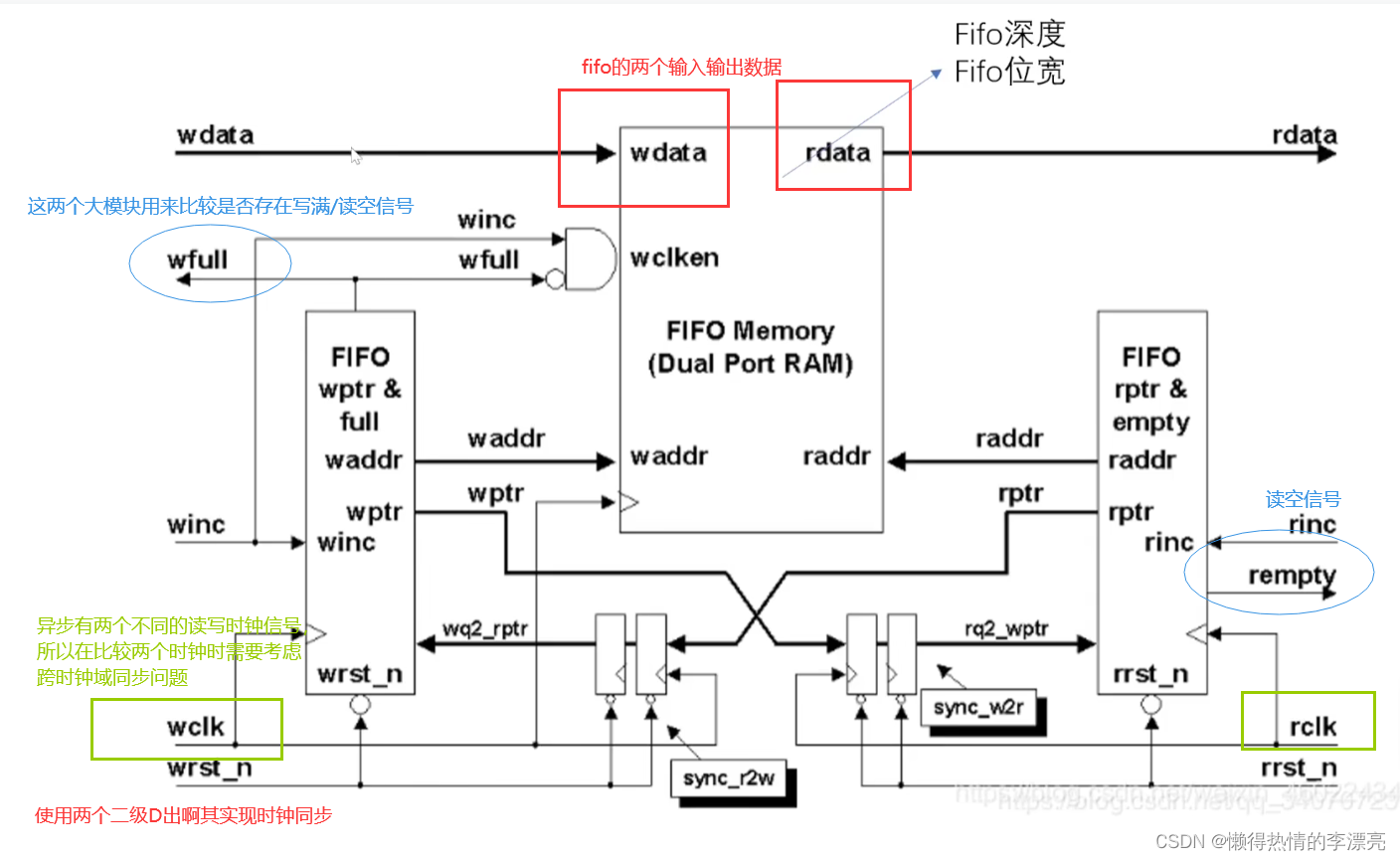

一 FIFO基本介绍及原理框图

FIFO基本框图如下:first in first out,数据缓存器,在实际项目中的硬件依赖是一块RAM,通常用于接口电路的数据缓存。只能顺序写入数据和顺序读出数据,不能像普通存储器那样由地址线决定读取或者写入某个指定地址。 FIFO深度:这个存储器可以写入多少个数据。 FIFO位宽:每个数据的宽度是多少位。

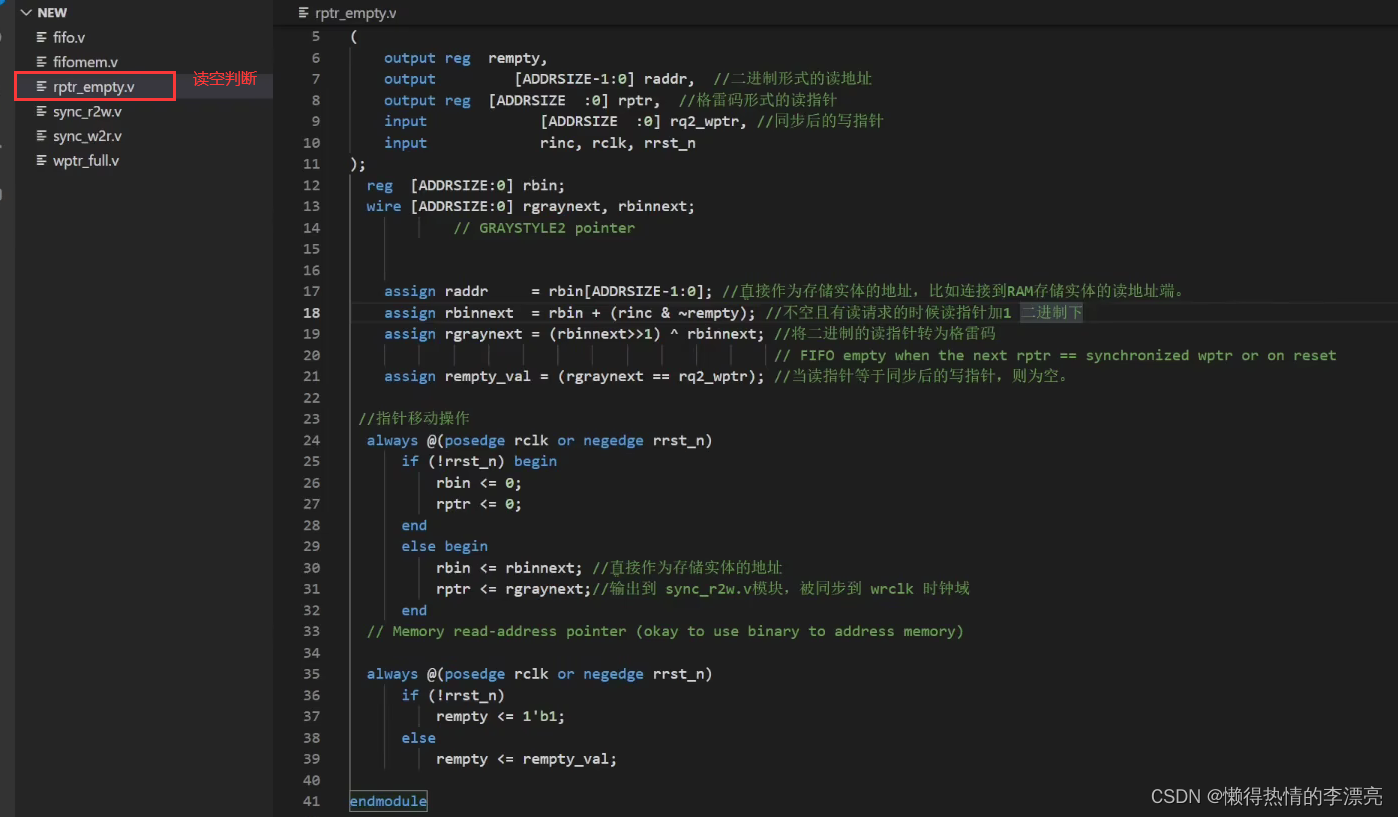

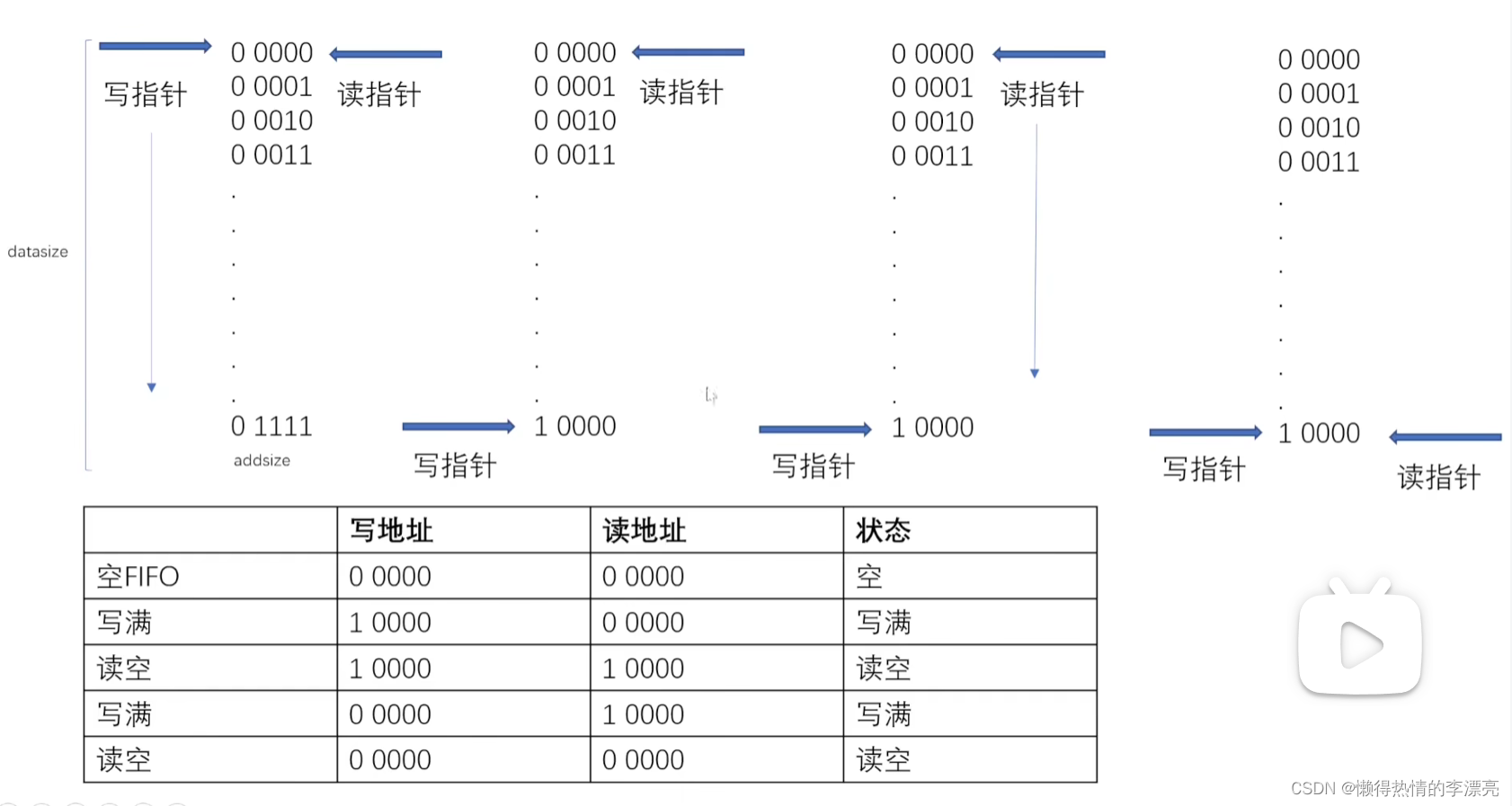

wdata和rdata是RAM的输入和输出,涉及有同步时钟和异步时钟(即同步FIFO,异步FIFO)。 两组数据(wdata和rdata)就涉及两组数据的地址:即waddr(写地址)/raddr(读地址)这个信号线告诉你此时此刻将数据(wdata)写到了FIFO的哪个部分。 问题:判断FIFO是否读空?or写满?,因为FIFO在被读空不能再被继续读出或者写满不能再继续写入。解决:关键在于读写时钟的地址,通过读写时钟的读写地址的指针【wptr(写指针) / rptr(读指针)】来判断FIFO 的空满状态。(因为一般是一个上升沿写/读一个数据,在写/读一个数据后,指针+1指向下一个空间) 读写时钟域的同步问题:硬件是使用二级D触发器实现。(因为异步FIFO的读写时钟是不一样的,所以在比较两个时钟的时候需要考虑这个问题,比如比较读时钟读指针,必须把写指针先同步到读时钟域下才可以。

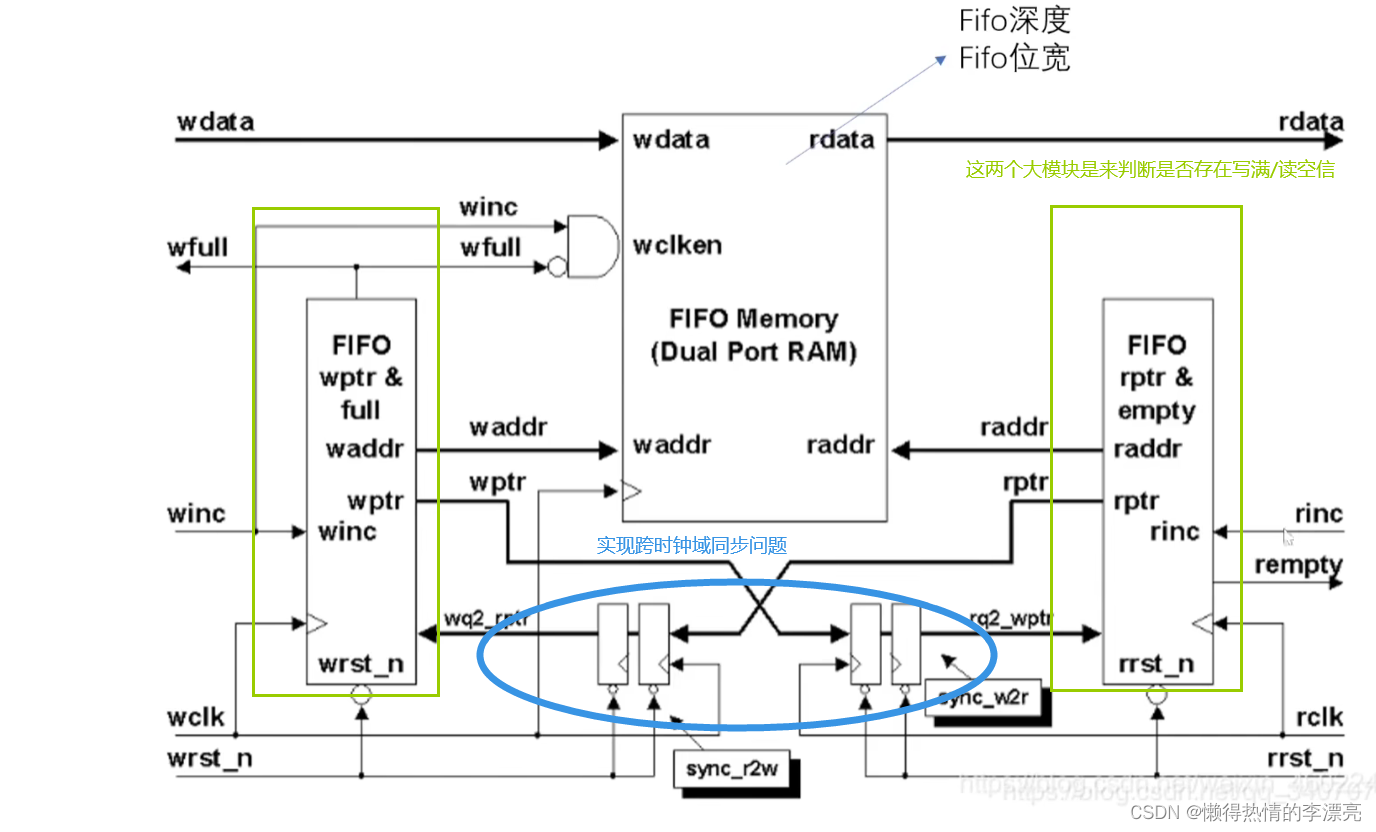

简化的简单框图为:

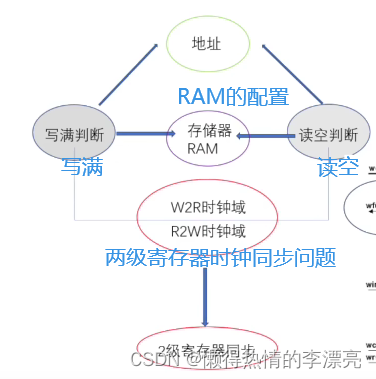

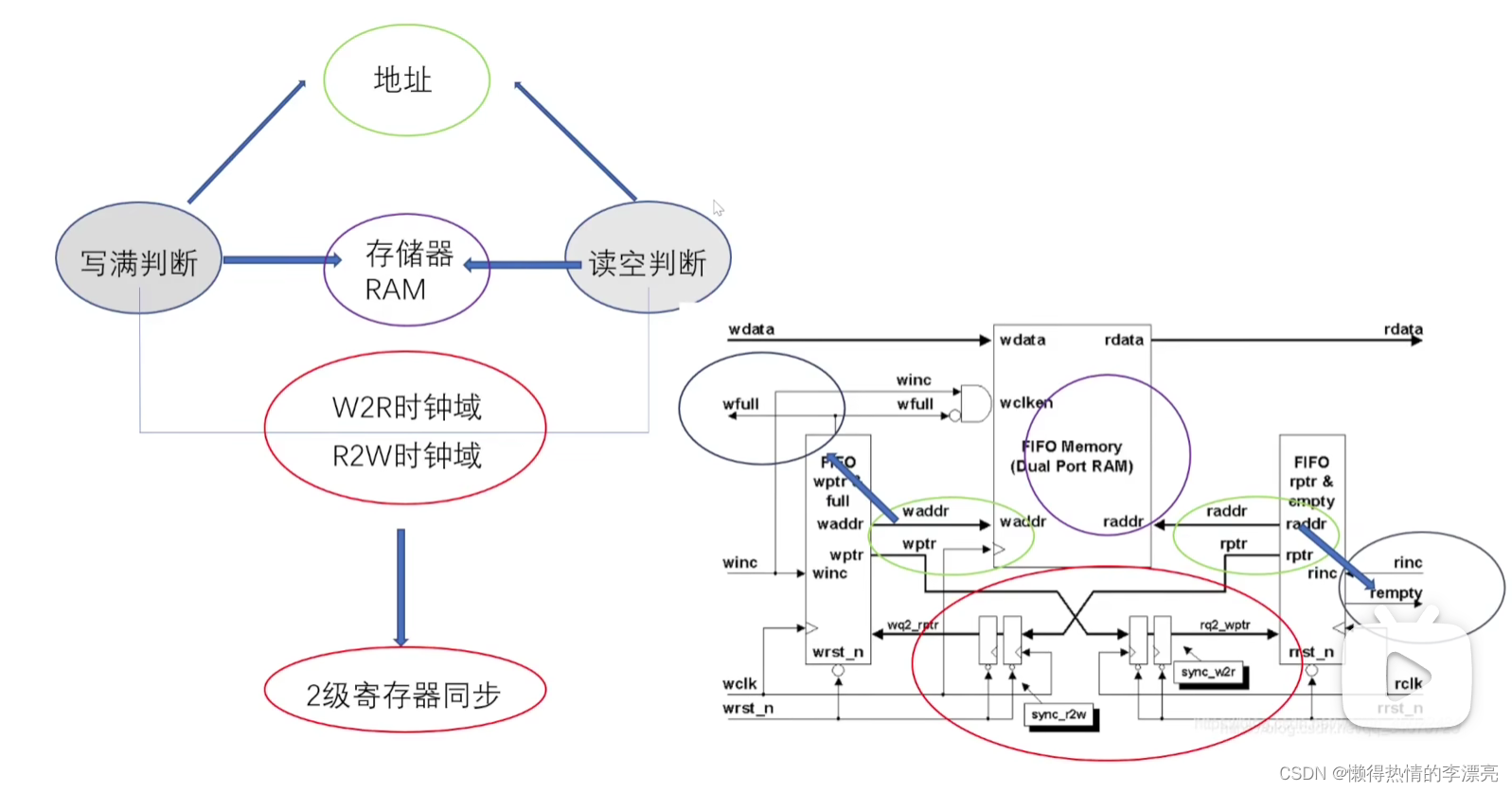

整体逻辑:FIFO最基础的部分是一块RAM存储器,通过外围各种算法设置(写满读空判断、时钟等)让这个RAM实现先进先出的功能。 判断这个存储器写入读出的状态需要进行两次判断,即写满和读空判断,在硬件中是通过两个信号判断的(wfull:写满信号,rempty:读空信号),如何得到这两个信号?通过waddr(写地址)wptr(写指针),和raddr(读地址) rptr(读指针),通过比较读写地址指针来判断FIFO是否写满和读空。在比较的时候涉及跨时钟域的问题,因为是异步FIFO,所以读写的时钟不一样,需要将写入的时钟同步到读的时钟上。 二 如何判断生成空满信号写指针是循环的,满了直接回0,先写先读,

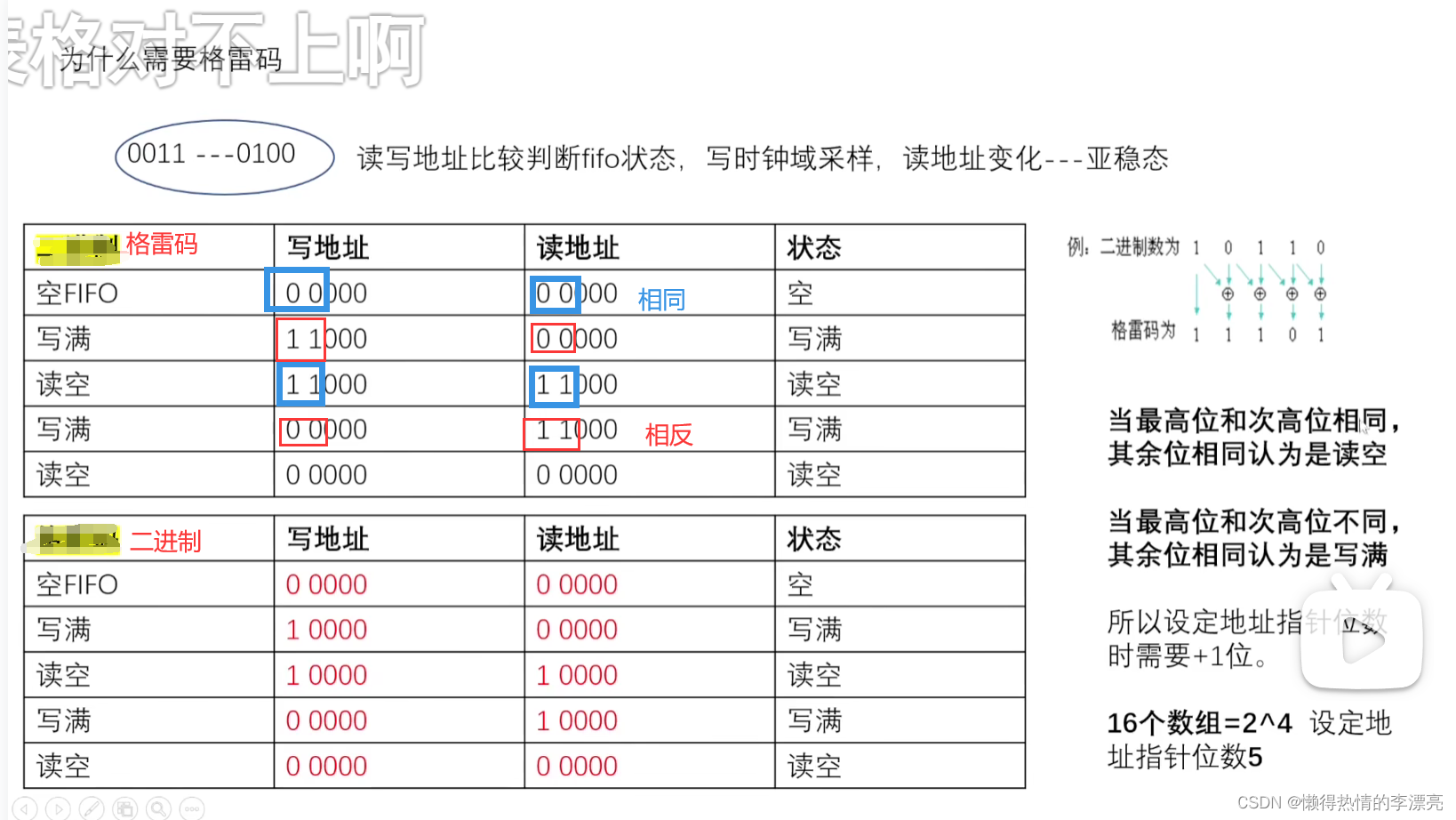

note:需要用格雷码,用读写地址的比较来判断FIFO的状态,写时钟时候采样及读地址变化的时候很容易出现亚稳态的情况。

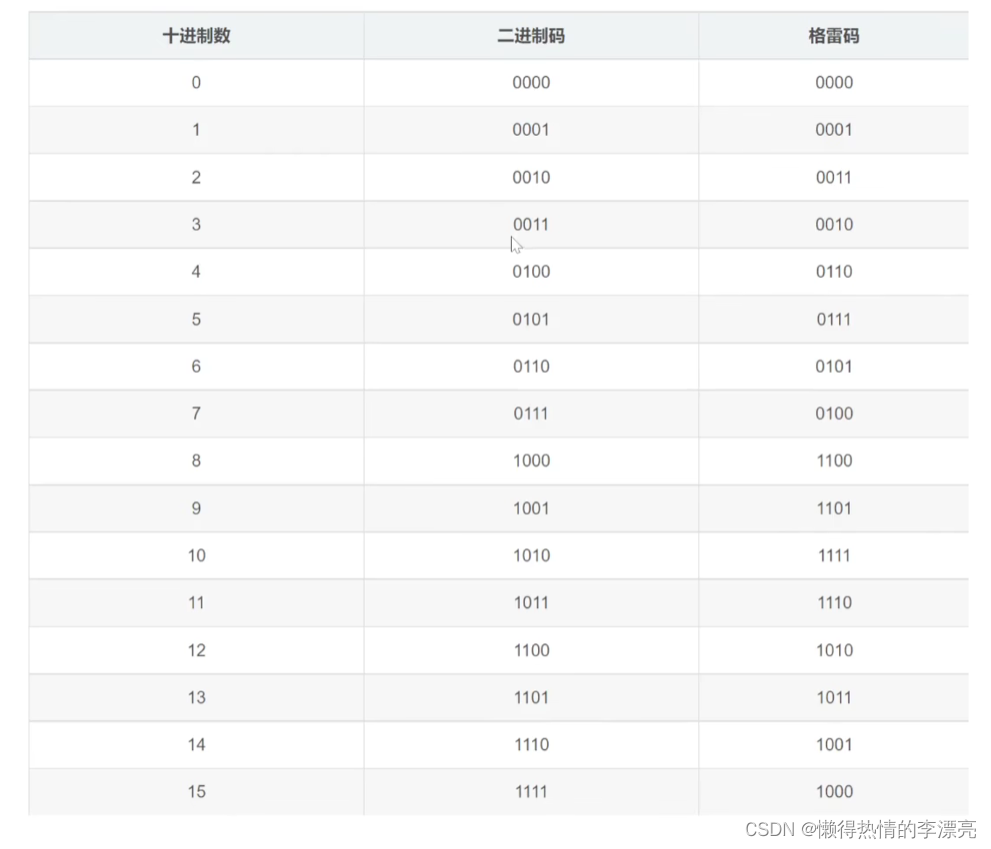

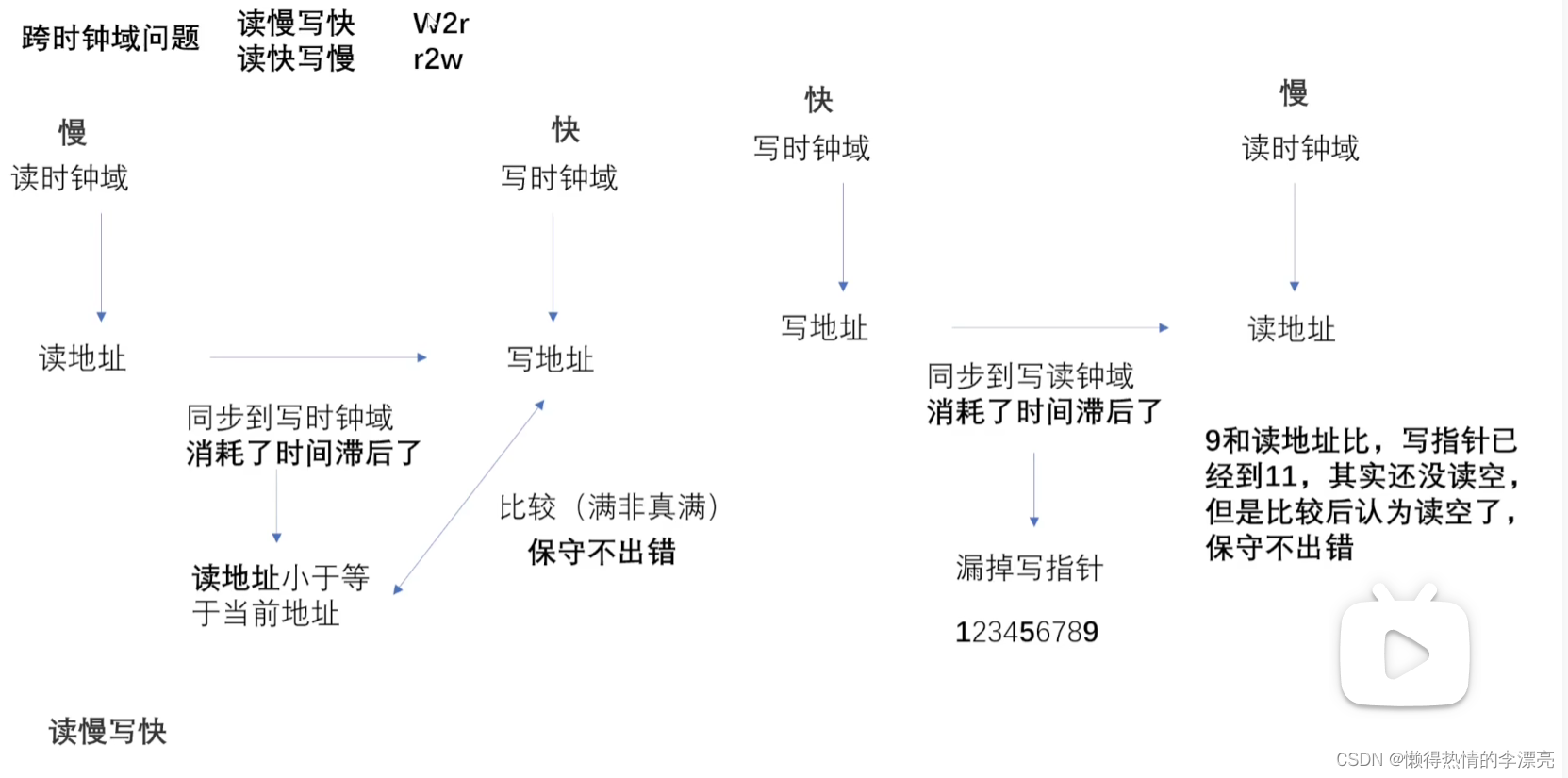

将读写地址指针的二进制编码转换位格雷码为:

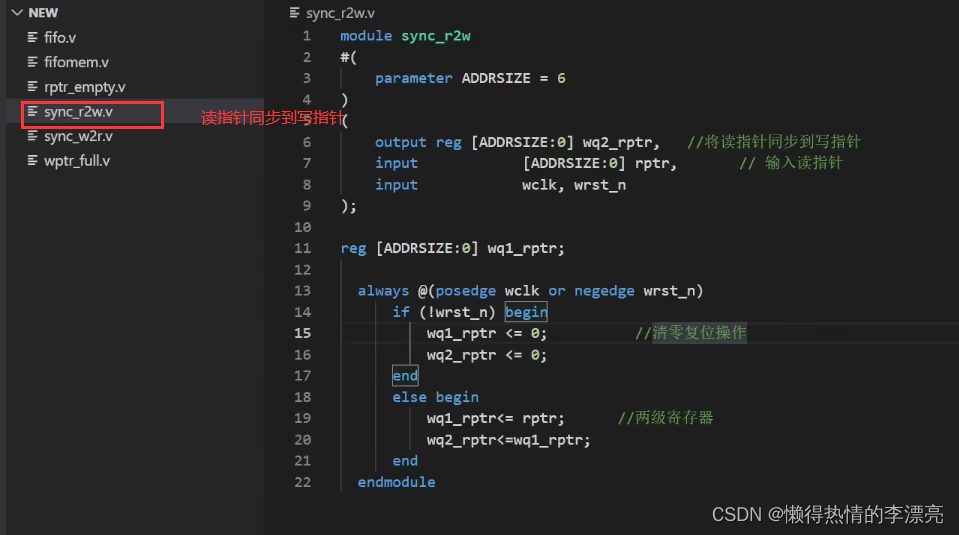

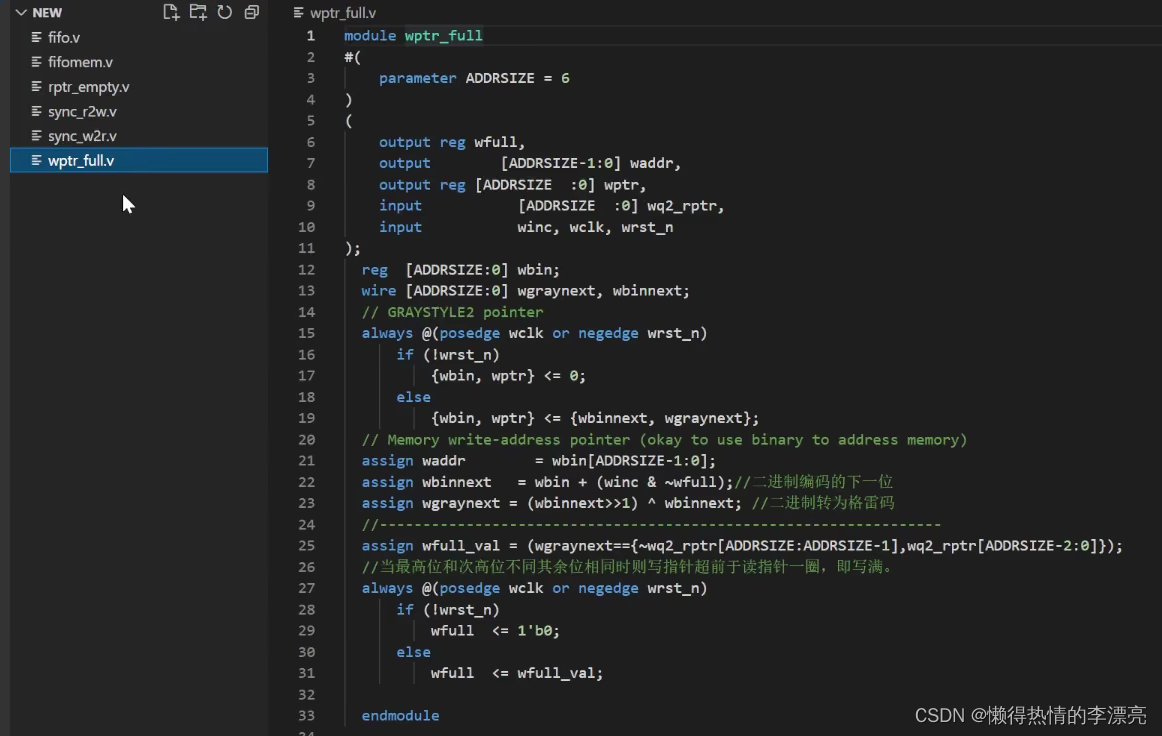

规律————写满状态时候:左端两位最高位和次高位相反,其他位相同 ————读空时候:左端最高位和次高位相同的,其他位相同。 note:假如FIFO深度为16的话,二进制需要4位即可存储地址位了,为什么会有5位?(设定地址指针位数时需要+1) 原因:判断读空写满的时候是利用的进位端来判断的状态的,即是进位端和次高位来结合判断。 三 跨时钟域的问题因为异步FIFO的读写时钟是不一样的,要比较读时钟的地址指针和写时钟的地址指针的时候,肯定要把他们规到同一个时钟域下才能够比较。所有情况分为4类:读慢写快,读快写慢,同步(硬件上使用两级寄存器实现, 寄存器同步消耗时间,对FIFO的性能有影响,功能没有影响):要么将读时钟同步到写时钟,要么将写时钟同步到读时钟。 以读慢写快为例:当读时钟慢,写时钟快的时候, 1. 想要把(慢的)读时钟域的地址同步到(快的)写时钟域,读地址经过两级D触发器后(消耗了时间被滞后了,此时的读地址是小于等于实际的读地址的)与写地址比较,此时小的读地址(读的更慢)与写地址(写的本来就快)比较得到满信号(不是真的满),这样的目的是,实际上它没有写满但是我认定它写满了就不会再往里面写入数据(就是我们防止FIFO在写满的时候再被写,宁愿让它还没写满却认为是写满的状态这样比较保守不会出错 ) 2. 把(快的)写时钟域的写地址同步到(慢的)读时钟域的读地址时:写地址经过两级D触发器后(消耗了时间被滞后了,所以可能会漏掉一些写指针,假如同步后的写地址是9,实际的写指针已经到11了,其实认为还没有读空,但是认为已经读空,这样不会出现读空错误) 舍弃FIFO的性能,保证FIFO的功能不出错

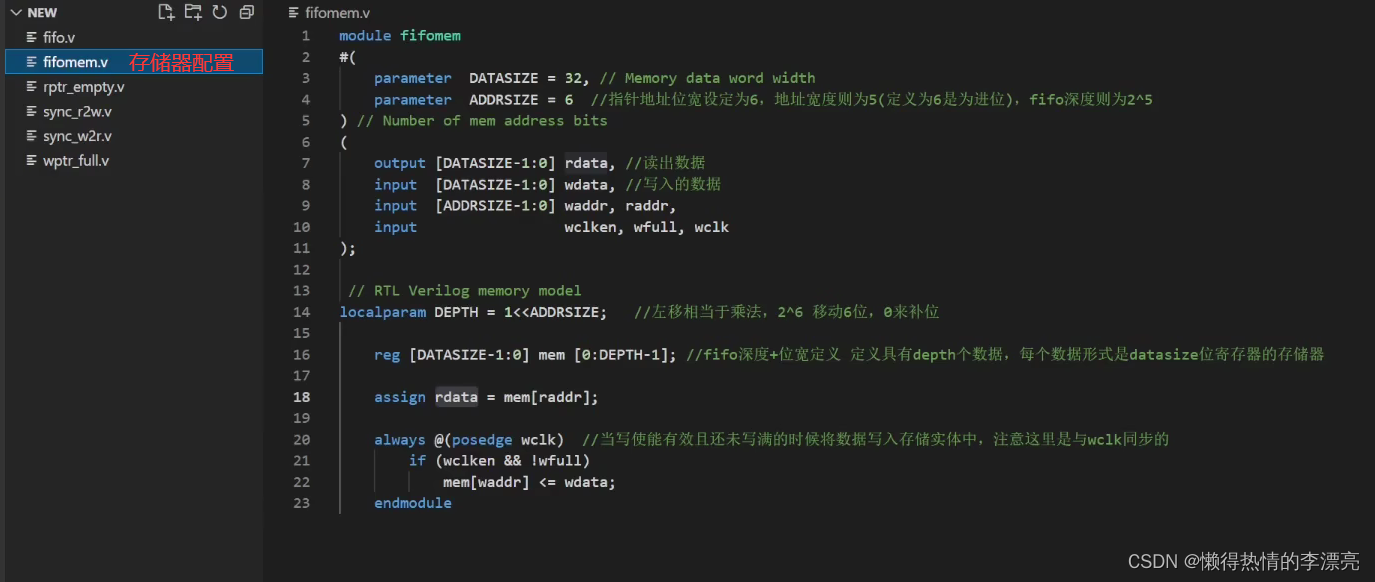

在编写FIFO的时候需要注意的原理和特点: 1.首先需要配置FIFO的存储器模块{FIFO深度决定读写地址的位数和读写指针的位数(在读写地址位数的基础上+1,因为需要靠进位和次高位判断是否写满和读空)和宽度} 2.两级寄存器来实现时钟域同步的问题,寄存器同步必然导致FIFO滞后,但是不会影响功能。 4个子模块为:

RAM的配置

包括 深度和位宽 读空判断

时钟域同步:读指针 同步到写指针,利用两级触发器,输入读指针, 写满判断:

|

【本文地址】

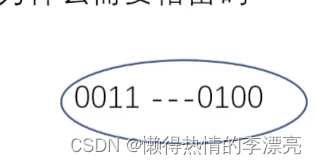

这里面有三位的数据发生了变化,并不能保证此时此刻采的就是准确的0100,变化的数据位数多,容易出现不确定的情况(多bit位传输的时候很容易出现亚稳态的情况),相比二进制编码,格雷码的优势在于相比前后状态每次只变化一位。

这里面有三位的数据发生了变化,并不能保证此时此刻采的就是准确的0100,变化的数据位数多,容易出现不确定的情况(多bit位传输的时候很容易出现亚稳态的情况),相比二进制编码,格雷码的优势在于相比前后状态每次只变化一位。