| 【数字电路】设计计数器:采用与非门和74390设计一个模24的计数器 | 您所在的位置:网站首页 › 同步计数器和异步计数器的优缺点 › 【数字电路】设计计数器:采用与非门和74390设计一个模24的计数器 |

【数字电路】设计计数器:采用与非门和74390设计一个模24的计数器

|

1.设计任务

利用 74390 设计一个模 24 的计数器,观察 LED 灯的计数状态,用示波器同时观察 CP 和输出端最高位的波形,绘制波形图。

2.设计前知识

74390芯片(双2-5-10进制异步计数器)

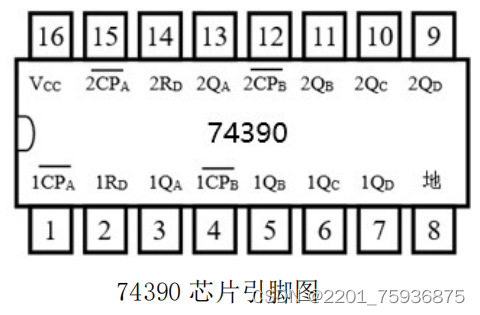

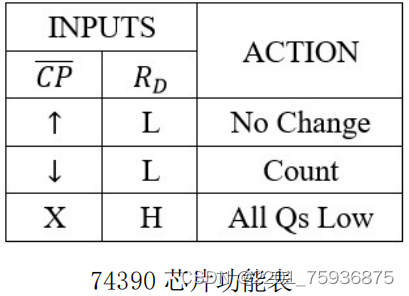

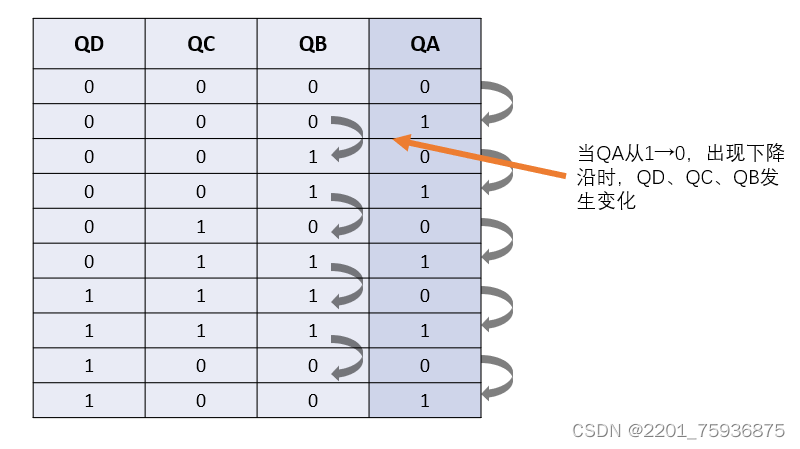

74390内部有两组计数器,每组计数器由一个二进制计数器与一个五进制计数器组成。 故每组计数器有CLKA、CLKB两个计数时钟输入, 整个芯片两组计数器总共有四个计数时钟输入。 二进制计数器的时钟输入为CLKA,输出为QA;五进制计数器的时钟输入为CLKB,输出为QD、QC、QB。(如左图) 当一个二进制/五进制计数器收到下降沿,并且前提是RD=0时,计数器就会计数。当完成模的计数时,把RD=1,清零。(如右图) 关于进制的实现当输入一个下降沿给CLKA时,二进制计数器计数,它只需要一位即可实现二进制,所以QA从0-1-0-1-0......不断变化。 当输入一个下降沿给CLKB时,五进制计数器计数,它需要三位来实现五进制,所以QD/QC/QB从高位到低位依次从000变到100。 QDQCQB000001010011100当把QA接到CLKB,也就是把二进制计数器的输出连到五进制计数器的时钟输入,就可以构成一个十进制计数器。当QA发生一个下降沿时,QD、QC、QB就会发生改变。

如何实验3进制?采用5进制计数器,当计数器计到三的时候清0即可。 那么如何实现任务要求的24进制?已知74390有两组计数器,每组有五进制和二进制,那么就可以看做74390有两组10进制,把第一个十进制的最高有效位接到第二个十进制的最低有效位使第一个计数器的下降沿作用到第二个计数器上,就可以实现最多100进制的计数器。当计数到24的时候把RD=1,就可以清零,实现24的计数器。 3.设计思路3.1 首先列出计数状态表 2QD2QC2QB2QA1QD1QC1QB1QA2RD1RD0000000000000000010000000010000000001100000001000000000101000000011000000001110000001000000000100100000100000000010001000001001000000100110000010100000001010100000101100000010111000001100000000110010000100000000010000100001000100000100011000000000011# 最后一行RD=1,使得清零。 3.2 写表达式 1RD=2QB*1QC(当最后一次为00100100的时候,令RD=1,变为00000000) 写出这个表达式的目的是为了连接1RD、2RD引脚。 3.3画出电路连接图

*画电路连接图要参照引脚图 *用一个7474两次与非门实现与运算(2QB*1QC) 以上就是设计的整个思路和过程。 |

【本文地址】