| SAC(Self | 您所在的位置:网站首页 › 半导体工艺制程中CT是什么 › SAC(Self |

SAC(Self

|

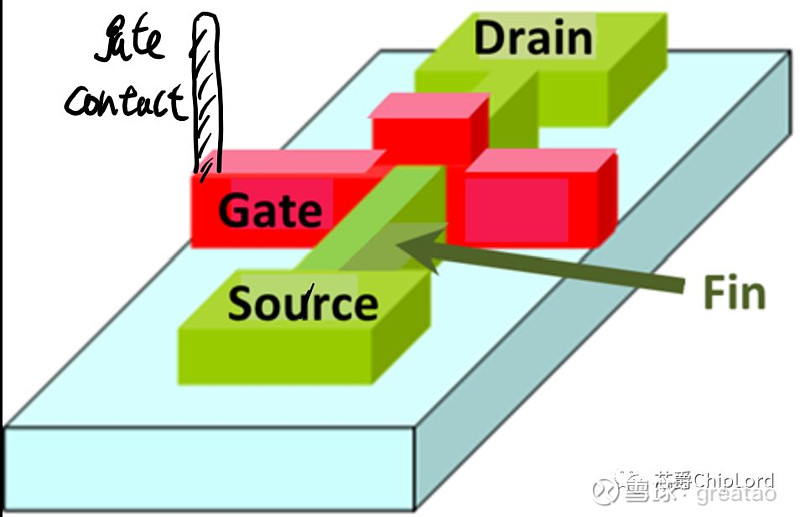

来源:雪球App,作者: greatao,(https://xueqiu.com/1958668676/143379961) Intel 22nm工艺中,关于contact连线有个细节工艺叫SAC,全称叫self-aligned contact,中文翻译叫自对准接触,有读者后台留言想了解具体细节,这篇文章详细介绍下SAC工艺。 简单来说说,SAC工艺就是在栅极gate上方添加一层保护性介电层,目的是防止源,漏极的contact与栅极gate短路。主要原因是当时contact的pitch越来越小,source/drain contact很容易发生偏移,造成与gate短路,最终导致low yield。

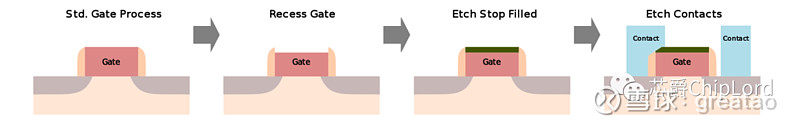

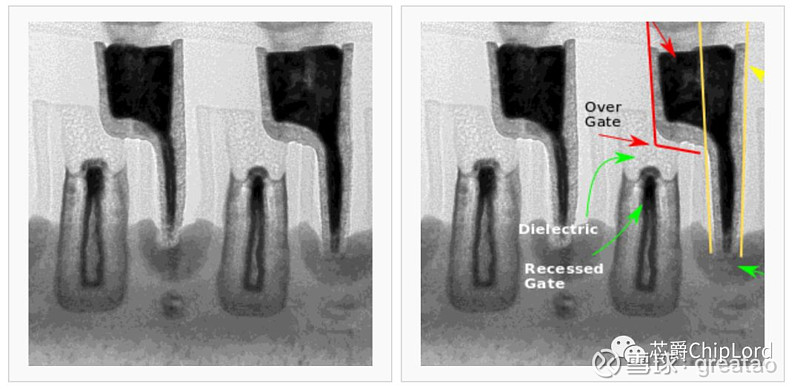

Intel在其22nm FinFET工艺中首先推出SAC flow,主要是添加了三个步骤,具体流程如下: Intel标准工艺形成metal gate metal gate向下凹陷 向下凹陷的区域中填充氮化硅etch stop layer然后CMP磨平 然后覆盖一层氧化硅 最后进行contact patterning

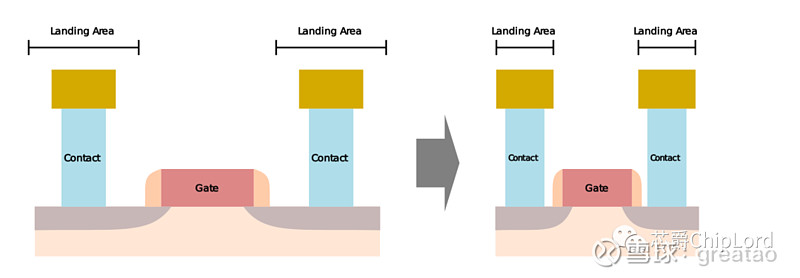

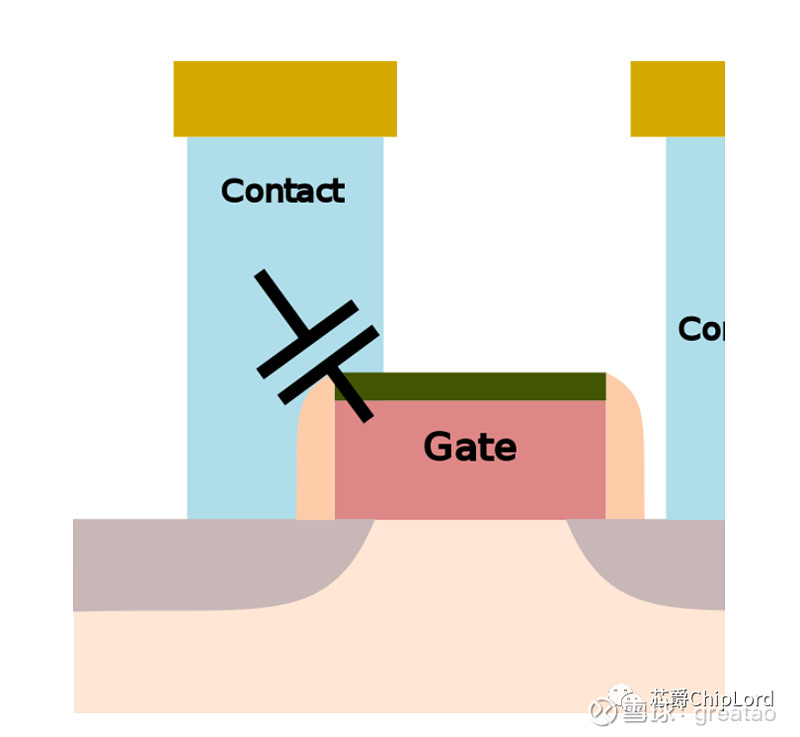

最主要差异就是在metal gate的上面添加一层氮化硅和氧化硅,这样即使source/drain的contact overlaid on metal gate上,由于氮化硅介电质存在,也不至于短路,这样就大大提高了misalignment margin。

上面的二维图可能不好理解,这里要说明的是,Gate上也有contact,但是和source/drain的contact不在同一水平面位置,所以source/drain的contact发生偏移,即使和gate接触了,只要没有和gate下面的金属接触都没有关系,不影响正常连线。

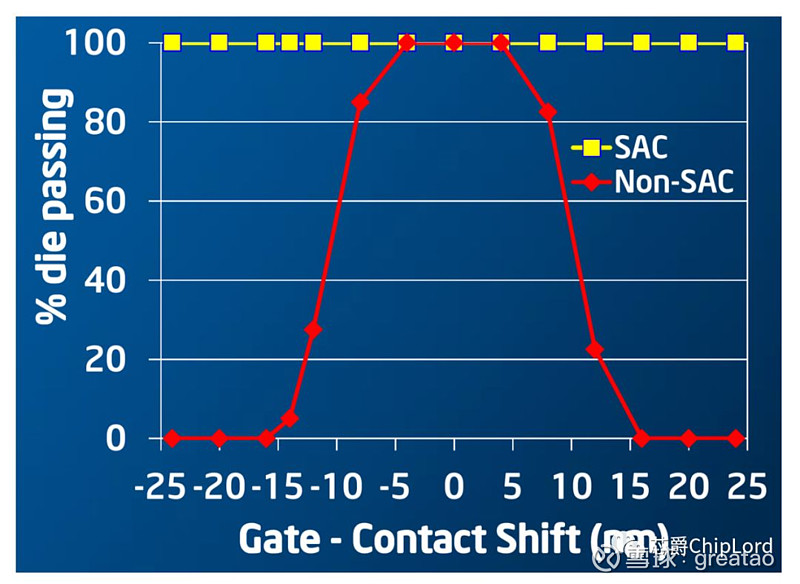

如果没有SAC flow,Intle 22nm制程中contact misalignment margin只有+-5nm,10nm左右的misalignment就会造成20%左右的yield loss,但是增加了SAC flow以后,gate 到 contact的shift margin可以达到25nm,良率显著提高。

现在看来,SAC flow很简单,只不过了增加几步process,但是这在当年很有创造性,而且效果非常明显,大大提高了良率,不得不说intel的工程师还是非常厉害的。 以上,希望大家都能看懂上述介绍,有问题欢迎留言,谢谢! 我从油管上搬了一个印度小哥介绍SAC的英文视频,无奈腾讯还没审核通过,下次放上来吧,之前有个介绍三星FinFET工艺的视频,大家有兴趣可以点击看看。 网页链接 长按 识别图中二维码即可关注

你点的每个赞,我都认真当成了喜欢 |

【本文地址】