| CMOS设计手册 | 您所在的位置:网站首页 › 半导体vth为啥要短接gd › CMOS设计手册 |

CMOS设计手册

|

模拟CMOS

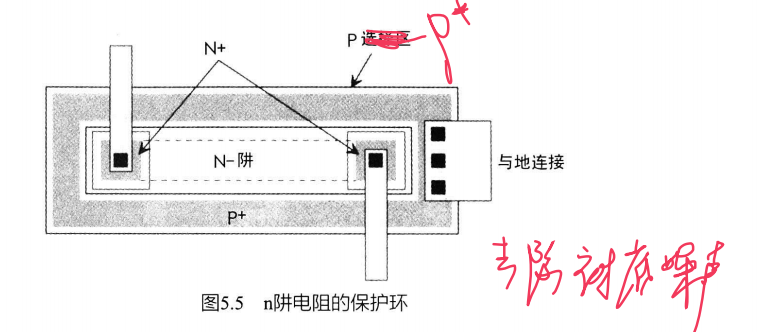

衬底噪声:由于相邻的电阻互相注入电流而产生的衬底噪声。解决方法:在两个电阻之间加入一个P+注入区(作为P衬底晶圆的衬底接触)。P+注入区保护电路免受载流子的影响,由于注入区是一个环形,所以成为保护环。

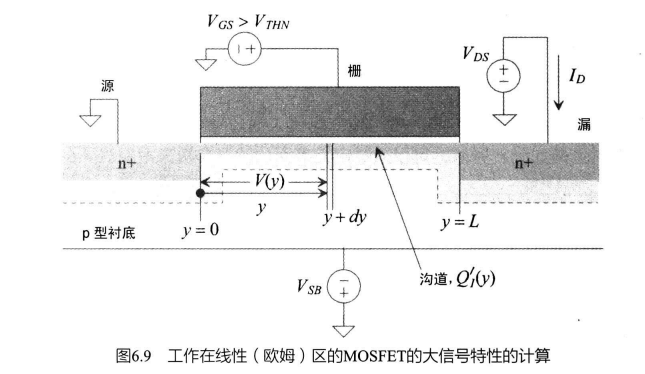

共质心版图 共质心(共同的中心)版图有助于改善两电阻之间的匹配性能(代价是两元件之间具有不均匀的寄生特性),另外,共质心也能改善MOS和电容的匹配性能。 3.MOS电容 堆积 (VGSVth,VdsVth,所以在栅氧化层下的表面会反型,因为Vds>0,所以有漂流电流从漏端流向源端。

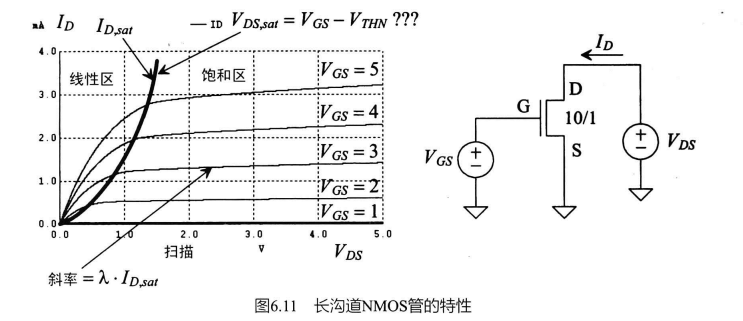

饱和区(Vgs>Vth,Vds>Vgs-Vth) 当Vds=Vgs-Vth时,栅电极下方(漏极与沟道的汇合处)沟道中的反型电荷为零,这个漏端和源端之间的电压被称为Vds,sat=(Vgs-Vth),它表明沟道在漏端和沟道交界处被夹断。增加Vds并超过Vds,sat,会将固定电荷吸引至漏端,从而使得沟道中紧临漏端的电荷被耗尽。继续增加并不会使漏端电流继续增加(由于沟道长度调制效应会使漏端电流随着漏端电压增加而增加) \[I_D=\frac {1}{2} β(V_{GS}-V_{TH})^2(1+λV_{DS}) ,λ=\frac {1}{L}\frac {dX}{dV_{DS}} \]迁移率会随着Vds变化而变化,

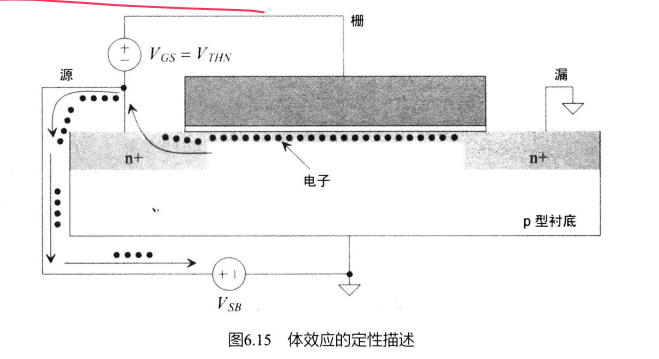

沟道长度调制效应和体效应效应 沟道长度调制效应:当栅和漏端之间的电压差减小时,实际的反型沟道长度在减小,这称为沟道长度调制效应。 体效应:当\(V_{SB}\)开始增加时,阈值电压也开始增加,这被称为体效应。电子从沟道中被吸引到了\(V_{SB}\)的正端,为了保持表面反型,必须要在mosfet上施加一个更大的\(V_{GS}\)。于是从沟道中获取电子带来的效果就是MOSFET的阈值电压增加了。

|

【本文地址】

公司简介

联系我们