| 译码器实验总结(八篇) | 您所在的位置:网站首页 › 加法器与译码器实验报告 › 译码器实验总结(八篇) |

译码器实验总结(八篇)

|

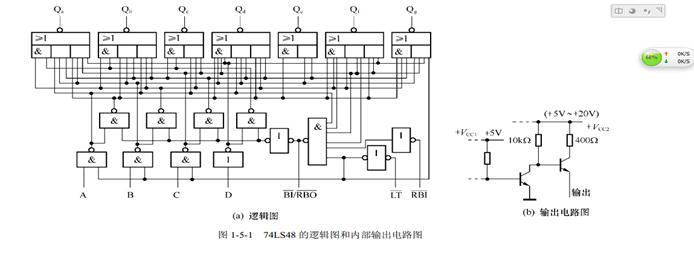

数字电路逻辑与设计实验报告 实验名称:译码器及其应用 实验目的: 1. 掌握数码管的使用方式及显示原理 2. 掌握中规模集成七段显示译码器74LS48的功能,以及进行功能测试。 3. 了解多位数码显示电路的组成及原理,通过multisim进行仿真验证。 实验原理: 译码器是一个多输入、多输出的组合逻辑电路,它能把给定的一组组代码译成一个个相应的输出状态或一组组新的代码,以表示编码时赋予的原意。完成这种译码功能的电路称为译码器。它不仅可用于数字显示,而且可用于代码转换、数据分配、存储器寻址和组合控制信号等方面。 本次试验采用的是74LS48七段显示译码器,下面介绍些七段显示译码器的工作原理。 74LS48是七段显示译码器,其逻辑图、内部输出线路如图 1-5-1(a)和(b )所示,逻辑符号见附录,其功能表如表 1-5-1所示。它由全译码器和辅助功能控制电路两部分组成,功能较全。全译码器的工作情况详见功能表1-5-1。从功能表可知,当输入码大于十进数9时,七段显示器仍显示一定的图形。从而可鉴别相应的输入情况。辅助控制端有三个。

① LT—试灯信号输入端。用于检查显示数码管的好坏,当LT=0、BI=1时,七段全亮,显示“日”。这表明数码管是好的,否则是坏的。 ② BI—熄灭控制信号输入端(与灭零信号输出端共用该端)。用于间歇显示的控制,当BI=0时不论输入DCBA 和其他辅助控制信号是什么状态,七段全灭。 …… …… 余下全文 |

【本文地址】

公司简介

联系我们