| Verilog位宽转换器参数化设计 | 您所在的位置:网站首页 › 位宽不匹配怎么解决 › Verilog位宽转换器参数化设计 |

Verilog位宽转换器参数化设计

|

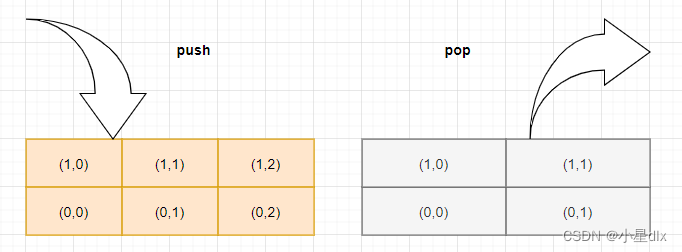

摘要:Verilog 位宽转换 参数化设计 1、应用场景 Verilog位宽转换应用场景很多,比如ADC数据采集存储,CameraLink数据采集存储等很多需要进行位宽转换的地方都需要用到。换句话说,只要输入输出位宽不匹配,就会用到。常规的位宽转换方法有FIFO IP、以及移位寄存器等。但如果输入输出位宽之间不是整数倍的关系又该如何处理?大概都会想到用移位寄存器+计数器+数据选择器实现。那么有没有一种通用写法呢?这里说的通用写法也就是可不可以实现参数化。 2、工程实现 我想到的一种实现方式是参考FIFO的思想,如果有人有其他更好的方法欢迎交流学习。和一般的FIFO只有一维指针不同,这里用到了二维指针。大致示意图如下:

模块代码: // 时间:2023-03-17 // 作者:xiaoxingdlx([email protected]) // 模块:位宽转换示例 module unit_wide_convert #( parameter simTdly = 1, // 仿真延时参数 parameter dinWidth = 4, // 输入数据位宽 parameter doutWidth = 8, // 输出数据位宽 parameter bufWidth = 16, // 缓存数据位宽(输入和输出位宽最小公倍数的整数倍) parameter bufDeepth = 1, // 缓存数据深度(2^N) parameter ptrWidthW = 2, // 写指针位宽(内部指针,根据缓存数据位宽/输入数据位宽-1为最大值计算) parameter ptrWidthR = 1 // 读指针位宽(内部指针,根据缓存数据位宽/输出数据位宽-1为最大值计算) ) ( input wire clk, // 时钟 input wire reset, // 复位,高有效 input wire [dinWidth-1:0] din, // 数据输入 input wire din_vld, // 数据输入valid信号 output wire din_rdy, // 数据输入ready信号 output wire [doutWidth-1:0] dout, // 数据输出 output wire dout_vld, // 数据输出valid信号 input wire dout_rdy // 数据输出ready信号 ); // 获取二维指针内部指针的最大计数值 localparam WR_PTR_1_MAX = bufWidth/dinWidth - 'd1; localparam RD_PTR_1_MAX = bufWidth/doutWidth - 'd1; // 数据缓存 reg [bufWidth-1:0] buffer [2**bufDeepth-1:0]; // 二维写指针 reg [bufDeepth:0] wr_ptr_0; // 外部指针 reg [ptrWidthW-1:0] wr_ptr_1; // 内部指针 // 二维读指针 reg [bufDeepth:0] rd_ptr_0; // 外部指针 reg [ptrWidthR-1:0] rd_ptr_1; // 内部指针 // 二维写指针控制逻辑 always @(posedge clk ) begin if (reset) begin wr_ptr_0 |

【本文地址】

公司简介

联系我们