| 对如何使用WaveDrom画波形图的研究(案例分解分析) | 您所在的位置:网站首页 › wavecn软件怎么使用 › 对如何使用WaveDrom画波形图的研究(案例分解分析) |

对如何使用WaveDrom画波形图的研究(案例分解分析)

|

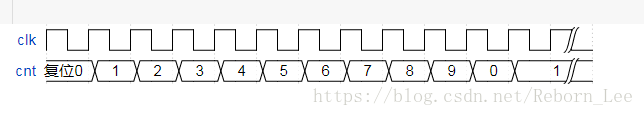

目录 背景介绍 工具介绍 案例分析: 案例一 偶分频电路波形图(以10分频电路为例) 奇分频(5分频为例) 案例二 结束语 背景介绍今天翻网页学习FPGA的相关知识时,无意翻到了一个画波形图的工具,激起了我的兴趣,有的时候我是需要画波形图的,用手画十分的麻烦且不标准,难以对齐,且要花费大量的时间,果然,前人大牛们已经经历了这个过程并写出了一个工具来解决此问题,真是有一种膜拜的感觉,我感觉自己真的很菜,需要学习的东西太多,想法很多,先是学会如何使用这个工具。画出一些基本的波形图。 本博文使用两个案例来说明如何画波形图,这两个案例,都是之前我写过的博文,由于波形图手画不标准(我没尺子),我就没有画,而是直接仿真得出的,这不利于原理分析,今天来完善下。顺便学会了这个工具的使用方法。 工具介绍首先贴出来工具的下载地址:Wavedrom 最上方有4个选项,第一个是tutorial(教程),点击进去,有软件或工具的使用方法,语法等。 第二个是Editor(编辑器),点击进去,就可以在线编写波形,无需下载软件,当然人家也把软件做好了,各种平台上的软件,真的很崇拜呀。 第三个是source,点击进去会进入这个开源项目的各种源文件,里面由所有你想知道的东西,就看你能不能看懂了。 最下方的第一项是Download editor,下载这个编辑器,可以离线编辑。 其他的自己查看吧,我就不介绍了。 再我的博文案例贴出来: 【FPGA】分频电路设计(Verilog HDL设计)(良心博文) 模6计数器以及模10计数器(Verilog HDL语言设计)(Modelsim仿真与ISE综合) 下面这段代码是这个工具默认的一段示例代码,先贴出来供大致了解,参观参观: {signal: [ {name: 'clk', wave: 'p.....|...'}, {name: 'dat', wave: 'x.345x|=.x', data: ['head', 'body', 'tail', 'data']}, {name: 'req', wave: '0.1..0|1.0'}, {}, {name: 'ack', wave: '1.....|01.'} ]}这段代码描述出来的波形图为: 从代码看,几乎可以说是一目了然,很容易上手,画出来的波形图也很美观,简直了。 虽然代码简单,但是细节还是需要认真的研究一下的,多找几个案例练手,达到熟练的目的。 案例分析: 案例一 偶分频电路波形图(以10分频电路为例)下面默认你看过这篇博文了,分频电路设计,不看也没关系,我说的直接一些吧。 这篇博文中要实现一个偶分频电路,原理是对时钟的上升沿进行计数,从0开始计数,计数到4(相当于经过了5个时钟周期),分频时钟clk_div翻转一次。 在Modelsim进行功能仿真得到的电路图如下: 下面我就要画出类似这个的原理图: 先看软件提供的示例代码: {signal: [ {name: 'clk', wave: 'p.....|...'}, {name: 'dat', wave: 'x.345x|=.x', data: ['head', 'body', 'tail', 'data']}, {name: 'req', wave: '0.1..0|1.0'}, {}, {name: 'ack', wave: '1.....|01.'} ]}从示例代码可以看出,这个波形描述语言的总体框架如下: {signal: [ ]}在两个中括号里面填充你需要描述的波形,首先是时钟波形描述如下: {signal: [ {name: 'clk', wave:'p...........|...'}, ]}每个波形的描述都在一个大括号内,别忘了大括号的结尾有一个逗号(,),name: 以及 wave:后面都要有一个' ',单引号内部写相关信息,例如波形名字(name),wave:'p...'中p代表一个时钟周期,后面的点是p的重复,有几个点就重复几次,p也算一次; wave:'p...|...'中,|代表省略了一系列时钟,没画出来。 上面的那段代码描述的波形为: 当然也可以添加上升沿标识,只需要将代码中的p换成大写的P(Positive)就好了,如下: {signal: [ {name: 'clk', wave:'P...........|...'}, ]}描述的波形如下: 下面添加一个计数,从0开始计数,计数到4,然后计数器清零: {signal: [ {name: 'clk', wave:'P...........|...'}, {name: 'cnt', wave:'============|===',data:['0','1','2','3','4','0','1','2','3','4','0','1','2','3','4']}, ]}描述出的波形为: 至于怎么写的,wave中=代码那一个个数字框,后面的data是填充数据用的。见下图: 这段描述很清晰了。 下面添加一个分频时钟,五个时钟周期翻转一次: {signal: [ {name: 'clk', wave:'P...........|...'}, {name: 'cnt', wave:'============|===',data:['0','1','2','3','4','0','1','2','3','4','0','1','2','3','4']}, {name: 'clk_div10', wave:'0....1....0.|1..'}, ]}有了上面的基础,就逐渐上手了,这段代码描述的波形是: 这就是10分频,clk_div10的时钟周期是clk的10倍,频率是其1/10,这也是10分频的意思。 奇分频(5分频为例)画分频电路波形图的所用的这些简单的语言上面已经讲完了,下面直接画出5分频电路的波形图。 先简要的说明一下原理: 假如是一个占空比为50%的5分频电路,那么就需要在基准时钟clk的2.5个时钟周期,分频时钟clk_div5翻转一次,如何实现2.5个时钟周期翻转一次呢? 这就需要产生一个与clk完全相反的时钟clk1,此时钟与clk相位相差180°,然后对这两个时钟的上升沿计数,计数到4,计数器初始值为0,那么就代表2.5个clk时钟周期。 且看下图: 从图中可以看出,clk与clk1的上升沿都进行计数,计数到4,clk_div5翻转一次,这样就实现了5分频电路。 描述这个波形图的代码为: { signal: [ { name: "clk", wave: "P........", period: 2 }, { name: "clk1", wave: "n........", period:2 }, { name: "cnt", wave: "==================", data: "0 1 2 3 4 0 1 2 3 4 0 1 2 3 4 0 1 2" }, {}, { name: "clk_div5", wave: "0....1....0....1.." }, ]}这张图的精髓在于调节周期和相位,见下图: 不做过多解释,应该能看懂。在源代码的基础上该就是了。 如果占空比为3:2呢?波形图如何画? 同样很简单,就是clk的三个周期翻转一次,然后再过两个周期翻转一次 ,再过三个周期翻转一次,依次循环即可: 描述代码为: {signal: [ {name: 'clk', wave:'P...........|'}, {name: 'cnt', wave:'============|',data:['0','1','2','0','1','0','1','2','0','1','0','1']}, {name: 'clk_div5', wave:'0..1.0..1.0.|'}, ]} 案例二这个案例就是模10计数器了,见原博文:模6计数器以及模10计数器(Verilog HDL语言设计)(Modelsim仿真与ISE综合),这个波形就好画的多了,权当练手: 每个时钟上升沿到来时,计数一次,计数到9后计数器清零。 直接给图: 代码: {signal: [ {name: 'clk', wave:'p...........|'}, {name: 'cnt', wave:'============|',data:['复位0','1','2','3','4','5','6','7','8','9','0','1']}, ]} 结束语所谓用到学到,暂时先学习这些,当用到其他功能时,再继续研究呗,反正此刻已经满足了画基本的波形图的需求了。 最后贴出,教程:Hitchhiker's Guide to the WaveDrom Hitchhiker's Guide to the WaveDrom (Part 2) 最后再次贴出在线编辑界面: WaveDrom Editor

|

【本文地址】