| VsCode配置之verilog | 您所在的位置:网站首页 › vscode设置关键字变色 › VsCode配置之verilog |

VsCode配置之verilog

|

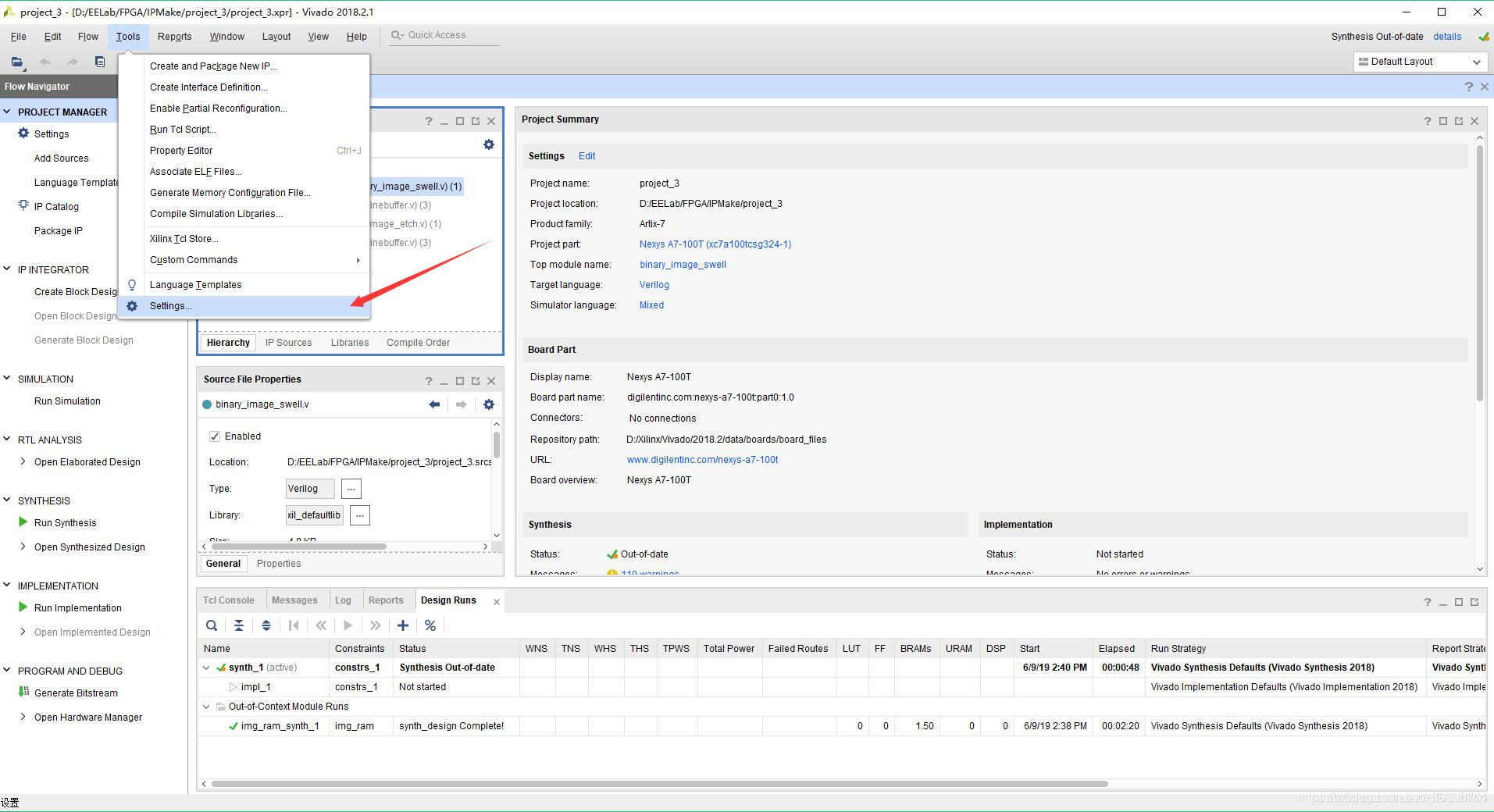

原文:https://blog.csdn.net/qq_39498701/article/details/84668833 步骤一、更换Vivado自带文本编辑器 第一步 打开Vivado 再Tool菜单中 打开Settings

这里需要键入的表达式是: C:/Program Files/Microsoft VS Code/Code.exe -g [file name]:[line number] 前面是VsCode应用程序的绝对路径。Linux下如果是在环境变量中,可以直接写Code 但是Windows下好像不可以。 这样双击工程下面的文件,Vivado会自动使用Code打开文件。 这样,我们就能用VsCode取代原本的编辑器了。 步骤二、用VsCode舒适的编写Verilog 第一步 安装Verilog扩展

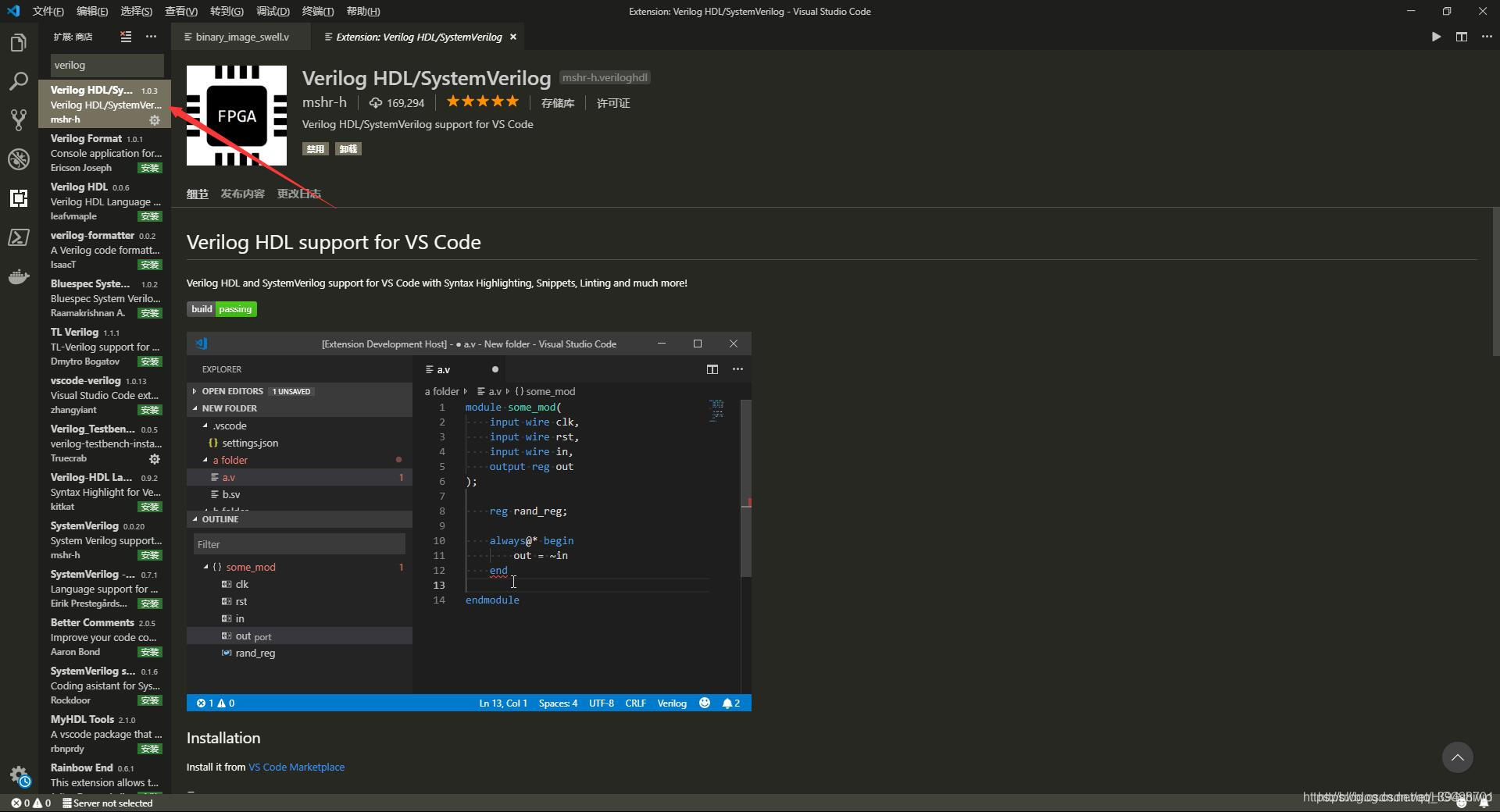

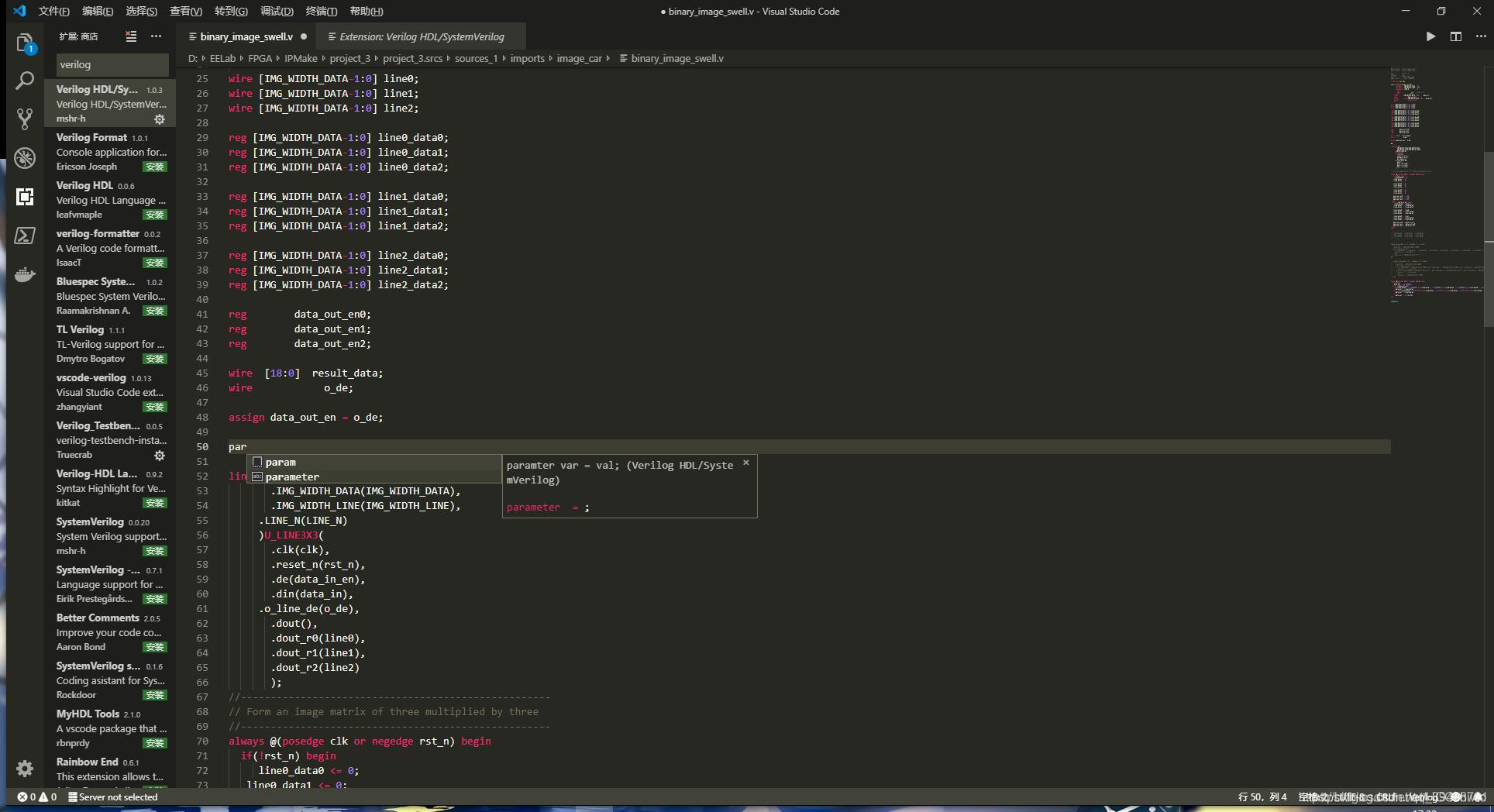

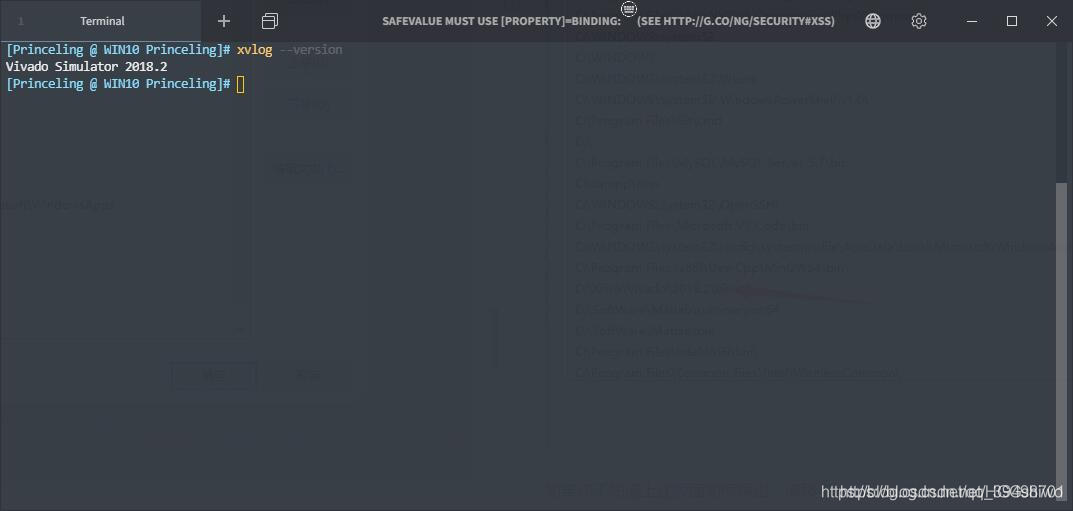

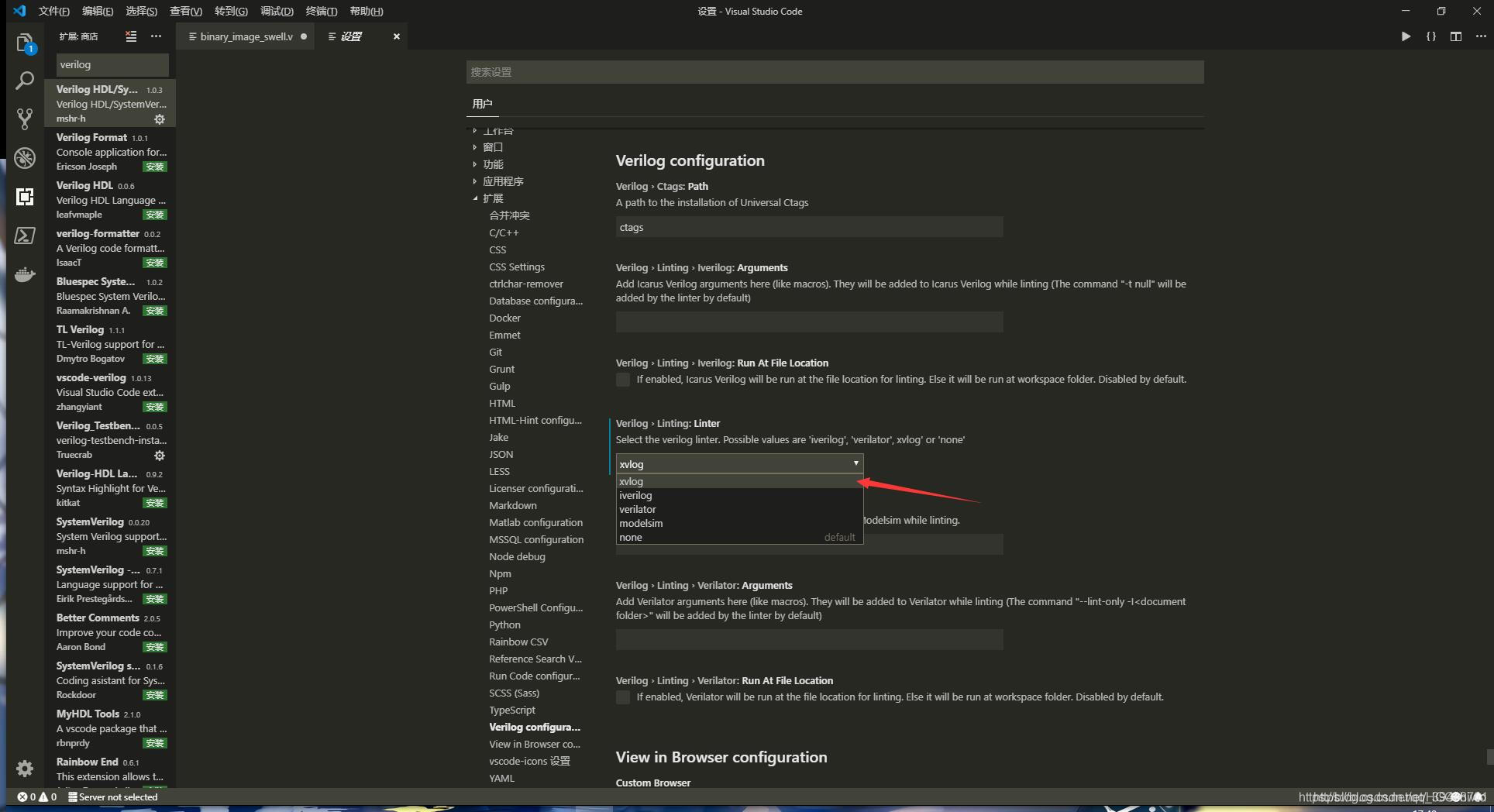

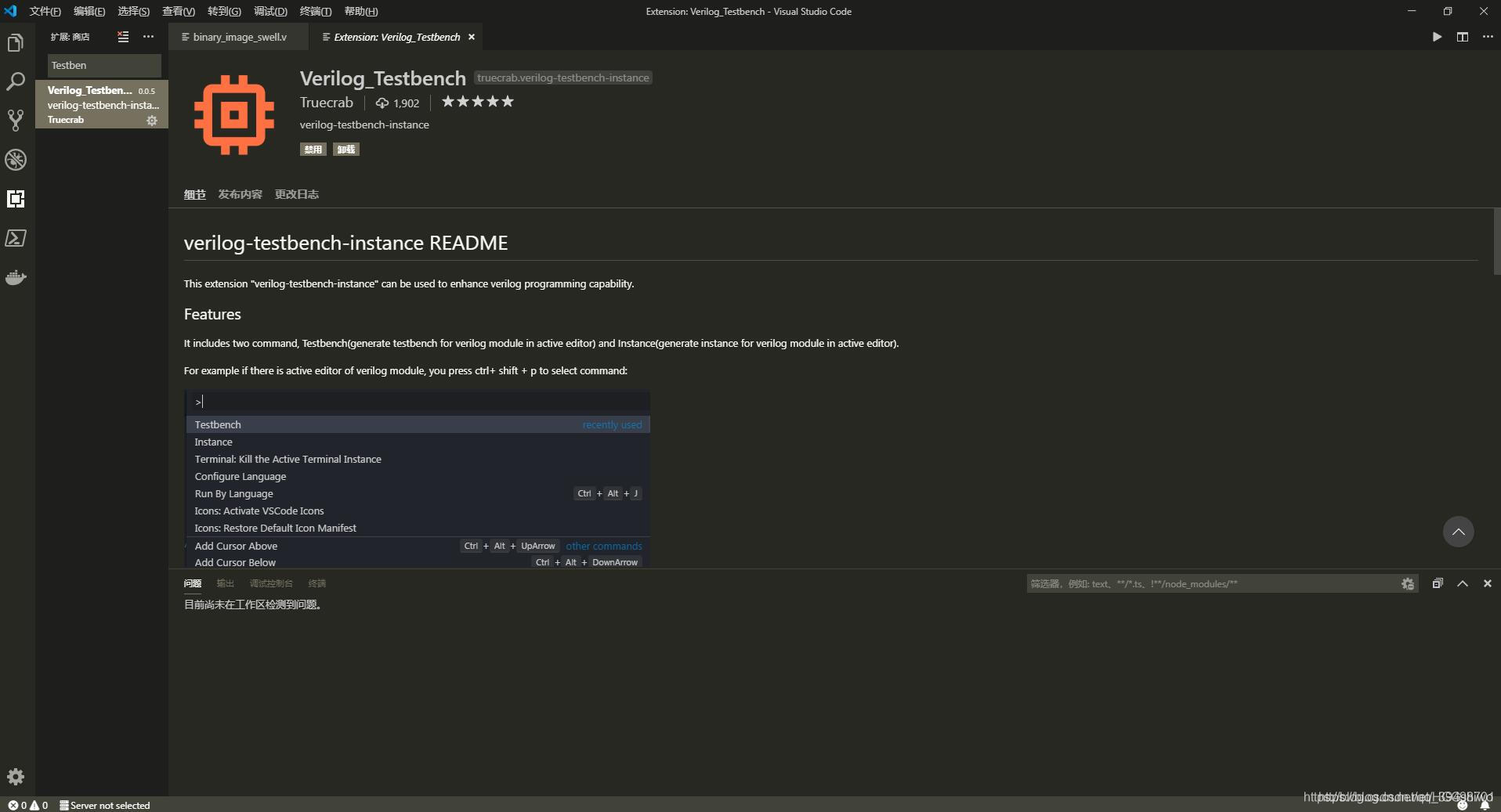

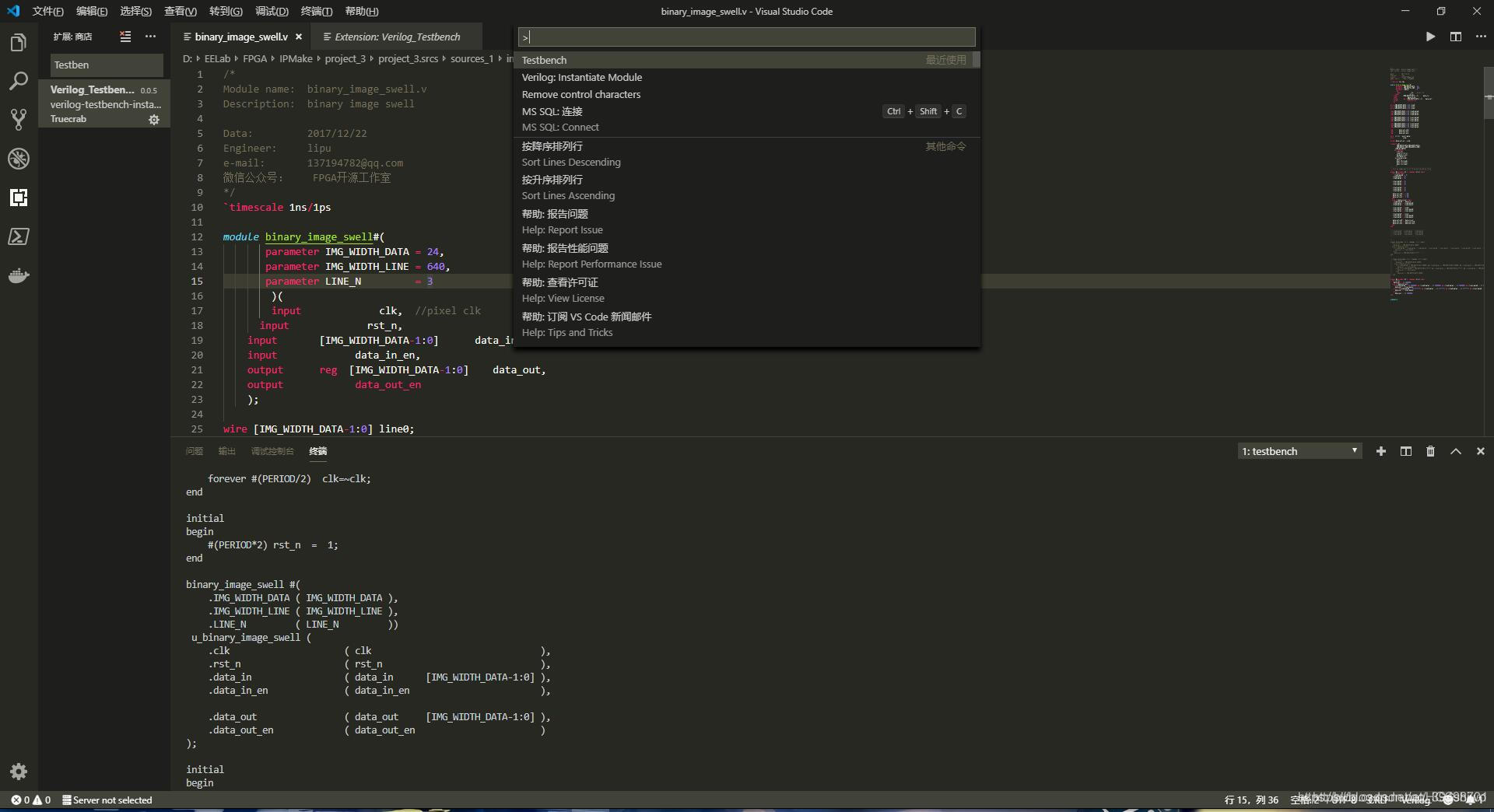

在VsCode扩展商店搜索verilog。 我们安装使用人数最多的扩展。可以看见其是支持Verilog和SystemVerilog的,如果你使用的是VHDL则下载另外的插件即可。 他能帮你实现的功能: 语法高亮,自动补齐,列出端口。 可以看到,我们的verilog文本,被渲染的很漂亮。并且能够实现自动补齐。 第二步 实现自动纠错vivado使用xvlog进行纠错。 vivado安装目录下的xvlog所在的目录放置在系统的环境变量,以便VsCode能够方便的调用他。 具体的目录就是Vivado的bin文件夹。 搜索环境变量->点击编辑环境变量->用户变量->Path 就会出现下图,不要在用户变量里添加,要在path里添加。 添加完成之后,在命令行输入xvlog –-version检测是否生效 如果没有打印出未找到该命令,那么你可能需要重启您的电脑。 接下来我们在设置里,找到刚才安装的verilog扩展,将verilog的Linter更换成xvlog。 需要注意的是,编译器需要您手动保存,才会开启xvlog解析,也就是说观看最新错误之前,需要保存一下。 步骤三、自动生成Testbench有时候在工程中要例化一个模块,这个模块有几十个输入几十个输出,如果没有一个好的脚本帮助你,不仅人为出错的可能比较大,例化的过程想必也是痛苦的。 还好有人已经在VsCode编写过自动生成Testbench的脚本了,感谢。 扩展商店搜索Verilog_TestBench,安装过后,任意编写一段verilog程序。按下ctrl+shift+p,选择testbench即可生成testbench对应的tb文本。 效果如上图所示。执行脚本之后,其出结果导向powershell的输出结果之中。帮我们自动生成了了时钟信号,复位信号,以及进行了模块的例化。如果你只需要例化模块,复制这一部分进你的代码中就可以了。到这里,VsCode已经能够给你的工程带来及其舒适的体验了。 VsCode使用小技能这部分用来总结一下VsCode使用过程中的一些小经验,可能会持续更新 按住鼠标中键,可以连续操作多行,这个在例化模块,以及一些无脑操作的时候很管用。 ctrl + f 搜索 替换 Code支持文件对比功能,在左边的资源栏中右击比较即可(抄代码很方便) ctrl+r可以搜索过去曾经使用code打开的文件,真的方便,不需要鼠标操作,够极客 答疑总结无法正确进行语法纠错的原因: 打开的Verilog文件目录有中文路径。 打开的Verilog文件目录有空格。 |

【本文地址】