| 【EDA技术】 实验一 利用半减器设计一位全减器 | 您所在的位置:网站首页 › vhdl电路图 › 【EDA技术】 实验一 利用半减器设计一位全减器 |

【EDA技术】 实验一 利用半减器设计一位全减器

|

一、实验目的

(1)熟悉EDA软件,并能熟练使用。 (2)分析设计任务,根据任务要求完成设计内容。 (3)利用软件对设计内容进行仿真调试,得到正确运行结果。 二、实验要求

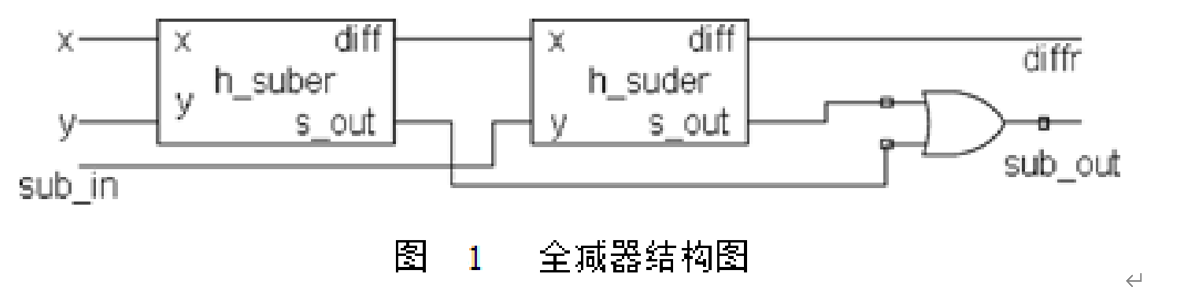

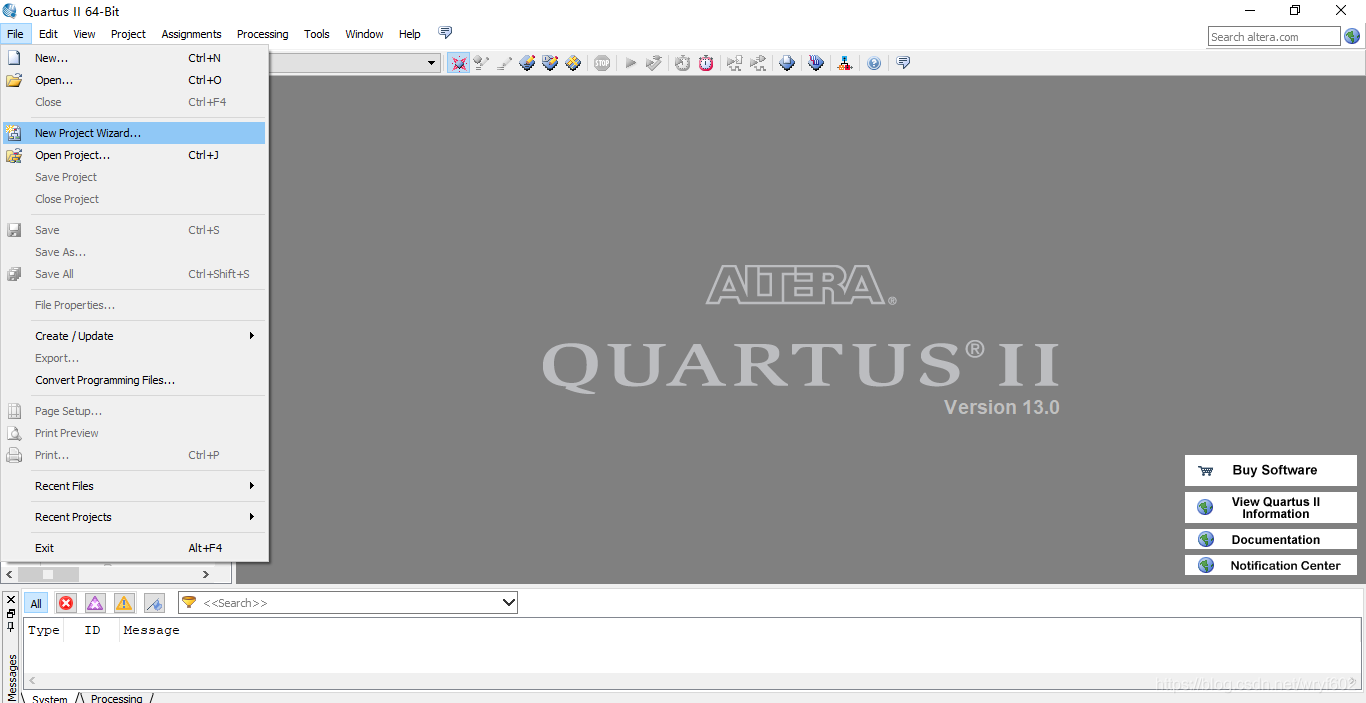

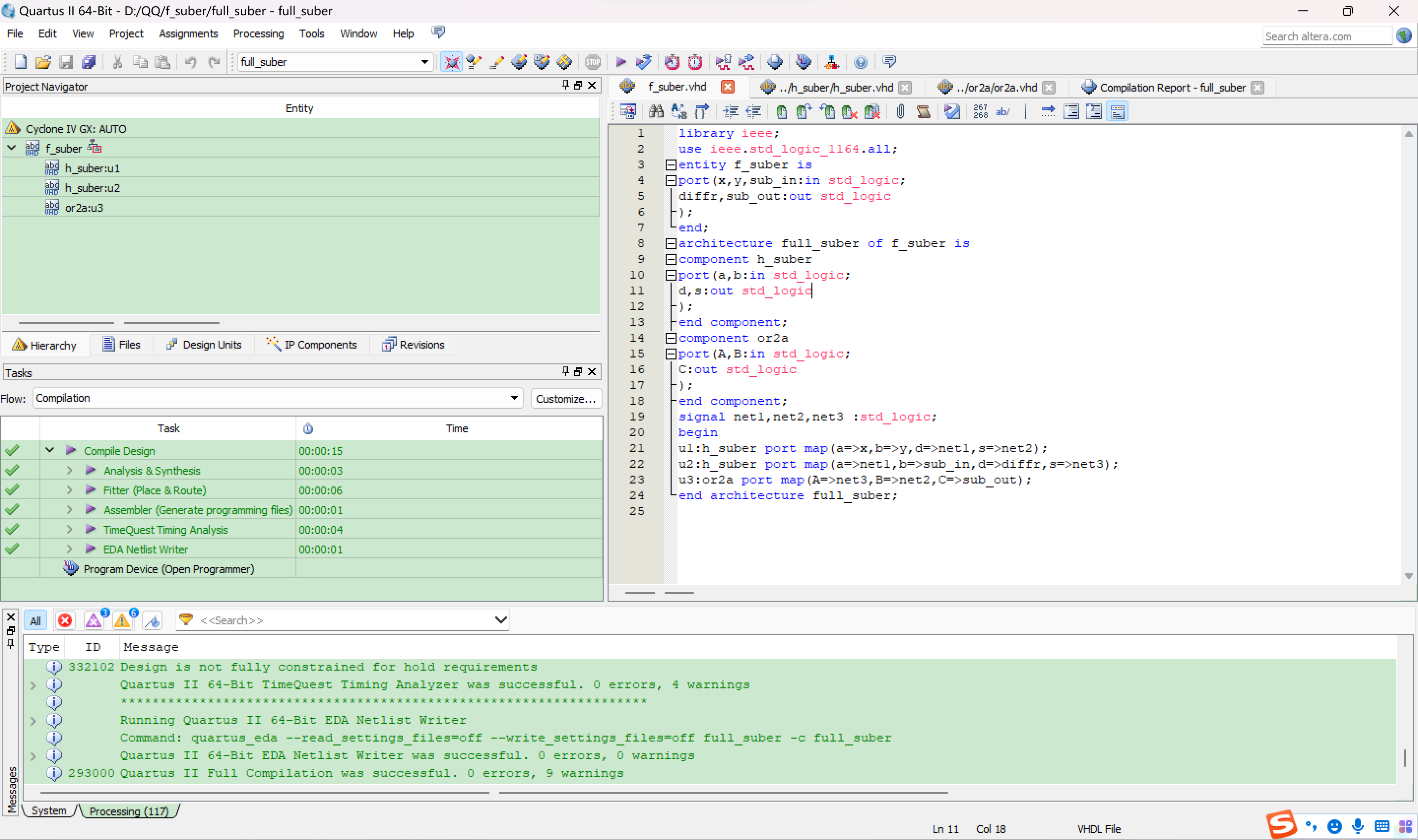

(1)首先设计半减器,然后用例化语句将它们连接起来,图1中h_suber是半减器,diff是输出差,s_out是借位输出,sub_in是借位输入。 (2)根据图1设计全减器。以全减器为基本硬件,构成串行借位的8位减法器,要求用例化语句来完成此项设计(减法运算是 x – y - sun_in = diffr)。 三、实验步骤(1) 建立工作库文件夹和编辑设计文件 File->New Project Wizard

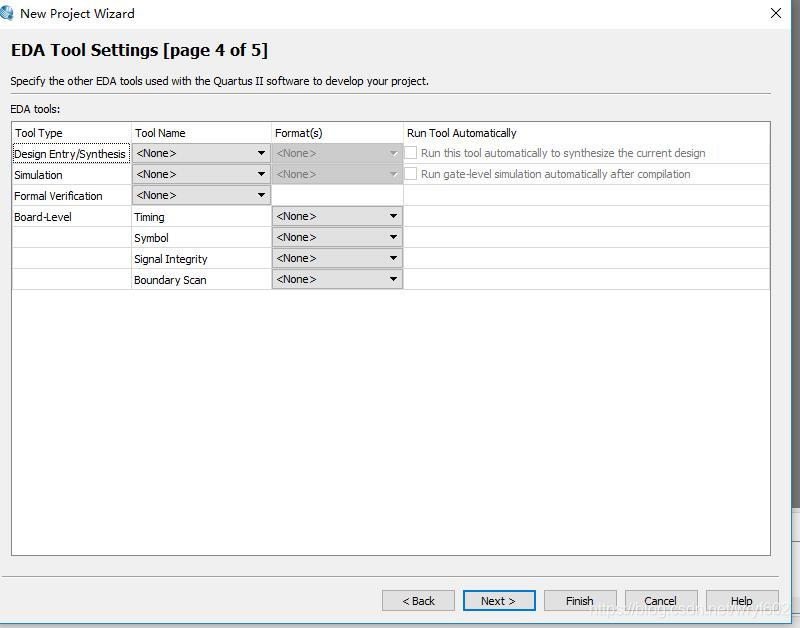

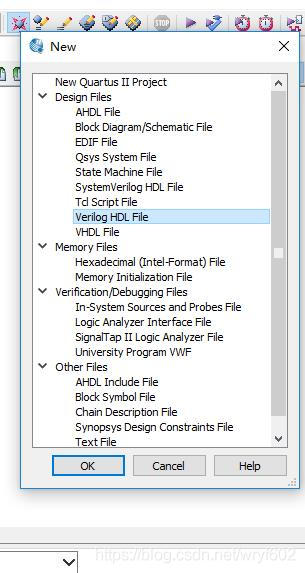

(2) 创建工程 File->New->Verilog HDL File

(3) 全程编译

(4) 时序仿真

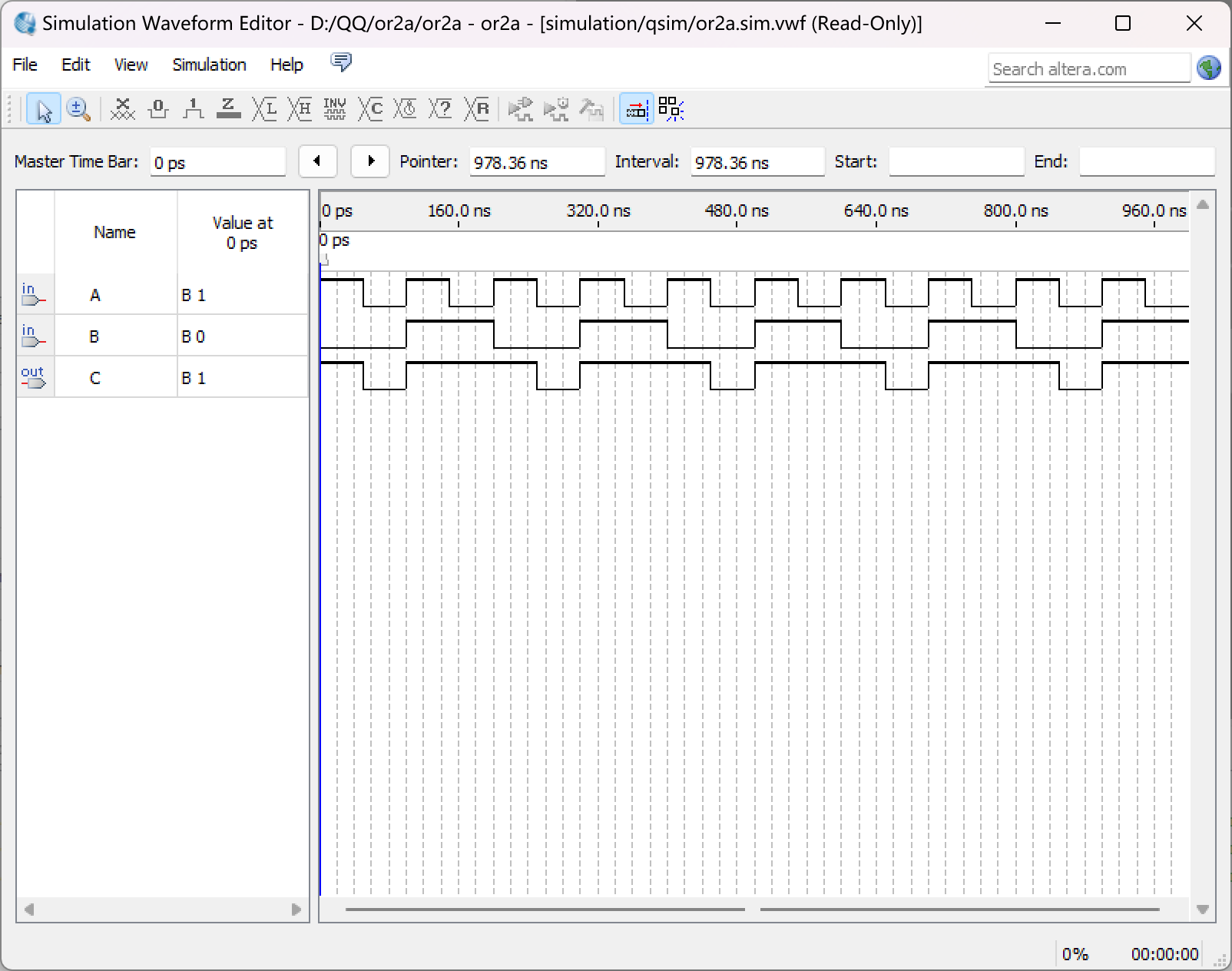

输入有1,输出就是1;只有当输出全为0时,输出才为零。证明是2输入或门。

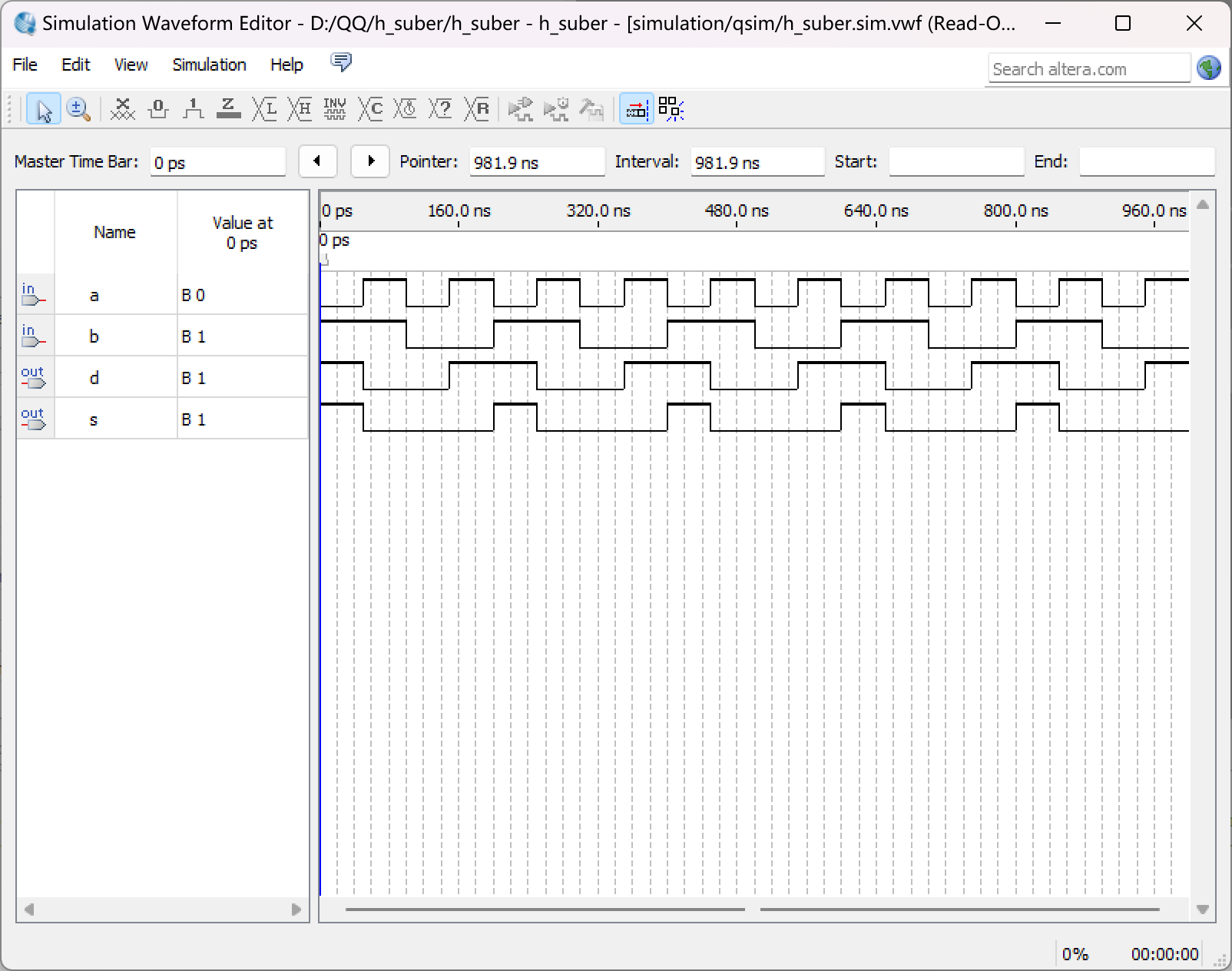

b是减数,a是被减数,d、s分别是本位输出和借位输出。 只有当a和b相同时,d才是低电平;即是 被减数 和减数 相同时 差是0。 只有当b比a大的时候,s才是高电平;即是 减数比被减数大的时候,本位向高位借1。

从上至下依次是减数(x)、低位借位(sub_in)、被减数(y)、高位借位(sub_out)、差(differ). 以下假设均建立在被减数≥减数情况,小于情况分析类似亦成立。 当x和 y 相同 ① sub_in 是0时,differ是低电平0;②sub_in 不是0时,differ是高电平1; 当x和 y 不同 ① sub_in 是0时,differ是高电平1;② sub_in 不是0时,differ是低电平0; 当x和 y 相同 1.sub_in是0时① sub_out 是0时,differ是低电平0;② sub_out 不是0时,differ是高电平1; 2.sub_in是1时 ,sub_out 不是0时(是0不存在),differ是高电平1; 当x和 y 不同 1.sub_in是0时① sub_out 是0时,differ是高电平1;② sub_out 不是0时,differ是低电平0; 2.sub_in是1时, sub_out 是0(1情况不考虑)时,differ是低电平0; 符合全减器规律 下面给出方便理解的图示和真值表

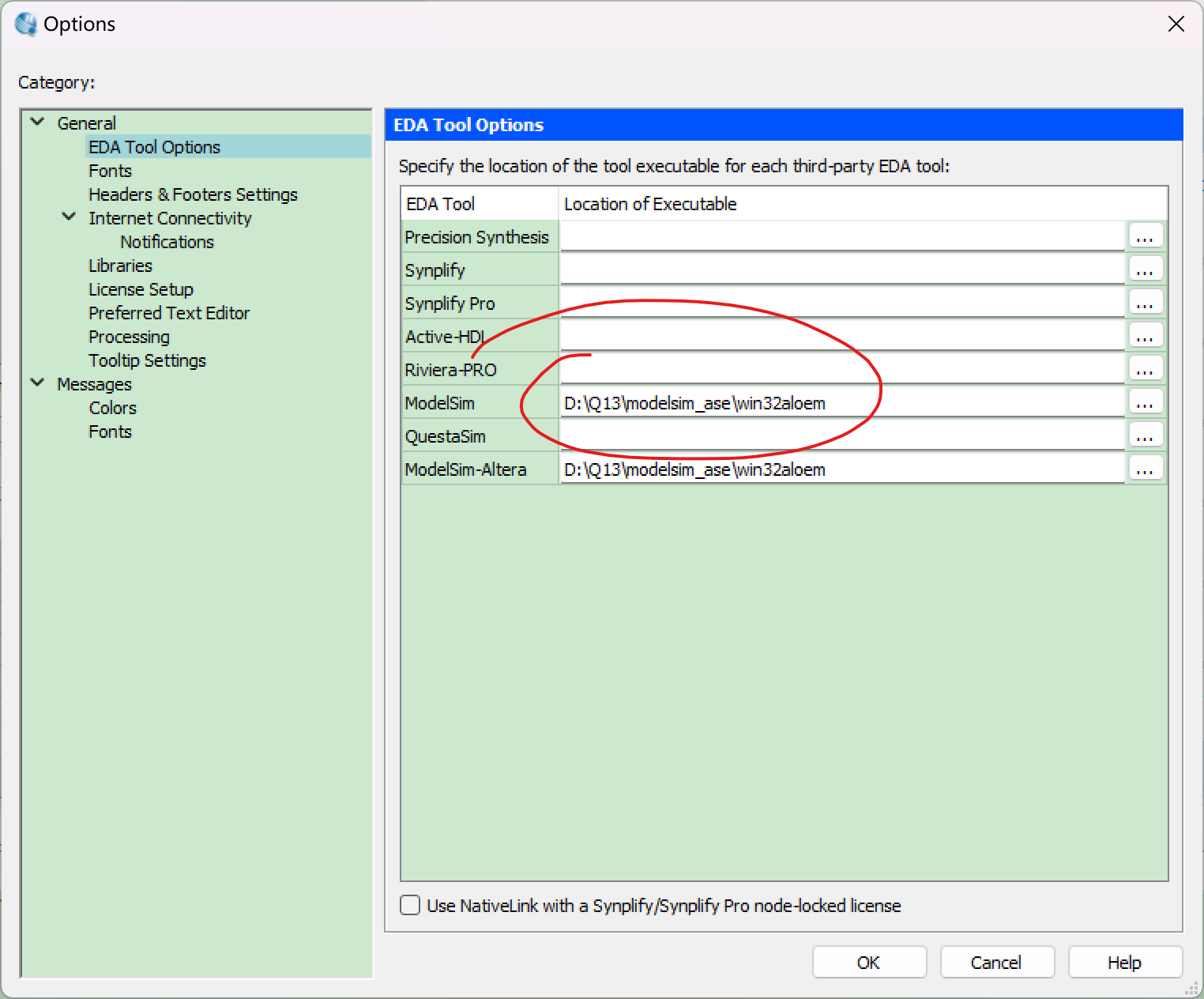

解决办法:按照图示依次点击Tools->Options->General->EDA Tool Options->ModelSim 把路径设置为ModelSim软件所在处。

解决办法:检查问题1是否已经解决,解决后关闭软件,以管理员身份启动软件,再次仿真。 |

【本文地址】