| Verilog HDL系统任务说明语句task | 您所在的位置:网站首页 › verilog调用task任务 › Verilog HDL系统任务说明语句task |

Verilog HDL系统任务说明语句task

|

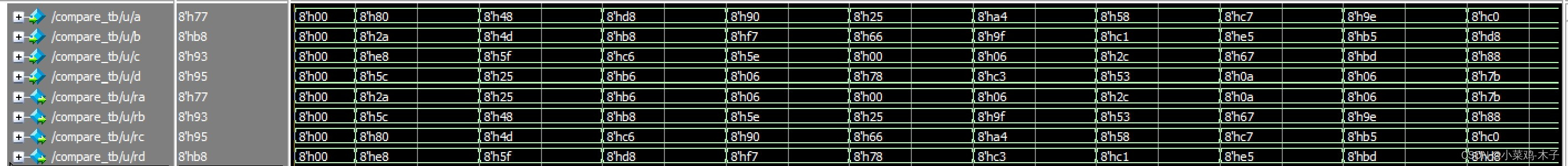

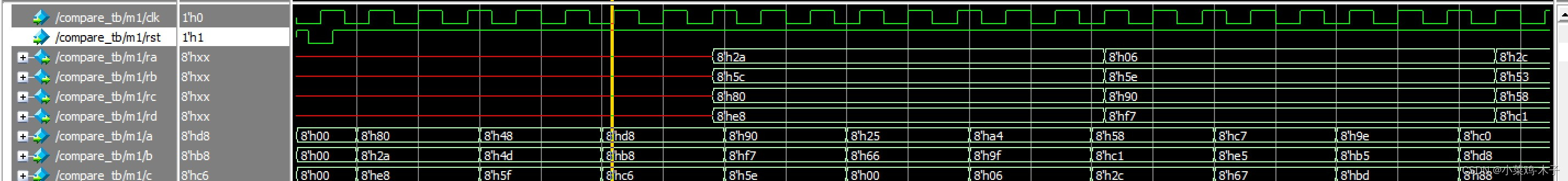

task说明语句 如果传给任务的变量和任务完成后接受任务的变量已定义,就可以用一条语句启动任务,任务完成以后控制传回启动的过程。 1.1任务的定义 定义任务的语法如下: task ... endtask1.2任务的调用及变量的传递 任务调用: (端口名1,端口名1,...端口名n);1.3例子 用两种不同的方法设计一个功能相同的模块,完成一个四个8位2进制输入数据冒泡排序。一种方法是组合逻辑实现,另一种是时钟触发任务实现,每个时钟周期完成一次数据交换。 第一种方法: 设计代码: module compare( a, b, c, d, ra, rb, rc, rd ); input [7:0] a,b,c,d; output reg [7:0] ra,rb,rc,rd; reg [7:0]va,vb,vc,vd; always @(*) begin {va,vb,vc,vd}={a,b,c,d}; change(va,vb); change(vb,vc); change(vc,vd); change(va,vb); change(vb,vc); change(va,vb); {ra,rb,rc,rd}={va,vb,vc,vd}; end task change; inout [7:0]x,y; reg [7:0] temp; if(x>y) begin temp=y; y=x; x=temp; end endtask endmoduletestbench: `timescale 1ns/1ns module compare_tb; reg clk,clk1; reg [7:0] a,b,c,d; wire[7:0]ra,rb,rc,rd; initial begin clk=0; clk1=0; a=0; b=0; c=0; d=0; end always #20 clk=~clk; always #50 clk1=~clk1; always@(posedge clk1) begin a={$random}%255; b={$random}%255; c={$random}%255; d={$random}%255; end compare u( a, b, c, d, ra, rb, rc, rd ); endmodule仿真波形: 第二种方法: 设计代码: module compare_2( clk, rst, a, b, c, d, ra, rb, rc, rd ); output reg[7:0] ra,rb,rc,rd; input[7:0] a,b,c,d; input clk,rst; reg[7:0] va=0; reg[7:0]vb=0; reg[7:0]vc=0; reg[7:0]vd=0; reg[2:0]state; parameter IDLE=0 ,s0=1,s1=2,s2=3,s3=4,s4=5,s5=6,s6=7; always @ (posedge clk) begin if(!rst) begin va$random}%255; d={$random}%255; end compare_2 m1( .clk(clk), .rst(rst), .a(a), .b(b), .c(c), .d(d), .ra(ra), .rb(rb), .rc(rc), .rd(rd) ); endmodule仿真波形: |

【本文地址】

公司简介

联系我们

| 今日新闻 |

| 推荐新闻 |

| 专题文章 |