| 基于verilog的BCD计数器设计与验证 | 您所在的位置:网站首页 › verilog设计模60bcd码计数器 › 基于verilog的BCD计数器设计与验证 |

基于verilog的BCD计数器设计与验证

|

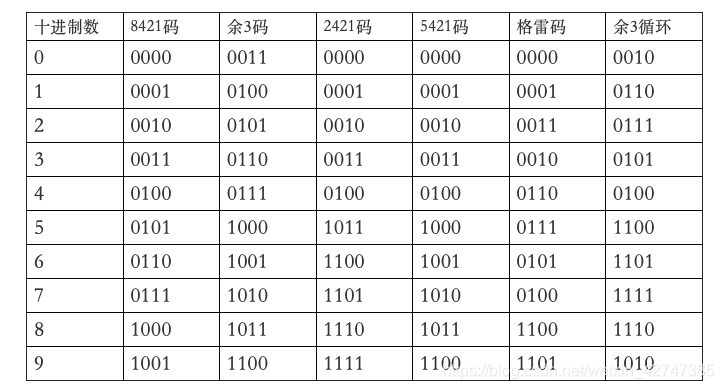

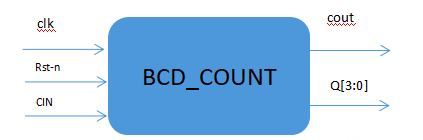

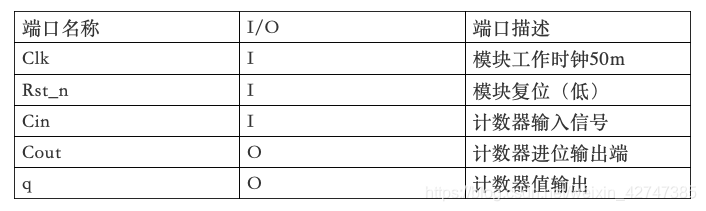

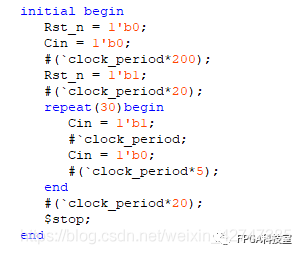

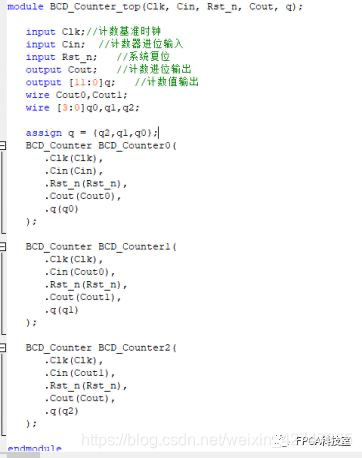

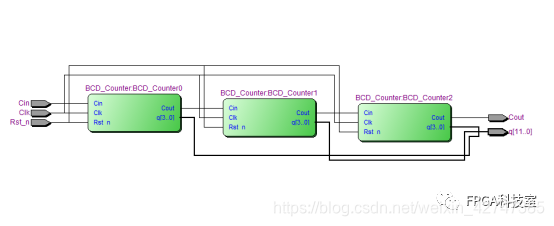

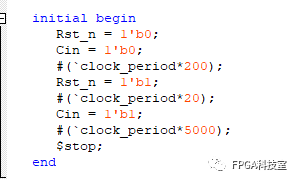

请关注微信公众号“FPGA科技室”获取更多内容 先来了解一下啥是BCD码,BCD码又被叫做二进制十进数,二-十进制代码是一种十进制数字编码,用4位二进制数来表示十进制数中的0~9.BCD编码又可以分成有权码和无权码两种,其中,有权码有:8421码,5421码还有2421码等;无权码有:余3码,格雷码,余3循环码等。 BCD码原理BCD码中最常用的是8421码,其各个bit权值分别是8d,4d,2d,1d;同理,5421码各位的权值依次为5d,4d,2d,1d。5421码特点是最高位连续5个0后连续5个1,故其当计数器时采用这种编码,最高位可产生对称方波输出;余3码是在8421码上加上0011b后得到的;格雷码的特点就是任意两个相邻的代码只有一位二进制数不同;余3循环码具有格雷码的特点并且编码的首尾可以连接来进行循环,这样可以用反馈移位寄存器来实现。 BCD码运算规则:BCD码是十进制数,而运算器对数据做加减运算时,都按照二进制运算规则进行处理的。那么,当将BCD码传送给运算器进行运算时,其结果需要需要修正。 修正的规则:当两个BCD码相加,如果和等于或小于1001b时,不需要修改;如果相加之和在1010b到1111b之间,就要加6d(0110b)来进行修正;如果相加时,本位产生了进位,也需要加6来修正,举个例子:计算5+8时,将5和8转换为8421BCD码后输入进加法器,即为0101+1000=1101结果大于9d,那么我们就要+0110b修正得到10011b,补充高位得到0001_0011b。 BCD计数器代码设计实现根据设计方案,得到本设计模块接口如下。 测试仿真编写测试激励文件,新建BCD_Counter_tb.v 这里生成了重复30次的占空比为1:5 周期为120ns的cin。 现在以上面的BCD计数器为基础设计级联的多位BCD计数器。将计数器位数设置为12,即为3个BCD计数器级联实现。 编写BCD_counter_top.v

|

【本文地址】

由上表知,十进制895转换为BCD码就是1000_1001_0101, 同理,BCD码1001_0110_0100转换为二进制数为964.

由上表知,十进制895转换为BCD码就是1000_1001_0101, 同理,BCD码1001_0110_0100转换为二进制数为964.

新建BCD_Counter工程,并书写BCD_Counter.v文件

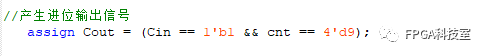

新建BCD_Counter工程,并书写BCD_Counter.v文件  上图看出,计数器计数值为9. 产生进位信号:

上图看出,计数器计数值为9. 产生进位信号:  BCD计数器输出: assign q = cnt;

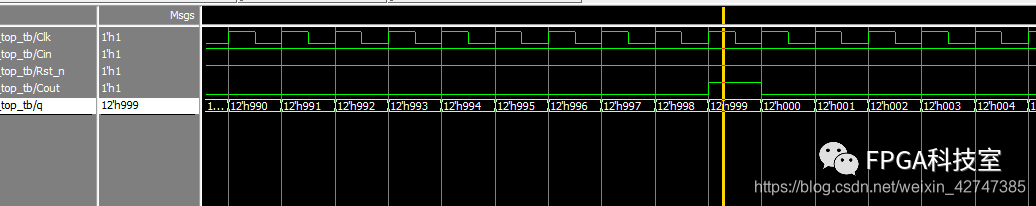

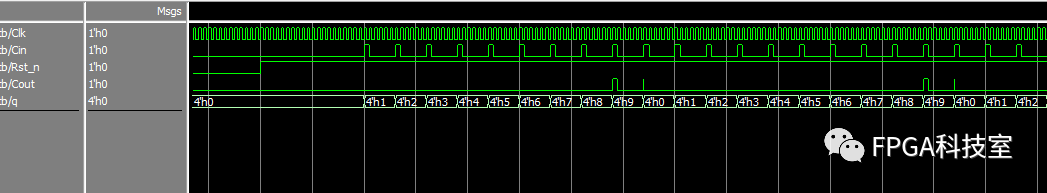

BCD计数器输出: assign q = cnt; 设置好仿真脚本后进行功能仿真,可以得到波形文件,可以看出在复位信号置高后,每当进位输入信号cin为高时计数值输出q完成一次自加,直到计数值为9后清零重新计数,然后产生进位。

设置好仿真脚本后进行功能仿真,可以得到波形文件,可以看出在复位信号置高后,每当进位输入信号cin为高时计数值输出q完成一次自加,直到计数值为9后清零重新计数,然后产生进位。

为了测试仿真编写测试文件,新建BCD_counter_top_tb.v文件。 复位后将cin一直置高,并延迟一定的时间,因为是3级计数器,计数器计数满后值为十六进制999.

为了测试仿真编写测试文件,新建BCD_counter_top_tb.v文件。 复位后将cin一直置高,并延迟一定的时间,因为是3级计数器,计数器计数满后值为十六进制999.  开启波形窗口 ,可以看到计数值q为1001_1001_1001产生进位信号

开启波形窗口 ,可以看到计数值q为1001_1001_1001产生进位信号