| 数字电路 第四章 | 您所在的位置:网站首页 › rs触发器原理图解图 › 数字电路 第四章 |

数字电路 第四章

|

一、边沿D触发器

1、电路组成及逻辑符号

下图所示是用两个同步D触发器级联起来构成的边沿D触发器。

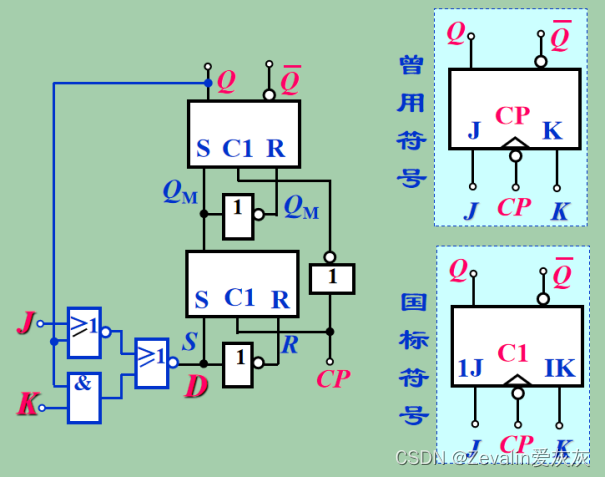

(1)下图所示是带有异步输入端的边沿D触发器的逻辑电路图和逻辑符号(右上是曾用符号,右下是国标符号)。

(2)同步输入端与异步输入端:

(3)异步输入端的工作原理:

(4)异步输入端是预置触发器初始状态,或者在工作过程中强行置为和复位触发器用的。 (5)在上图所示的逻辑符号中, (6) (1)逻辑符号与引出端功能图:

(2)考虑

(1)逻辑符号与引出端功能图:

(2)考虑

(1)CP边沿触发(判断上升沿触发还是下降沿触发,可以看逻辑符号中的CP连接的端是否有小圆圈,有小圆圈的基本就是下降沿触发,没有的则是上升沿触发;这种判断方法并不局限于这里)。在CP脉冲上升沿(或下降沿)时刻,触发器按照特性方程 (2)抗干扰能力极强。因为是边沿触发,只要在触发沿附近一个极短暂的时间内,加在D端的输入信号保持稳定,触发器就能够可靠地接收,在其它时间里输入信号对触发器不会起作用。 (3)只具有置1、置0功能,还是有一定的局限性。 三、边沿JK触发器 1、电路组成及逻辑符号 在边沿D触发器的基础上增加三个门

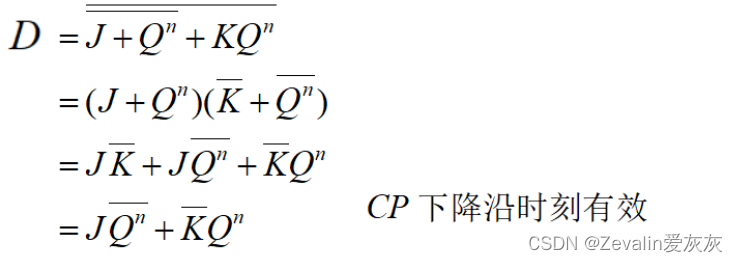

(1)

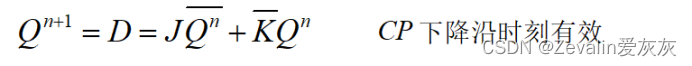

(2)特性方程:

(1)逻辑符号与引出端功能图:

(2)特性表(CP上升沿触发):

(1)逻辑符号与引出端功能图:

(2)特性表(CP下降沿触发):

(1)在CP上升沿或下降沿瞬间,加在J端和K端的信号才会被接收,也称为边沿触发。 (2)抗干扰能力极强,工作速度很高。 ①因为只要在CP触发沿瞬间J、K的值是稳定的,触发器就能够可靠地按照 ②由于是边沿控制,需要的输入信号建立时间和保持时间都极短,所以工作速度可以很高。 (3)在CP边沿控制下,根据J、K取值的不同,边沿JK触发器具有保持、置0、置1、翻转四种功能,对于触发器来说,它是一种全功能型的电路。

|

【本文地址】