|

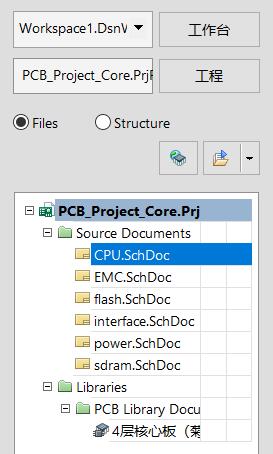

工程中需要先加入所有原理图与封装库  对于引脚较多的CPU,原理图往往使用引脚分部的绘制方法。在本次设计中CPU分成了4个part。 对于引脚较多的CPU,原理图往往使用引脚分部的绘制方法。在本次设计中CPU分成了4个part。  图为LPC3250的part.c。除了CPU本身引出的引脚外,左上角为两组IIC总线配备了10K欧姆的上拉电阻。 图为LPC3250的part.c。除了CPU本身引出的引脚外,左上角为两组IIC总线配备了10K欧姆的上拉电阻。  上图为LPC3250的part.a。这一部分与外接的flash,SDRAM进行连接,因此使用了一条数据总线与地址总线。 上图为LPC3250的part.a。这一部分与外接的flash,SDRAM进行连接,因此使用了一条数据总线与地址总线。  上图为LPC3250的part.d与flash芯片。LPC3250接有一个13MHZ的主频晶振和32.768KHZ的副晶振,副晶振为RTC提供时钟。flash芯片的设计较为简单,除了必要的数据总线与地址总线外,上拉控制IO处(3.3V)接了10K欧姆的上拉限流电阻。 上图为LPC3250的part.d与flash芯片。LPC3250接有一个13MHZ的主频晶振和32.768KHZ的副晶振,副晶振为RTC提供时钟。flash芯片的设计较为简单,除了必要的数据总线与地址总线外,上拉控制IO处(3.3V)接了10K欧姆的上拉限流电阻。  核心板与底板通过普通的排针进行连接,因此核心板上加了两排双联的排针座。左下角为LPC3250的复位电路。右下角为3.3V输入,由LDO降压稳压到1.2V的电源电路,电源芯片使用带反馈的SP6669K开关型LDO。值得一提的是,嵌入式CPU与SOC的供电电压一般为1.2V、1.8V、3.3V。由电路亦可知3.3V是由底板提供的。 核心板与底板通过普通的排针进行连接,因此核心板上加了两排双联的排针座。左下角为LPC3250的复位电路。右下角为3.3V输入,由LDO降压稳压到1.2V的电源电路,电源芯片使用带反馈的SP6669K开关型LDO。值得一提的是,嵌入式CPU与SOC的供电电压一般为1.2V、1.8V、3.3V。由电路亦可知3.3V是由底板提供的。  上图为LPC3250的part.b。图中右侧出现了大量的电源–地滤波电容,这样的滤波电容我们一般使用104规格的。在嵌入式数字电路中一般规定,芯片上每一个供电电源口都需要加至少一个滤波电容,以求最大程度减少电压尖峰和浪涌对元器件工作的影响。此外左边的CPU右侧在锁相环(PLL)引脚加入了一个高频振荡电路,为了减少高频信号受外界信号的干扰,该部分在布局时需要和锁相环引脚紧贴。 上图为LPC3250的part.b。图中右侧出现了大量的电源–地滤波电容,这样的滤波电容我们一般使用104规格的。在嵌入式数字电路中一般规定,芯片上每一个供电电源口都需要加至少一个滤波电容,以求最大程度减少电压尖峰和浪涌对元器件工作的影响。此外左边的CPU右侧在锁相环(PLL)引脚加入了一个高频振荡电路,为了减少高频信号受外界信号的干扰,该部分在布局时需要和锁相环引脚紧贴。  最后一部分是SDRAM,设计思路与上述相同。综上可见,核心板设计的元器件并不多(因为一般没有大量外设),因此原理图设计较为简单,难点在于布局与布线。 最后一部分是SDRAM,设计思路与上述相同。综上可见,核心板设计的元器件并不多(因为一般没有大量外设),因此原理图设计较为简单,难点在于布局与布线。  在嵌入式电路中往往使用wire+label的形式来进行各模块的链接。为了方便起见我们给wire和label设置快捷键。在AD中设置快捷键的方法为:按住Ctrl键,随后点击界面上想要设置快捷键的图标,会弹出以上窗口。由窗口可见,原先的操作叫:Sch:PlaceWire,也就是原理图布线,将鼠标移到红框中的栏目中,按下你想要为这个操作设置的快捷键(这里我用F2代替布线),随后点击右下角确定即可。需要注意的是,在SCH原理图绘制界面与PCBdoc绘制界面,快捷键不是共通的,因此在编辑PCB时F2这个键是没用的(如果系统没有预设的话),因此还需要再将PCB绘制使用的快捷键按上述方法设置一遍。 画好原理图之后紧接着是要对原理图进行错误类型设置以及编译。原理图的编译并不是真正的运行生成什么,而是对原理图进行纠错,需要注意原理图编译只会单纯的检查原理图,至于封装有没有问题,需要导入到PCBdoc中才能发现。 右键单击左侧工程目录里的工程文件,单击工程参数(O)会弹出原理图编译的错误类型设置窗口。 在嵌入式电路中往往使用wire+label的形式来进行各模块的链接。为了方便起见我们给wire和label设置快捷键。在AD中设置快捷键的方法为:按住Ctrl键,随后点击界面上想要设置快捷键的图标,会弹出以上窗口。由窗口可见,原先的操作叫:Sch:PlaceWire,也就是原理图布线,将鼠标移到红框中的栏目中,按下你想要为这个操作设置的快捷键(这里我用F2代替布线),随后点击右下角确定即可。需要注意的是,在SCH原理图绘制界面与PCBdoc绘制界面,快捷键不是共通的,因此在编辑PCB时F2这个键是没用的(如果系统没有预设的话),因此还需要再将PCB绘制使用的快捷键按上述方法设置一遍。 画好原理图之后紧接着是要对原理图进行错误类型设置以及编译。原理图的编译并不是真正的运行生成什么,而是对原理图进行纠错,需要注意原理图编译只会单纯的检查原理图,至于封装有没有问题,需要导入到PCBdoc中才能发现。 右键单击左侧工程目录里的工程文件,单击工程参数(O)会弹出原理图编译的错误类型设置窗口。  首先移到violations associateed with components(元器件冲突)这一栏,将duplicate part designers(出现相同编号的器件)与un-designed parts requiring annotation(未进行编号的元器件)设定为致命错误(fatal error)。在实际编译后,往往只需要考虑出现红色波浪线的地方即可,除了致命错误外其余的错误与警告可以无视。 之所以这两项设定为致命错误,是因为元器件编号出现问题,如果不使用交叉布局方式在PCBdoc布局的话,很容易混淆具体的元器件。此外,出现这种错误实在不规范。 首先移到violations associateed with components(元器件冲突)这一栏,将duplicate part designers(出现相同编号的器件)与un-designed parts requiring annotation(未进行编号的元器件)设定为致命错误(fatal error)。在实际编译后,往往只需要考虑出现红色波浪线的地方即可,除了致命错误外其余的错误与警告可以无视。 之所以这两项设定为致命错误,是因为元器件编号出现问题,如果不使用交叉布局方式在PCBdoc布局的话,很容易混淆具体的元器件。此外,出现这种错误实在不规范。  随后 移到violations with assoicated with nets栏目。将floating net labels(悬空的网络标号)、floating power objects(悬空的电源类标志)、nets with only one pin(无链接的引脚)勾选为致命错误,一般选取以上作为编译时的错误即可。 之所以选择以上三项作为致命错误。首先对于floating power objects(悬空的电源类标志),常见于拥有多种电源、多种地、电路做数模分割的场合。比如一个电路中模拟电路与数字电路都需要3.3V电源,于是设置一个A3V3和D3V3,但是如果画着画着迷糊了,自己又设了个3V3,那就出错了。该选项可以有效解决此种问题。 对于floating net labels(悬空的网络标号),该错误往往发生在该情景:使用label对pin进行链接时,把label右下侧表链接的小白点放错地方了,没有放在导线上或者放在了器件原理图的黑线上,这样的话导入到PCBdoc时该网络是不会导入的,是致命的错误。 Nets with only one pin(无链接的引脚)有些工程师并不把它当做致命错误,因为一个电路图中往往不会所有的pin都有的连。但是为了检查电路和规范性,个人建议开启其作为致命错误。在检查到的pin上放置ERC标志。 设置完后,右键单击工程目录的工程文件,左键单击compile PCB Project。 随后 移到violations with assoicated with nets栏目。将floating net labels(悬空的网络标号)、floating power objects(悬空的电源类标志)、nets with only one pin(无链接的引脚)勾选为致命错误,一般选取以上作为编译时的错误即可。 之所以选择以上三项作为致命错误。首先对于floating power objects(悬空的电源类标志),常见于拥有多种电源、多种地、电路做数模分割的场合。比如一个电路中模拟电路与数字电路都需要3.3V电源,于是设置一个A3V3和D3V3,但是如果画着画着迷糊了,自己又设了个3V3,那就出错了。该选项可以有效解决此种问题。 对于floating net labels(悬空的网络标号),该错误往往发生在该情景:使用label对pin进行链接时,把label右下侧表链接的小白点放错地方了,没有放在导线上或者放在了器件原理图的黑线上,这样的话导入到PCBdoc时该网络是不会导入的,是致命的错误。 Nets with only one pin(无链接的引脚)有些工程师并不把它当做致命错误,因为一个电路图中往往不会所有的pin都有的连。但是为了检查电路和规范性,个人建议开启其作为致命错误。在检查到的pin上放置ERC标志。 设置完后,右键单击工程目录的工程文件,左键单击compile PCB Project。  编译后会弹出一个messages小窗,里面会显示编译后出现的致命错误、错误、警告。我们无视错误与警告,只观察我们自定义的致命错误。如上图所示,出现了两个has only one pin的致命错误,也就是说有两个pin和外界没有链接,也没放ERC标志。 我们先确定一下,是这两个pin真的不需要与外界链接还是自己忘了链接。左键单击第一个致命错误,会自动跳转到出现错误的地方。随后我们去原理图中LPC3250的原理图处检查,有无使用该引脚,发现并没有使用,因此为其加一个ERC标志。 随后点击第二个致命错误,GPO_07没有外部链接。我们去双排排针处检查,看此pin是否引出使用。最后发现也没有,故也为其加上ERC标志。 这样,原理图的编译工作就结束了。 虽然将SCH导入PCBdoc时会显示出封装方面的错误,不过最好在导入之前使用功能较强的封装管理器(footprint manager)检查一下最好。 左键点击菜单栏工具(T)–>封装管理器(G): 编译后会弹出一个messages小窗,里面会显示编译后出现的致命错误、错误、警告。我们无视错误与警告,只观察我们自定义的致命错误。如上图所示,出现了两个has only one pin的致命错误,也就是说有两个pin和外界没有链接,也没放ERC标志。 我们先确定一下,是这两个pin真的不需要与外界链接还是自己忘了链接。左键单击第一个致命错误,会自动跳转到出现错误的地方。随后我们去原理图中LPC3250的原理图处检查,有无使用该引脚,发现并没有使用,因此为其加一个ERC标志。 随后点击第二个致命错误,GPO_07没有外部链接。我们去双排排针处检查,看此pin是否引出使用。最后发现也没有,故也为其加上ERC标志。 这样,原理图的编译工作就结束了。 虽然将SCH导入PCBdoc时会显示出封装方面的错误,不过最好在导入之前使用功能较强的封装管理器(footprint manager)检查一下最好。 左键点击菜单栏工具(T)–>封装管理器(G):  封装管理器左侧是元器件列表,首先检查左侧第三列current footprint,如果有某些行在此列为空白,说明该器件从未确认过封装,必须手动添加。 即便是此列不为空白,出现错误也是很常见的。以上图的C2,一个104规格,0603封装的贴片陶瓷电容为例。首先我们看右上方的栏目(view and edit footprint)。该栏目中只有一行,说明我们只导入了一种为该电容适配的封装,叫0603C,路径暂时看不出来(实际上any一般说明封装库来自工程内),并且路径没有确认(not validated)。如果右下角出现了该封装的图片,说明此封装已经被使用了。 那一般还会犯什么错误呢?错误一:封装选对了,但是pin没有匹配上或者匹配对。我们在右上方的栏目中点击0603C这一栏,随后点击红框处的编辑。 封装管理器左侧是元器件列表,首先检查左侧第三列current footprint,如果有某些行在此列为空白,说明该器件从未确认过封装,必须手动添加。 即便是此列不为空白,出现错误也是很常见的。以上图的C2,一个104规格,0603封装的贴片陶瓷电容为例。首先我们看右上方的栏目(view and edit footprint)。该栏目中只有一行,说明我们只导入了一种为该电容适配的封装,叫0603C,路径暂时看不出来(实际上any一般说明封装库来自工程内),并且路径没有确认(not validated)。如果右下角出现了该封装的图片,说明此封装已经被使用了。 那一般还会犯什么错误呢?错误一:封装选对了,但是pin没有匹配上或者匹配对。我们在右上方的栏目中点击0603C这一栏,随后点击红框处的编辑。  之后会出现上图窗口。在封装模型中我们点击Pin Map(P),会出现原理图的pin和封装库的pin的一一对应关系,这个必须确定正确。 此外,如果导入了多个封装,依然有发生错误的可能: 之后会出现上图窗口。在封装模型中我们点击Pin Map(P),会出现原理图的pin和封装库的pin的一一对应关系,这个必须确定正确。 此外,如果导入了多个封装,依然有发生错误的可能:  如上图所示,我故意给这种0603封装的104陶瓷贴片电容又增加了两个封装0603与0603R。当然,0603,0603C,0603R三种封装的焊盘数据一定是一样的(不然怎么能都叫0603而不是0805),区别往往只是在丝印上,有的封装丝印是把元器件整个轮廓围了起来,有的封装只是象征性地画了几条线。使用哪种封装从电气角度上讲无所谓,没有真正的区别,看具体需求和个人喜好使用。关键在于,当你导入多个封装之后,单纯看上图(view and edit footprint)看不出到底用了哪个封装,甚至到底用没用都不知道。 因此导入多个封装也会导致错误,这个时候应当注意,具体使用哪种封装,一点要右键点击它,然后选择设定为当前(S),才能保证不会犯错。 最后我们新建一个PCBdoc。新建完之后记得首先在工程目录右键单击此PCBdoc,随后点击保存,这样就可以为其重命名,并保存。然后右键单击工程目录的工程文件,保存整个project,不然无法导入。 如上图所示,我故意给这种0603封装的104陶瓷贴片电容又增加了两个封装0603与0603R。当然,0603,0603C,0603R三种封装的焊盘数据一定是一样的(不然怎么能都叫0603而不是0805),区别往往只是在丝印上,有的封装丝印是把元器件整个轮廓围了起来,有的封装只是象征性地画了几条线。使用哪种封装从电气角度上讲无所谓,没有真正的区别,看具体需求和个人喜好使用。关键在于,当你导入多个封装之后,单纯看上图(view and edit footprint)看不出到底用了哪个封装,甚至到底用没用都不知道。 因此导入多个封装也会导致错误,这个时候应当注意,具体使用哪种封装,一点要右键点击它,然后选择设定为当前(S),才能保证不会犯错。 最后我们新建一个PCBdoc。新建完之后记得首先在工程目录右键单击此PCBdoc,随后点击保存,这样就可以为其重命名,并保存。然后右键单击工程目录的工程文件,保存整个project,不然无法导入。  由于检查仔细,导入并没有出现错误。本人大学期间经常帮人检查电路,发现一般在这一步容易出现两种错误: 1.footprint not found 这种错误是最直白的,某个元器件压根没有添加过封装。 2.unkown pin… 这种错误往往有多种形成原因:1.某个元器件添加过封装,但是出于某种原因,没能再次识别封装的路径,比如说原本在工程里的封装库,被不小心删掉了。2.某个元器件封装有问题,查看pin map会发现原理图与封装库的pin没对应好。3.有时候压根没添加封装也会出现这个错误。4.最极端的,原理图路径都没有保存,比如原本在工程里的原理图库,被删掉了。。。 由于检查仔细,导入并没有出现错误。本人大学期间经常帮人检查电路,发现一般在这一步容易出现两种错误: 1.footprint not found 这种错误是最直白的,某个元器件压根没有添加过封装。 2.unkown pin… 这种错误往往有多种形成原因:1.某个元器件添加过封装,但是出于某种原因,没能再次识别封装的路径,比如说原本在工程里的封装库,被不小心删掉了。2.某个元器件封装有问题,查看pin map会发现原理图与封装库的pin没对应好。3.有时候压根没添加封装也会出现这个错误。4.最极端的,原理图路径都没有保存,比如原本在工程里的原理图库,被删掉了。。。  导入成功后先将导入的room删掉,就会如上图所示。 导入成功后先将导入的room删掉,就会如上图所示。

|