| PCB 叠层(四层板) | 您所在的位置:网站首页 › pcb板4层板压伤怎么判定的 › PCB 叠层(四层板) |

PCB 叠层(四层板)

|

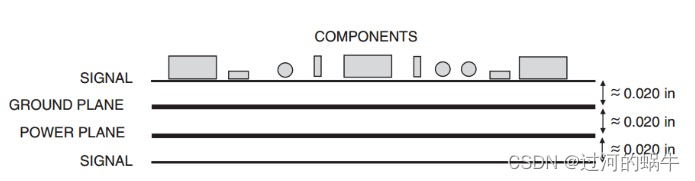

四层板的叠层 这里有两种方式 SIG-GND(PWR)-PWR (GND)-SIG; GND-SIG(PWR)-SIG(PWR)-GND;

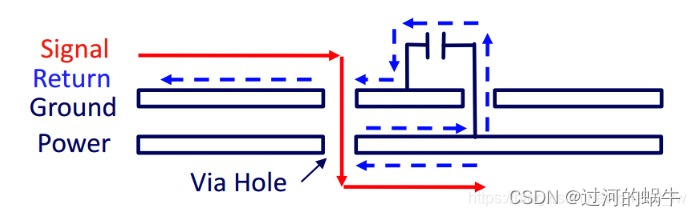

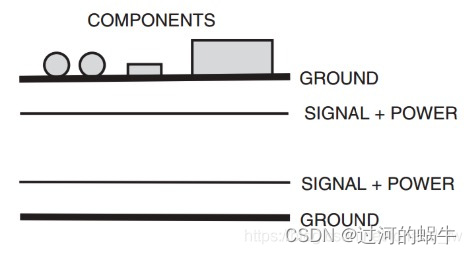

通常来讲,四层板辐射强度要比同样功能的两层板小20dB,关键在于要让信号尽量靠近参考层。因此,为进一步提升抗噪性能(EMC)和降低辐射(EMI),应该尽量减小信号层和参考平面之间绝缘层的厚度。如此看来,图1中的叠层结构性能不如图2的层叠结构,因为其信号层与参考层之间的绝缘层厚度更大,所以信号层和参考层的耦合度更低。但是这并不是一个严重的缺陷,因为两种叠层都能满足PCB的耦合度要求。这里要注意,两种叠层的整体厚度是一样的。 对于以上两种叠层设计,潜在的问题是对于传统的1.6mm(62mil)板厚。层间距将会变得很大,不仅不利于控制阻抗,层间耦合及屏蔽;特别是电源地层之间间距很大,降低了板电容,不利于滤除噪声。 对于第一种方案【SIG-GND(PWR)-PWR (GND)-SIG】,通常应用于板上芯片较多的情况。这种方案可得到较好的SI性能,对于EMI性能来说并不是很好,主要要通过走线及其他细节来控制。 主要注意:地层放在信号最密集的信号层的相连层,有利于吸收和抑制辐射;增大板面积,体现20H规则。 对于第二种方案【GND-SIG(PWR)-SIG(PWR)-GND】,通常应用于板上芯片密度足够低和芯片周围有足够面积(放置所要求的电源覆铜层)的场合。此种方案PCB的外层均为地层,中间两层均为信号 /电源层。 信号层上的电源用宽线走线,这可使电源电流的路径阻抗低,且信号微带路径的阻抗也低,也可通过外层地屏蔽内层信号辐射。从EMI控制的角度看, 这是现有的最佳4层PCB结构。 主要注意:中间两层信号、电源混合层间距要拉开,走线方向垂直,避免出现串扰;适当控制板面积,体现20H规则;如果要控 制走线阻抗,上述方案要非常小心地将走线布置在电源和接地铺铜岛的下边。 另外,电源或地层上的铺铜之间应尽可能地互连在一起,以确保DC和低频的连接性。 上述传统四层板叠层的缺点 首先,当走线从第一层换到第四层时,图1和2所示叠层结构就会出现问题,如图3。

如过层间电容不够大,那么层间阻抗就会比较大,这时回流的信号就会寻找阻抗较小的地方通过,从而增大回流面积。难免发生辐射污染,影响相邻的其他信号。这种情况当然应该避免,但是很不幸类似图1和2的叠层总厚度0.62inch的四层板,电源和地层间电容就很小,地阻抗较大。这种情况下,可能不会产生严重的信号完整性问题,但是一定会产生EMI问题。这就是为什么在用具有Power和Groud平面的叠层结构时,尽量避免信号换层,尤其是对于高速时钟信号。 当然,如果非要换层,最好在换层处加一颗去耦电容,并且尽量靠近换层过孔,从而减少回流路径的阻抗。但是,当信号频率非常高时,去耦电容因为自身的谐振也会失去效果。一般情况下,想让去耦电容发挥作用,信号频率不要高于200-300MHz。总结一下,当信号小于200-300MHz可以使用去耦电容帮助换层,但是更高频率的信号就不得不提高层间电容来解决问题了。

如果信号不换层就不会出现上述问题,但是层间电容过小还会带来另一个严重的问题:电源传输问题。通常许多IC都需要极高的瞬态电流,而且当信号的上升时间越来越小时(信号上升时间往往跟频率有关,时间越小频率越高),需要电源的频率也越高。通常,可以通过布置靠近IC的去耦电容来解决瞬间电源问题,但是如果需要电源频率过高,高于去耦电容自身的谐振频率,那么电容将变成一颗电感,而失去存储电能的作用。 现在越来越多的IC上升时间低于500ps,对去耦电容的性能提出挑战。而层间电容是一种非常好补充,它具有足够高的谐振频率,可以提供高效的瞬时电流。所以,相较于通用的去耦电容,层间电容能更好的为高速IC提供瞬时电源。 但是,减小绝缘层厚度增加层间电容的做法,有时也是不可行的,因为那会增加成本。 两种改进型叠层结构

图 6

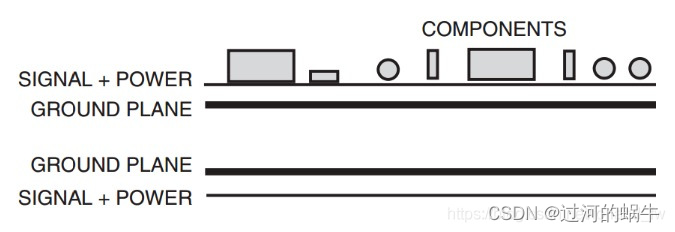

图 7 在图1和2所示的叠层结构中,要求信号层一定要有相邻的参考层,并且信号回流路径尽量小。出于这些考虑,图6所示叠层结构并非理想的叠层结构,因为表层摆放大量器件,破坏了完整的地平面。然而第三层却是一个非常好的布线层,因为它有完整的参考地平面。 图6和7都有两个地平面,这就提供了一个低阻抗的地平面并且有利于降低共模辐射。于此同时,图6的地平面包裹了信号层,形成一个屏蔽罩,可以很好的吸收大部分来自高频信号的辐射干扰。可以通过摆放过孔使两个地平面充分连接,这将进一步形成一个法拉第笼抑制辐射。当然图7叠层结构就没有这样的屏蔽效果了。以上两种叠层都没有一个完整的电源平面,所有不得不通过铺铜或者网格结构来传输电源。如果可以将器件和走线都摆放在第一层,那么强烈推荐图7的叠层结构,因为它有完整的地平面。如果不能,也可以考虑图6的叠层结构。 虽然没有完整的电源平面,但是电源铺铜一样可以非常靠近地平面,这样也可也得到一个较大的层间电容从而用于高频信号。有人认为,图6和7的电源铺铜的去耦作用强于传统四层结构的Power和Ground平面的去耦作用。再结合常用的去耦电容,也可以得到更好的电源性能。 最后,图6和7的叠层结构中,高速信号可以换层,因为信号的参考有完整的参考地平面(两边都有),地平面间摆放的过孔提过良好的连通性,从而减小回流路径的阻抗。 顶层和底层覆铜 以上两种改进的叠层结构中,最后一种中间两层均为GND平面,这种叠层中表层和顶层除了走线和电源外,是否应该进行覆铜,如果覆铜应该连接GND还是POWER。 在可能的情况,尽量覆铜并且连接到地。 首先,铺地操作能够起到屏蔽作用; 其次,铺地可以避免形成地回环,当然要在适当的地方打上过孔连接地平面;

答,3W原则,保持铺地与阻抗线3W距离,则可对阻抗影响较小,通常认为20mil间距足够。 |

【本文地址】

如图所示,Top和Bottom两个信号层各有一个参考平面(一个是地一个是电源)。所以,信号回流可以通过相邻的参考层,从而减小信号回路面积,减小信号路径的电感。低感量的信号路径可以降低噪声的干扰而且也减小了信号辐射(不管差模或者是共模)。

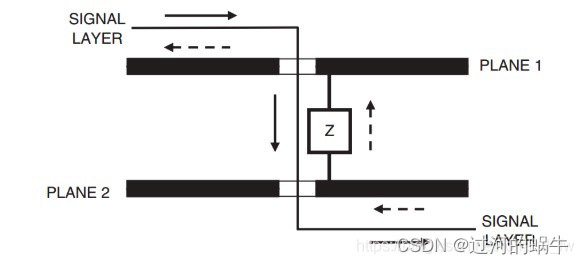

如图所示,Top和Bottom两个信号层各有一个参考平面(一个是地一个是电源)。所以,信号回流可以通过相邻的参考层,从而减小信号回路面积,减小信号路径的电感。低感量的信号路径可以降低噪声的干扰而且也减小了信号辐射(不管差模或者是共模)。 信号示意流向用红色线标出,回流用蓝色虚线标出。如果信号频率足够高,层间距足够小,信号回流就能轻松流过层间电容,从而实现从电源层到地层的转换。但是,因为电源和地之间并没有直接连通,所以对于回流的信号来说是存在一个破点,可以把它看做是一个阻抗,如图4所示。

信号示意流向用红色线标出,回流用蓝色虚线标出。如果信号频率足够高,层间距足够小,信号回流就能轻松流过层间电容,从而实现从电源层到地层的转换。但是,因为电源和地之间并没有直接连通,所以对于回流的信号来说是存在一个破点,可以把它看做是一个阻抗,如图4所示。

并且,铺地可以降低信号的回路阻抗,尤其是在双层板中。 所以,四层板如果允许尽量铺铜。那么如何解决顶层走线阻抗控制的问题?

并且,铺地可以降低信号的回路阻抗,尤其是在双层板中。 所以,四层板如果允许尽量铺铜。那么如何解决顶层走线阻抗控制的问题?