| 数字电路03 | 您所在的位置:网站首页 › mos等效电阻 › 数字电路03 |

数字电路03

|

1、概述

门电路 数字逻辑电路的基本单元,用以实现基本逻辑运算的的单元电路称为门电路或者逻辑元。

输出高低电压的基本原理:

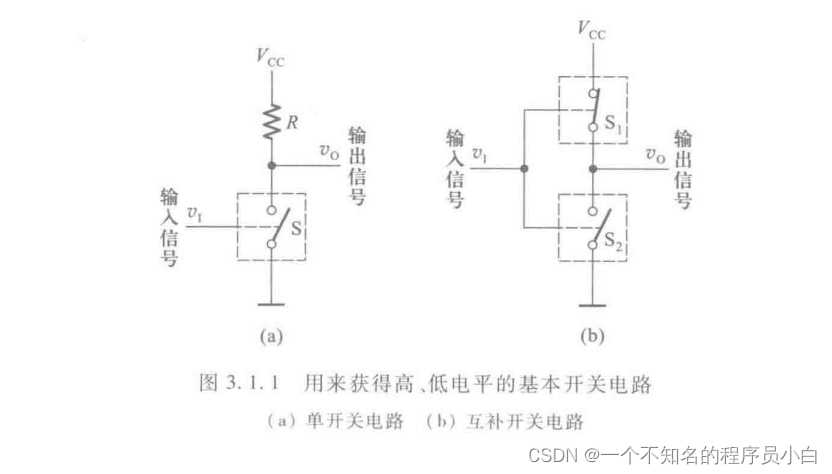

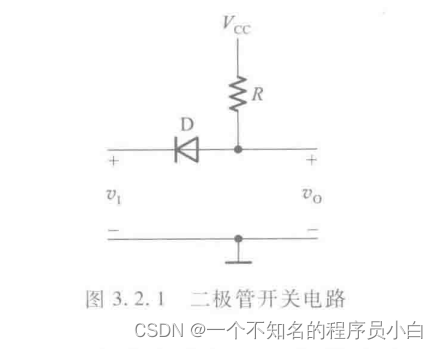

单开关电路 工作原理: S断开时,此时电路中不仅有电阻R,还有其他负载电路,故输出VDD-R(R一般特别小,故约等于输出电平VDD),输出高电平;S闭合时,由于直接接地,电路中无其他负载,所有电源电压均加在电阻R上,VO输出低电平缺点:当S闭合时所有电压都加在电阻R上,功耗等于 V 2 V^2 V2DD/R。 为了克服功耗大的缺点,就产生了互补开关电路。 互补开关电路 工作原理:根据输入信号,S1和S2必然有一个是断开,有一个是闭合的。 当S1断开S2闭合时,输出低电平;当S1闭合S2断开时,输出高电平优势:流过电路总的电流始终为0,功耗极小,这种开关电路在数字集成电路中广泛使用 2、半导体二极管门电路 开关特性假定二极管为理想器件,即正向导通电阻为0,反向内阻为无限大。 在

v

v

vI为0V时,D导通,

v

v

vO输出低电平;在

v

v

vI为VCC时,D截止,

v

v

vO输出高电平。

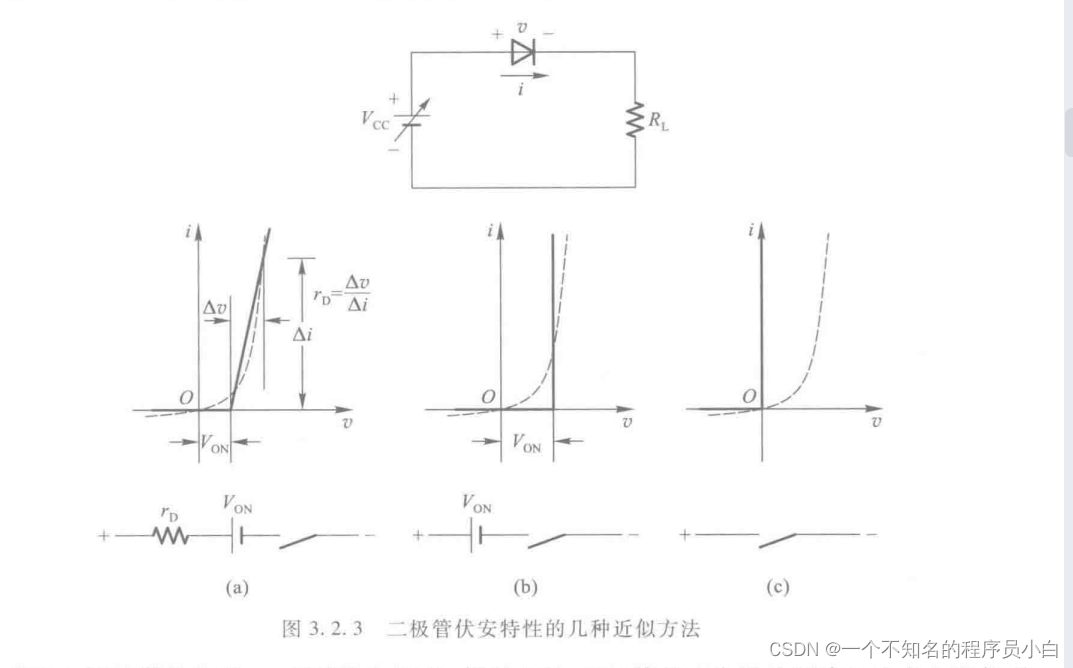

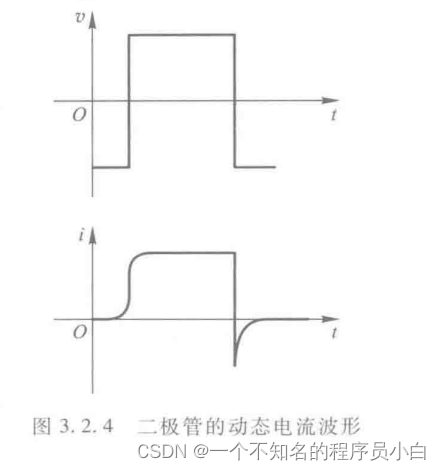

当外电路的电阻和电源Vcc都比较小,也就是说二极管的电阻和压降都不能被忽略时,此时二极管的特性近似于 a的折线 b当二极管内电阻可以被忽略,但压降不能被忽略时,此时二极管的特性近似于b的折线 实际大多情况是这种 c当二极管不管压降还是电阻都能被忽略时,二极管的特性近似于c的折线 二极管动态特性动态特性即二极管由断开到导通,由导通到断开过程中发生的变化

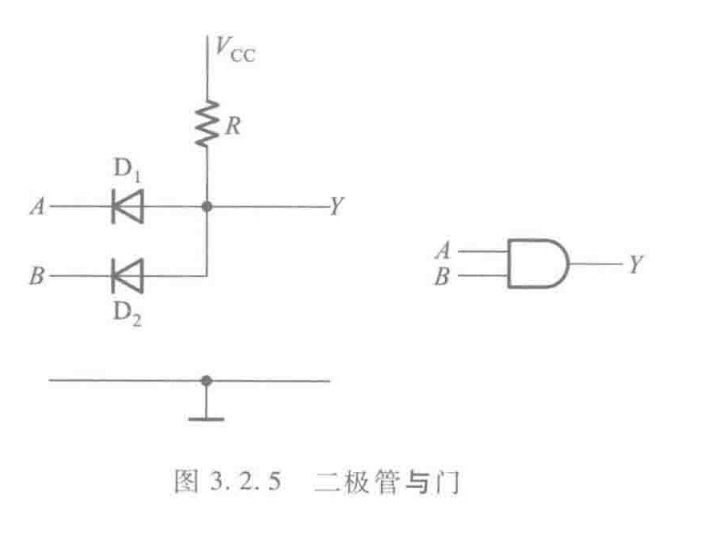

要等到PN结聚集足够的电荷,达到足够电流梯度时才有电流通过 由导通到断开时:由于PN结还有一定数量的电荷,所以会有较大的瞬态反向电流,反向电流会迅速衰减。 瞬态反向电流的大小和持续时间跟正向导通电流,二极管自身特性等有关。 二极管门电路 与门

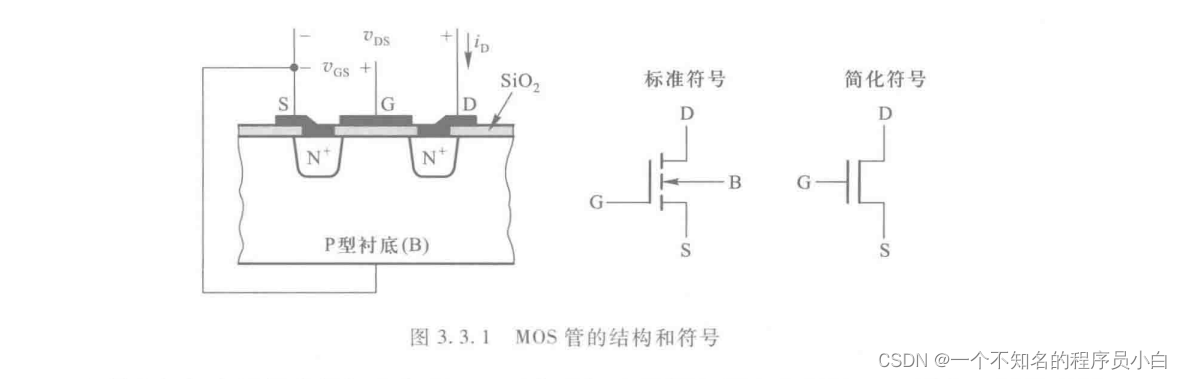

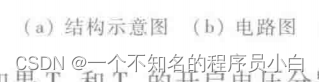

注意:通常二极管导通之后,如果其阴极电位是不变的,那么就把它的阳极电位固定在比阴极高0.7V的电位上;如果其阳极电位是不变的,那么就把它的阴极电位固定在比阳极低0.7V的电位上,人们把导通后二极管的这种作用叫做钳位。 或门工作原理 3、CMOS电路 1、MOS管的开关特性 1、结构和工作原理

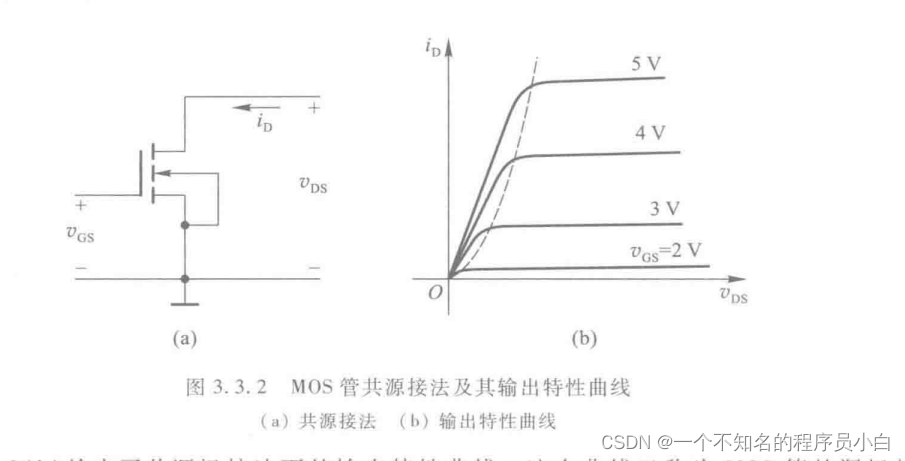

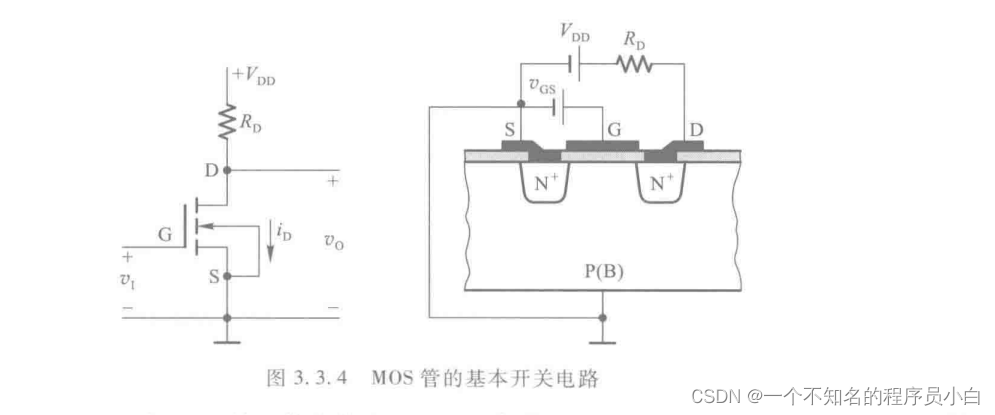

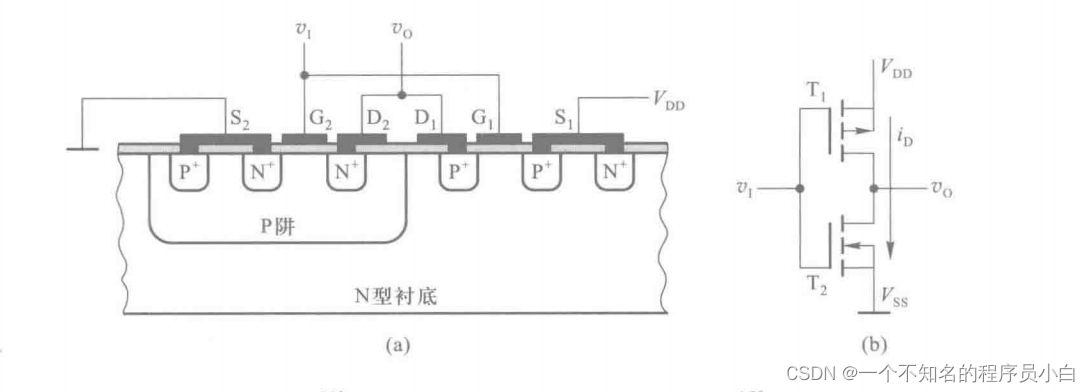

衬底上方有2个N型区,构成源极S和漏极D。 栅极G和衬底中间有绝缘层,确保栅源极不会产生电流 衬底接源极或者衬底接地,防止有电流从衬底流向源极或者导电沟道 工作原理给栅极接高电平,源极接低电平,衬底中的游离电子会被栅极的高电平吸引,从而聚集在栅极下方连通2个N型区,形成导电沟道,让漏极和源极导通。 2、输入和输出特性对于MOS管而言, 栅源作为输出端,漏源作为输出端,这样的接法称为共源接法。

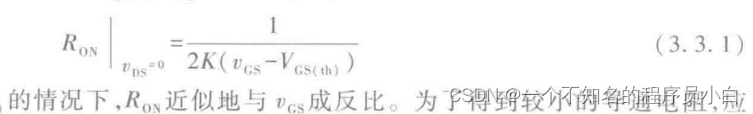

在 V V VGS < V V VGS(th)时,没有形成导电通道,漏极和源极之间的电阻无限大, i i iD的电流很小 可变电阻区

V

V

VGS >

V

V

VGS(th),且

V

V

VDS数值比较小时,这时导电通道相当于一个等效电阻。当

V

V

VDS趋近于0时,等效电阻

R

R

RON的大小跟

V

V

VGS的关系如下: 当

V

V

VGS >

V

V

VGS(th),且

V

V

VDS不再影响电流

i

i

iD大小时,这时就处于恒流区。 恒流区

i

i

iD的大小只受

V

V

VGS的影响。

V

V

VGS和电流

i

i

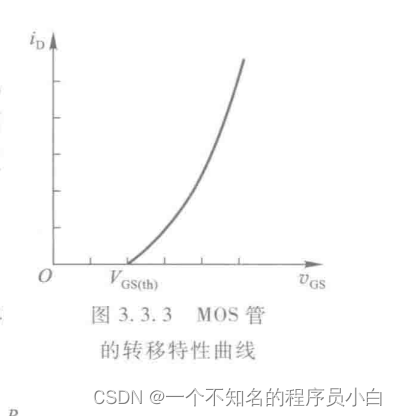

iD的关系 MOS管的转移特性曲线:描述 i i iD与 V V VGS的关系

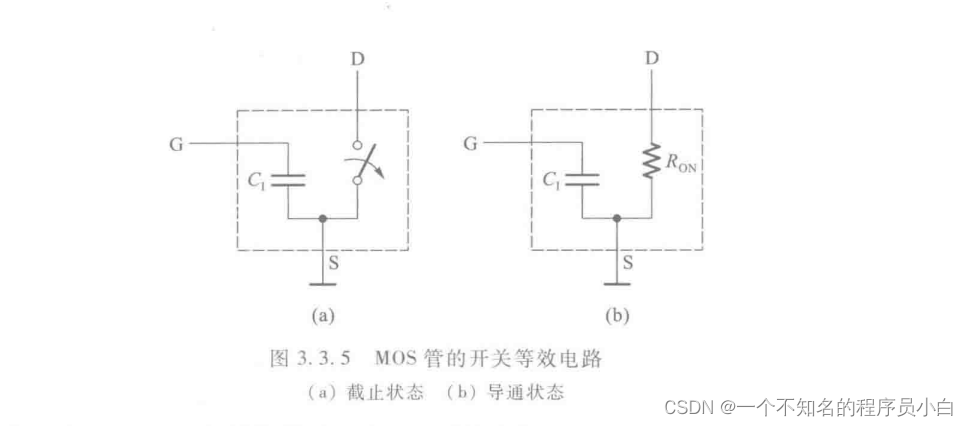

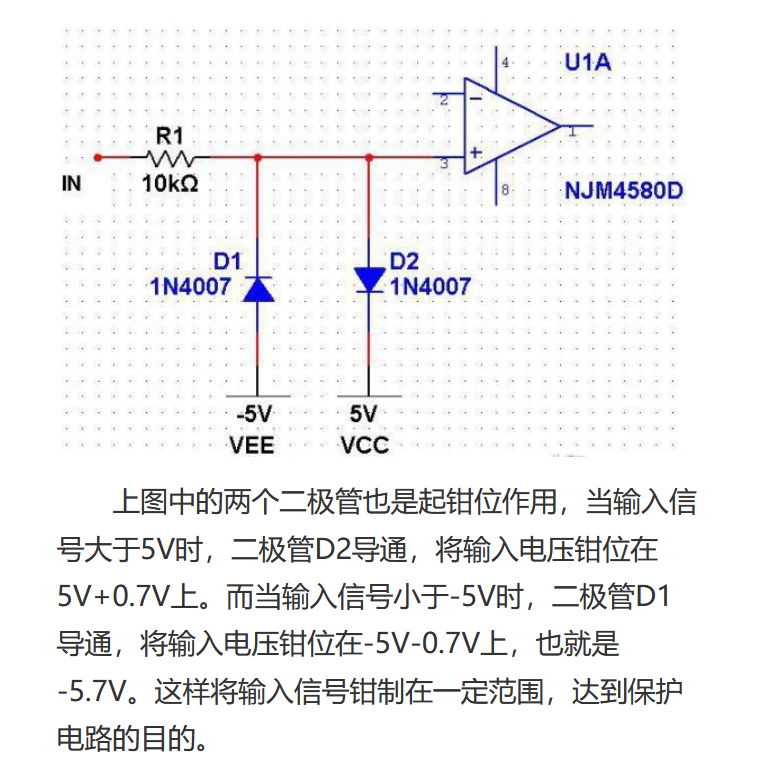

MOS管作为开关使用时的电路 作为开关使用时等效电路如图: 1.1、电路结构 由上面一个P沟道增强型MOS管(T1),下面一个N沟道增强型MOS管(T2)组成 1.2、工作原理 此时令 V V VDD > V V VGS(N) + | V V VGS(P`) | 当 v v v1=0= V V VIL时,T1导通,T2截止,(若T1导通时的等效电阻很小,T2截止的等效电阻很大)则电路图近似等效于图c,输出高电平VOH,且VOH约等于VDD当输入为低电压时同理 电压传输特性和电流传输特性 3、CMOS的静态输入特性和输出特性首先先了解相关概念 钳位:利用并联和二极管的特性,将电压固定在某个范围在不击穿二极管的情况下,二极管的电压等于 二极管导通压降+导通时另一端的输入电压,其实就是用二极管另一端的电压加上二极管限制此段电路的电压,从而限制跟此段电路并联的其他电路的电压(因为并联的电路电压都相等)。 从输入端观察输入电压和输入电流的关系称为输入特性 由于栅极与衬底的绝缘层极薄,容易被击穿,所以需要在输入端添加保护电路 图a为74HC保护电路,图b为4000系列保护电路 工作原理: D1为外接二极管,而D2是N型扩散区和衬底间自然形成的,称为分布式二极管。C1和C2为栅极等效电容在输入电压0< v v vi V V VDD时,D1导通,将 v v vG钳在 V V VDD+ V V VDF( V V VDF为二极管正向导通压降),保证加在C2(因为此时T2导通,所以加在C2而不是C1)上的电压不超过 V V VDD+ V V VDF在 v v vi< 0 时,D2导通,将 v v vG钳在- V V VDF(此处更准确说法为钳在 V V VSS- V V VDF,但- V V VSS为0,所以直接写作- V V VDF),保证加载C1上的电压不超过 V V VDD+ V V VDF(若 v v vG>RL>>RON,当T截止时, v v vO ≈ VDD2 = VOH;当T导通时, v v vO ≈ 0V = VOL,所以可以自行定制输出的高电平VDD2线与

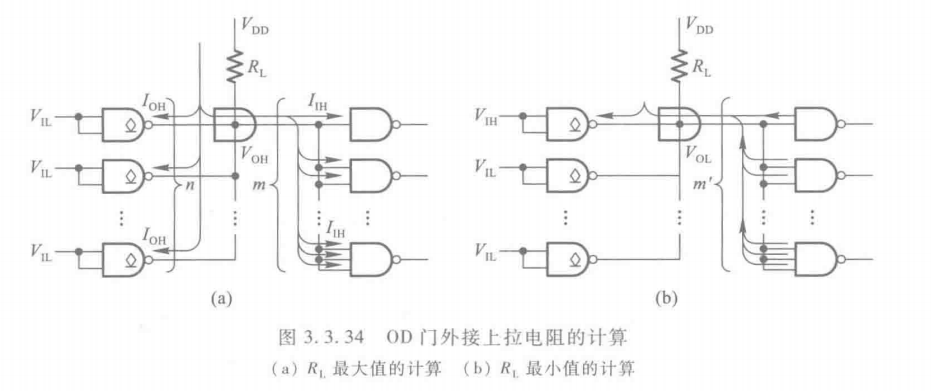

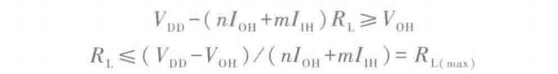

在线与输出端接有其他门电路作为负载的情况下,当所有的 OD门同时截止、输出为高电平时,由于 OD 门输出端MOS管截止时的漏电流和负载门的高电平输入电流同时流过 R,并在 R上产生压降,所以为保证输出高电平不低于规定的数值,RL不能取得过大。 可由如下公式计算RL最大值 此刻只有一个或多个T导通,则负载电流以及VDD产生的电流全都通过该一个或多个T,由于多了低电压输出端的电流,结合VDD所产生的电流,RL只能更小,才能保证低电平输出值不会太高。

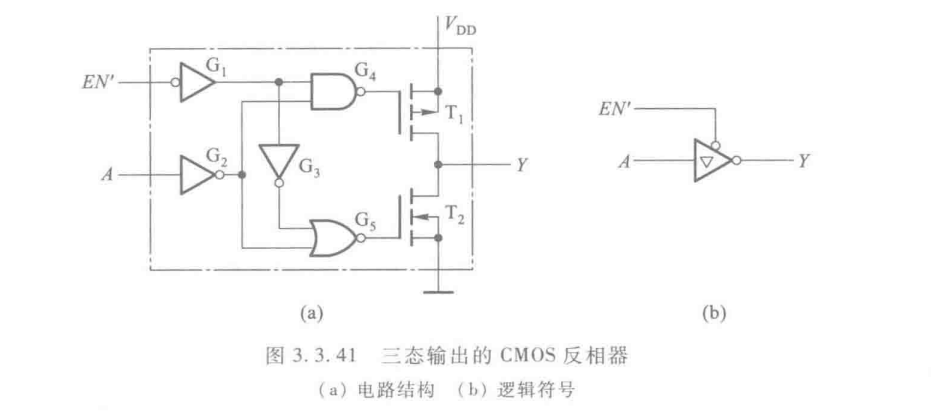

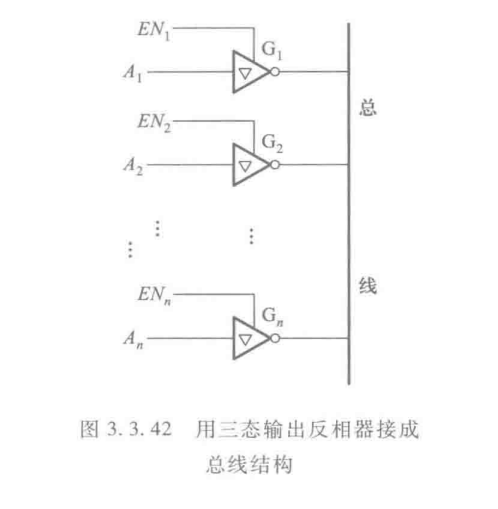

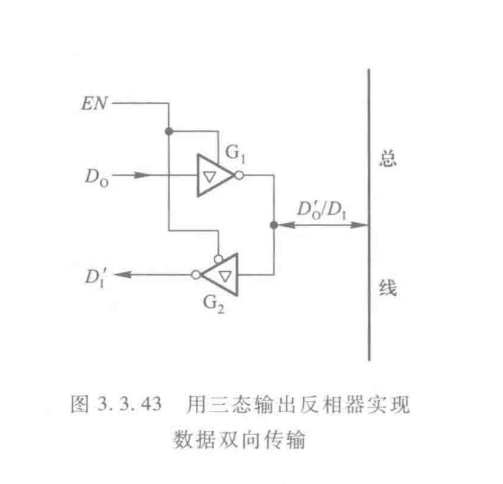

除了高低电平外,还有第三个状态–高阻态。 因为总是接在集成电路输出端,故又称为输出缓冲器 工作原理 当EN’=0时 若A=1,则T1截止,T2导通,Y输出低电平;若A=0,则T1导通,T2截止,Y输出高电平;即在EN’=0时,反相器处于正常工作状态,该三态门的逻辑函数为Y=A’ 当EN’=1时,不管A输入什么,T1和T2同时截止,呈现高阻态。 三态门组成总线结构控制各个EN端轮流等于1,保证任何时刻只有一个EN端为1,各个反相器的输出信号也就可以互不干扰的传输到总线上 图 3.3.43 是数据双向传输电路的结构图。 当EN=1时,G1工作而G2为高阻态,数据DO经过G1反相后送到总线上去。当EN=0时,G2工作而G1为高阻态,来自总线的数据D’I经过G2反相后送入电路内部 6、CMOS集成电路的正确使用(略)

6、CMOS集成电路的正确使用(略)

|

【本文地址】

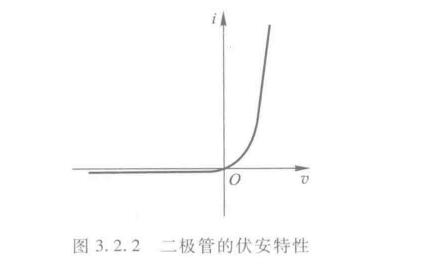

然而现实中的二极管无法在任何时候都满足于上面假定情况下的输出特性,二极管的近似理想输出特性公式和曲线如下

然而现实中的二极管无法在任何时候都满足于上面假定情况下的输出特性,二极管的近似理想输出特性公式和曲线如下

由图可知反向电阻不是无限大,正向电阻也不等于0。 虽然现实中能通过计算机辅助,准确分析二极管所形成的电路,但一般都不这么繁琐,都采用近似的较为快速的分析方式。 如下就是三种二极管的近似简化特性,用于现实中二级管电路的分析。

由图可知反向电阻不是无限大,正向电阻也不等于0。 虽然现实中能通过计算机辅助,准确分析二极管所形成的电路,但一般都不这么繁琐,都采用近似的较为快速的分析方式。 如下就是三种二极管的近似简化特性,用于现实中二级管电路的分析。 三种情况下的近似的福安特性曲线

三种情况下的近似的福安特性曲线

特性:设VCC为5V,导通压降VDF为0.7V,输入高低电平分别为VIH=3V,VIL=0V 当A或B端有一个低电平时,即D1或者D2只有一个导通,Y输出0.7V;当A和B都为高电平时,即D1和D2都导通,Y输出3.7V

特性:设VCC为5V,导通压降VDF为0.7V,输入高低电平分别为VIH=3V,VIL=0V 当A或B端有一个低电平时,即D1或者D2只有一个导通,Y输出0.7V;当A和B都为高电平时,即D1和D2都导通,Y输出3.7V

图(b)又称为漏极特性曲线 图b可分为三个工作区

图(b)又称为漏极特性曲线 图b可分为三个工作区 当

V

V

VGS 远大于

V

V

VGS(th)时,

R

R

RON和

V

V

VGS 成反比关系,即

V

V

VGS 越大越好。

当

V

V

VGS 远大于

V

V

VGS(th)时,

R

R

RON和

V

V

VGS 成反比关系,即

V

V

VGS 越大越好。 其中

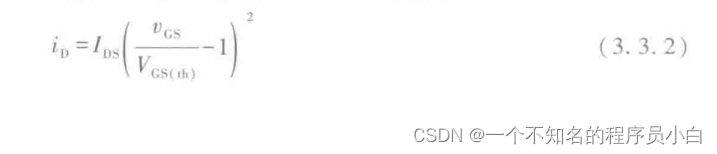

I

I

IDS为一个常数。 在

V

V

VGS 远大于

V

V

VGS(th)时,

i

i

iD近似的与

V

2

V^2

V2GS成正比

其中

I

I

IDS为一个常数。 在

V

V

VGS 远大于

V

V

VGS(th)时,

i

i

iD近似的与

V

2

V^2

V2GS成正比

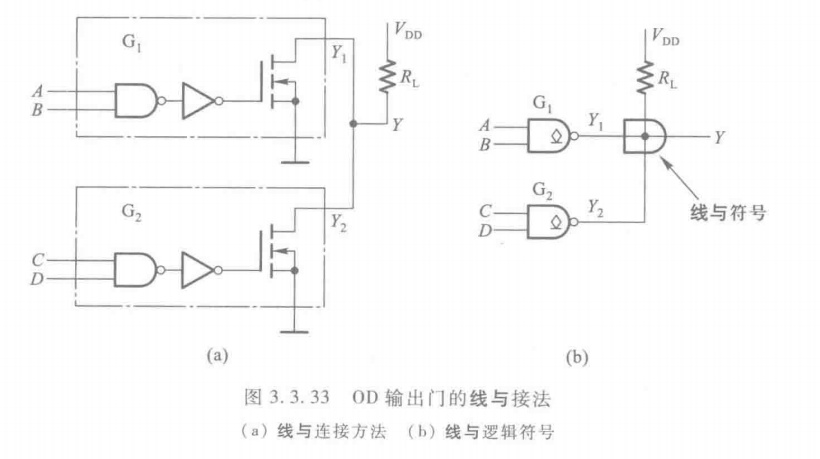

上图是将2个与非门通过线与接成与或非门 只有Y1和Y2同时为高电平时,Y才输出高电平

上图是将2个与非门通过线与接成与或非门 只有Y1和Y2同时为高电平时,Y才输出高电平

其中VOH为要求的最小高电平

其中VOH为要求的最小高电平

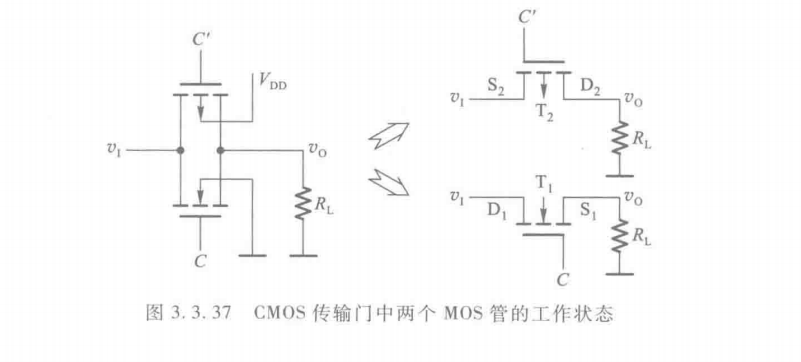

当C’=1,C=0时,若

v

v

vi 范围不超过 0V ~ VDD时,T1和T2同时截止,输出与输入之间呈现高阻态,传输门截止。 当C’=0,C=1时,若0V <

v

v

vi < VDD-VGS(th)N,则T1导通;若

v

v

vi

当C’=1,C=0时,若

v

v

vi 范围不超过 0V ~ VDD时,T1和T2同时截止,输出与输入之间呈现高阻态,传输门截止。 当C’=0,C=1时,若0V <

v

v

vi < VDD-VGS(th)N,则T1导通;若

v

v

vi