| MIPS单周期CPU设计 | 您所在的位置:网站首页 › mips指令集有多少条指令 › MIPS单周期CPU设计 |

MIPS单周期CPU设计

|

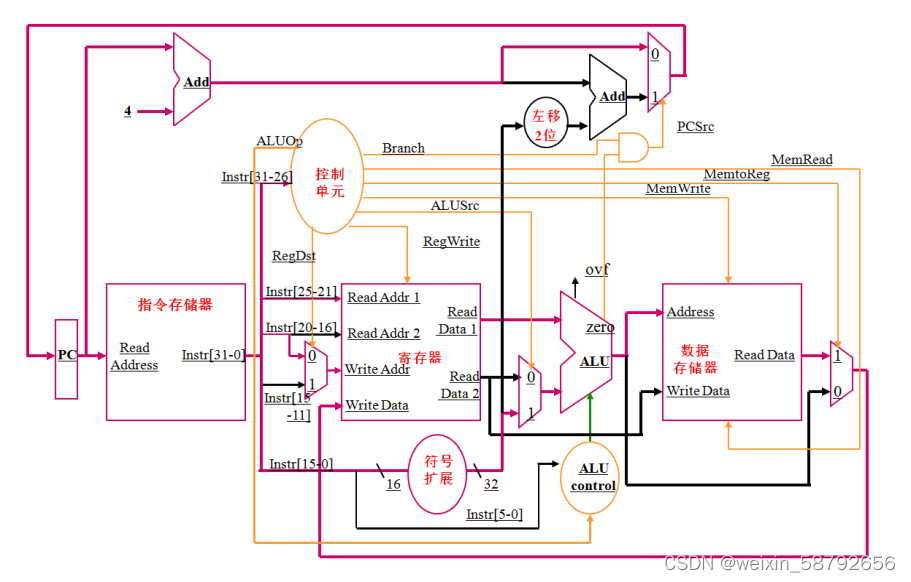

以下内容仅供参考 主要内容 用硬件描述语言(Verilog)设计单周期CPU,支持如下指令集: { lw,sw,add,sub, ori,lui,sll, srl, beq,bne,j } 用仿真软件Modelsim对汇编程序进行仿真测试. 基本要求 1. 熟悉硬件描述语言(Verilog)和仿真软件Modelsim; 2. 用硬件描述语言(Verilog)设计程序计数器模块(PcUnit); 3. 用硬件描述语言(Verilog)设计指令存储器模块(IM); 4.用硬件描述语言(Verilog)设计寄存器模块(GPR); 5.用硬件描述语言(Verilog)设计数据扩展模块(Extender); 6. 用硬件描述语言(Verilog)设计运算器模块(Alu); 7. 用硬件描述语言(Verilog)设计数据存储器模块(DMem); 8. 用硬件描述语言(Verilog)设计控制器模块(Ctrl); 9. 用硬件描述语言(Verilog)设计整机连接模块(Mips); 10.完成上述汇编程序的仿真调试。 2.1 CPU总体结构单周期的CPU总体结构如下图所示,其中包括程序计数器(PcUnit)、指令存储器(IM)、寄存器组(GPR)、运算器(Alu)、数据扩展单元(Extender)、数据存储器(DM)和控制器(Ctrl)。

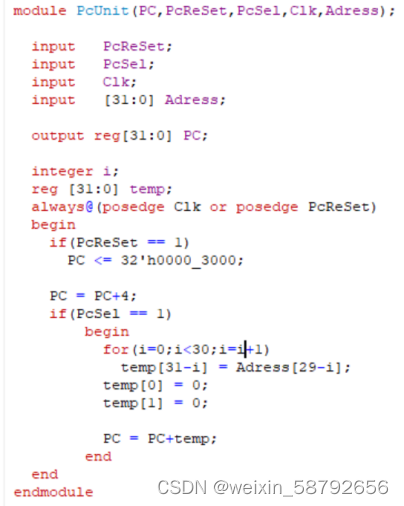

(1)功能描述 存放将要执行的指令的地址。 (2)模块接口 信号名 方向 描述 代码 Clk 输入 时钟信号

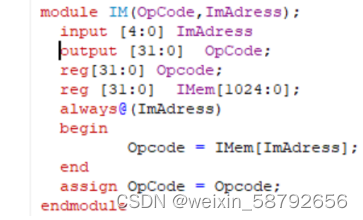

PcReSet 输入 PC复位信号 Adress 输入 扩展单元的32位数 PcSel 输入 Beq指令计算转移地址的指示信号 PC 输出 程序计数器的输出 2.3 IM(指令存储器) (1)功能描述 用于读取指令,在本程序中,指令存储器通过直接读取文本文件获取所需要执行的指令。 (2 )模块接口 信号名 方向 描述 代码 OpCode 输入 指令 ImAdress 输出 地址

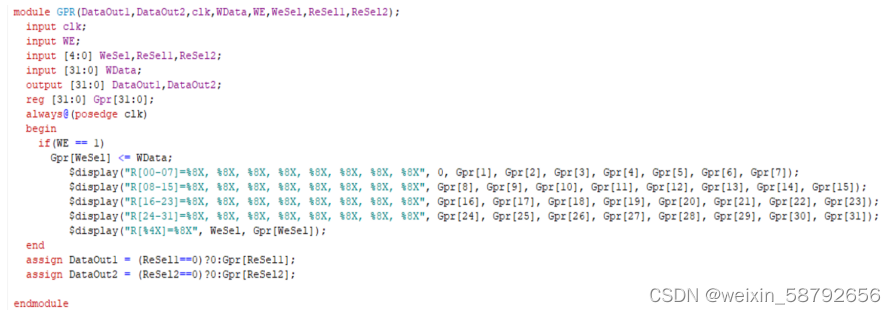

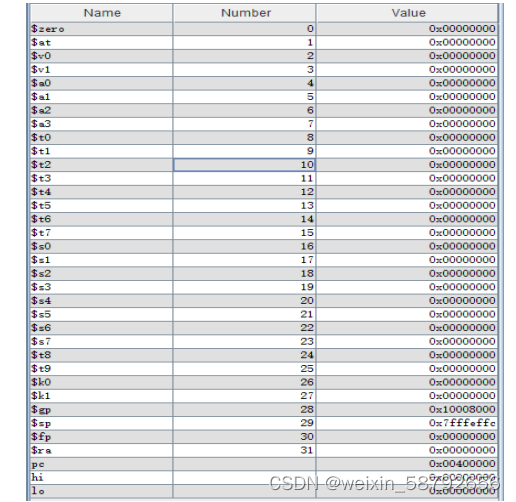

2.4 GPR(寄存器)设计 (1)功能描述 用于实现MIPS指令集中的32个寄存器。 (2)模块接口 信号名 方向 描述 代码 DataOut1 输出 读寄存器1的内容

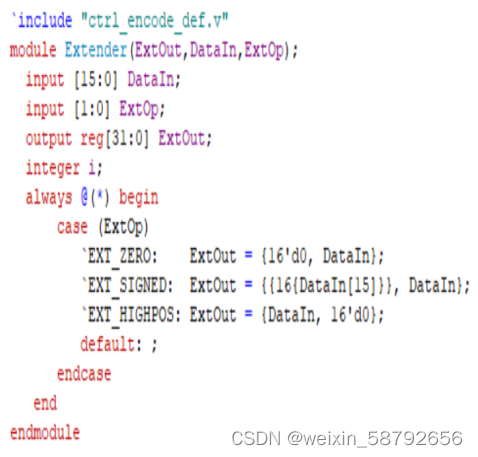

DataOut2 输出 读寄存器2的内容 clk 输入 时钟信号 WData 输入 写寄存器的内容 WE 输入 写使能信号 WeSel 输入 写寄存器的地址 ReSel1 输入 读寄存器1的地址 ReSel2 输入 读寄存器2的地址 2.5 Extender(扩展单元)(1)功能描述 将16位的数据扩展为32位数据。 (2)模块接口 信号名 方向 描述 代码 ExtOp 输出 扩展方式的控制信号 00:0扩展 01:符号扩展 10:将立即数扩展到高位  Extout 输出 符号扩展后的数据 DataIn 输入 初始数据

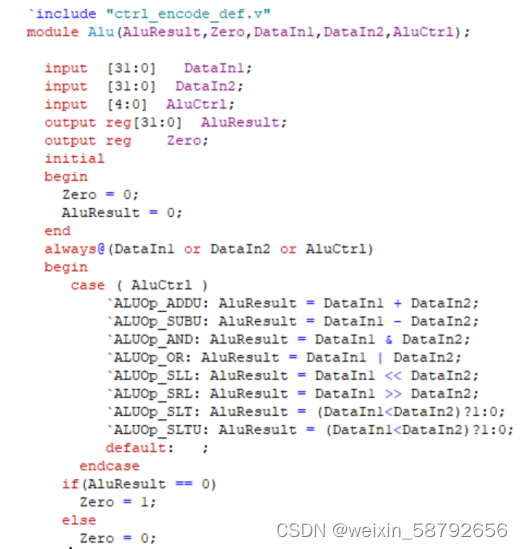

2.6 Alu(算术逻辑运算单元) (1)功能描述 算术逻辑单元,用于逻辑指令计算和跳转指令比较。 (2)模块接口 信号名 方向 描述 代码 AluResult 输出 计算结果  Zero 输出 零信号 DataIn1 输入 操作数1 DataIn2 输入 操作数2 AluCtrl 输入 控制码

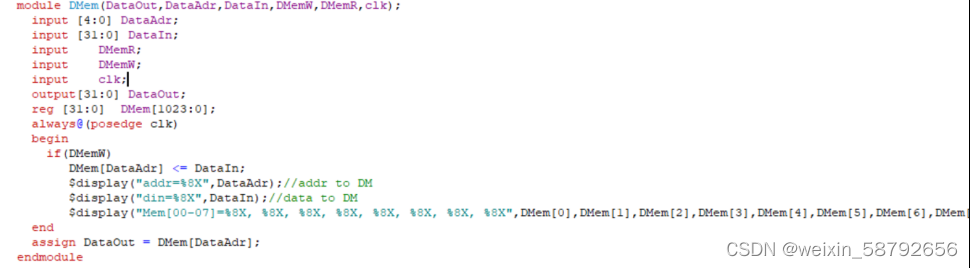

2.7 DMem(数据存储器) (1)功能描述 该部分控制内存存储,用于内存存储、读写 (2)模块接口 信号名 方向 描述 代码 DMemW 输入 写使能信号

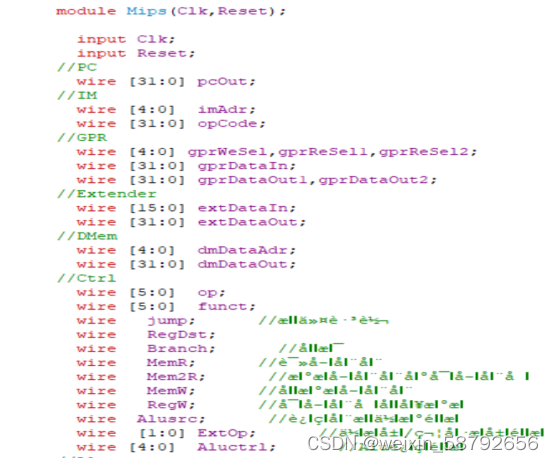

DMemR 输入 写使能信号 clk 输入 时钟信号 DataAdr 输入 地址 DataIn 输入 输出地址对应的数据 DataOut 输出 将数据写入对应地址 2.8 Ctrl(控制器)(1)功能描述 控制器控制各模块有条不紊的工作,主要产生控制信号。 (2 )模块接口 信号名 方向 描述 代码 jump 输出 跳转指令 RegDst 输出 选择寄存器的数据来源 Branch 输出 分支指令 MemR 输出 数据寄存器的写使能信号 Mem2R 输出 写入寄存器 MemW 输出 写入数据存储器 RegW 输出 写入寄存器 Alusrc 输出 ALU第二个操作数的来源 ExtOp 输出 拓展信号 Aluctrl 输出 ALU控制信号 OpCode 输入 操作码 funct 输入 指令的funct字段 2.9 Mips(模型机)(1)功能描述 用于将各功能模块连接成一个整体单周期CPU。 (2 )模块接口 信号名 方向 描述 代码 Clk 输入 时钟信号  Reset 输入 复位信号 3.1测试文件 测试程序 测试机器码   3.2 测试结果分析

3.2.1 lui $1,0x1000指令

3.2 测试结果分析

3.2.1 lui $1,0x1000指令

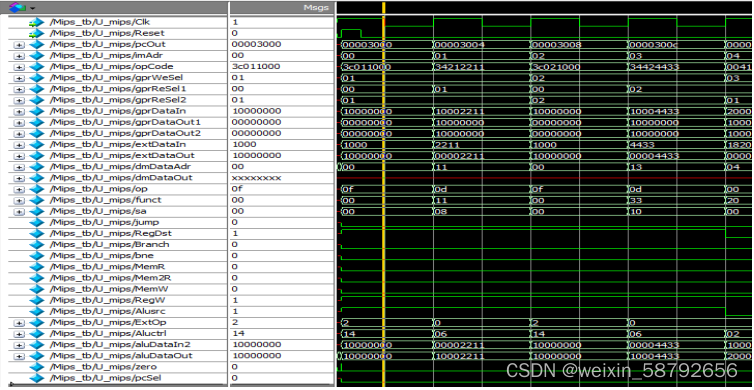

该指令的仿真结果如下图所示,该指令的功能是将0x1000送入$1寄存器,指令的执行结果$1寄存器的值是0x10000000,仿真结果与指令的预期结果是一致的,说明该指令设计正确。

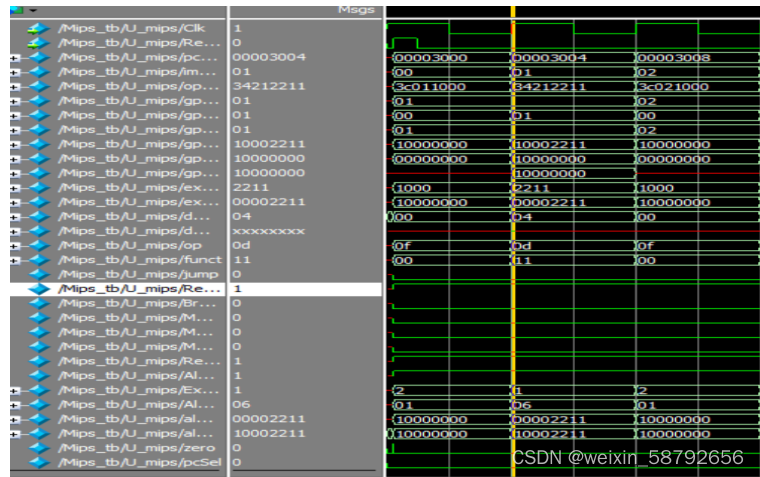

3.2.2 ori $1,$1,0x2211指令 该指令的仿真结果如下图所示,该指令的功能是将$1寄存器与数0x2211进行“或”运算,指令的执行结果$1寄存器的值是0x00002211,仿真结果与指令的预期结果是一致的,说明该指令设计正确。

|

【本文地址】