| 边沿触发器 | 您所在的位置:网站首页 › jk触发器具有四种功能 › 边沿触发器 |

边沿触发器

|

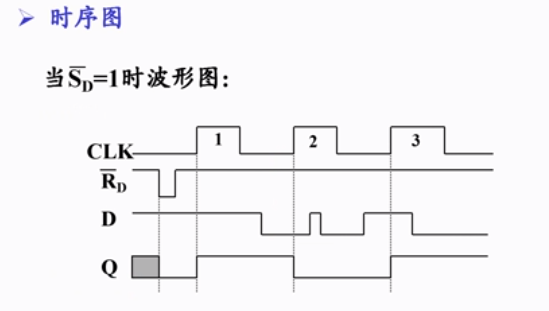

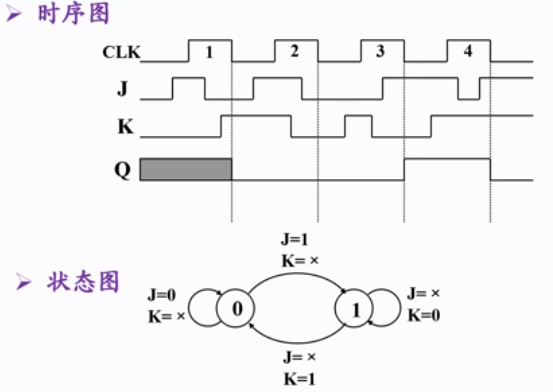

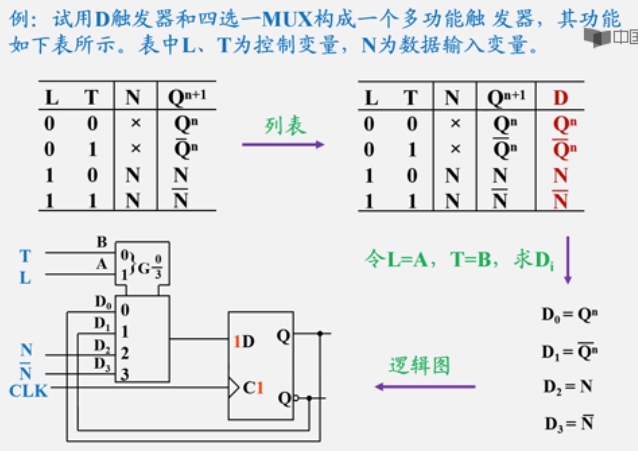

边沿触发器 || D触发器 || JK触发器 || 逻辑功能转换 || 脉冲工作特性 || 重难点 || 数电1.触发器基础 前面介绍了门控锁存器。对于门控锁存器,在控制信号C有效期间,输入信号的任何变化都将直接引起锁存器输出状态的改变。因此也可以说,门控锁存器是对电平敏感的。 本文将介绍触发器(FF:Flip-Flop),触发器是对边沿敏感的。  触发器分为两种类型: 主从触发器(现在很少见)边沿触发器主从触发器现在很少见了,实际使用的都是边沿触发器,所以下面只介绍边沿触发器。  下面将介绍两种类型的边沿触发器: D触发器JK触发器1.1 边沿D触发器边沿D触发器的电路结构与逻辑符号如图所示,使用了3个由与非门构成的RS锁存器。 输入D从一个锁存器输入,两个锁存器共用时钟信号CLK,第三个锁存器产生触发器状态输出Q和Q非。此外还有一个异步置零端(RD非)和一个异步置一端(SD非)。 在边沿触发器的逻辑符号中,在C1端加上了动态符号——一个箭头,说明触发器只对时钟的上升沿响应,如果再在动态符号前面加上一个圆圈,则表示触发器只对时钟的下降沿响应。 输入端D前面标有一个“1”,表示这个输入端受时钟信号的影响,而在置一端和置零端S和R的前面没有标注1,说明这两个输入端不受时钟信号的影响,也就是说他们是异步置一和异步置零端。 靠近S和R的边框标有小圆圈,表明置1端和置0端是低电平有效。  关于上示电路的工作原理,请看视频1的3'15"~5'07"处,由于我实在是头晕,所以跳过这部分。 下面是D触发器的特性表。  下面是时序图,  1.2 边沿JK触发器 1.2 边沿JK触发器下面是负边沿JK触发器的逻辑图,是在正边沿D触发器的基础上,添加了部分逻辑电路。 它有两个输入端J和K。 CLK时钟信号经过反相后,加到正边沿D触发器的时钟输入端,因此得到的JK触发器是负边沿有效的。JK触发器的逻辑符号如下图右侧所示,C1时钟输入前面加了一个小圆圈,表示触发器只对时钟的下降沿响应。 另外要重点记忆JK触发器的特性方程。  下面是JK触发器的特性表,  时序图和状态图如下图所示,  1.3 T触发器 1.3 T触发器 1.4 T'触发器 1.4 T'触发器 后面会经常用到T'触发器。 1.4 部分集成触发器 2.触发器逻辑功能转换 2.触发器逻辑功能转换已有触发器加上转换电路构成代求触发器。  2.1如何把JK触发器转换为D触发器 2.1如何把JK触发器转换为D触发器 2.2如何把JK触发器转换为T触发器 2.2如何把JK触发器转换为T触发器  2.3如何把JK触发器转换为T‘触发器 2.3如何把JK触发器转换为T‘触发器 2.4如何把D触发器转换为T触发器和T'触发器 2.4如何把D触发器转换为T触发器和T'触发器 2.5 例 2.5 例活用数据选择器MUX。  3触发器的脉冲工作特性(了解)3.1输入信号的建立和保持时间 3触发器的脉冲工作特性(了解)3.1输入信号的建立和保持时间 建立时间是信号D提前于触发边沿的时间。  保持时间是信号D在触发边沿到来后保持的时间。 3.2触发器的传输延迟时间 3.3触发器的最高时钟频率 3.3触发器的最高时钟频率 3.4触发器的最小脉冲宽度 3.4触发器的最小脉冲宽度 丢题目,  视频:MOOC-数字逻辑电路-第六单元 时序逻辑电路(1)-触发器 |

【本文地址】