| ChipScope 使用问题和解决方案 | 您所在的位置:网站首页 › ise找不到cable › ChipScope 使用问题和解决方案 |

ChipScope 使用问题和解决方案

|

背景介绍

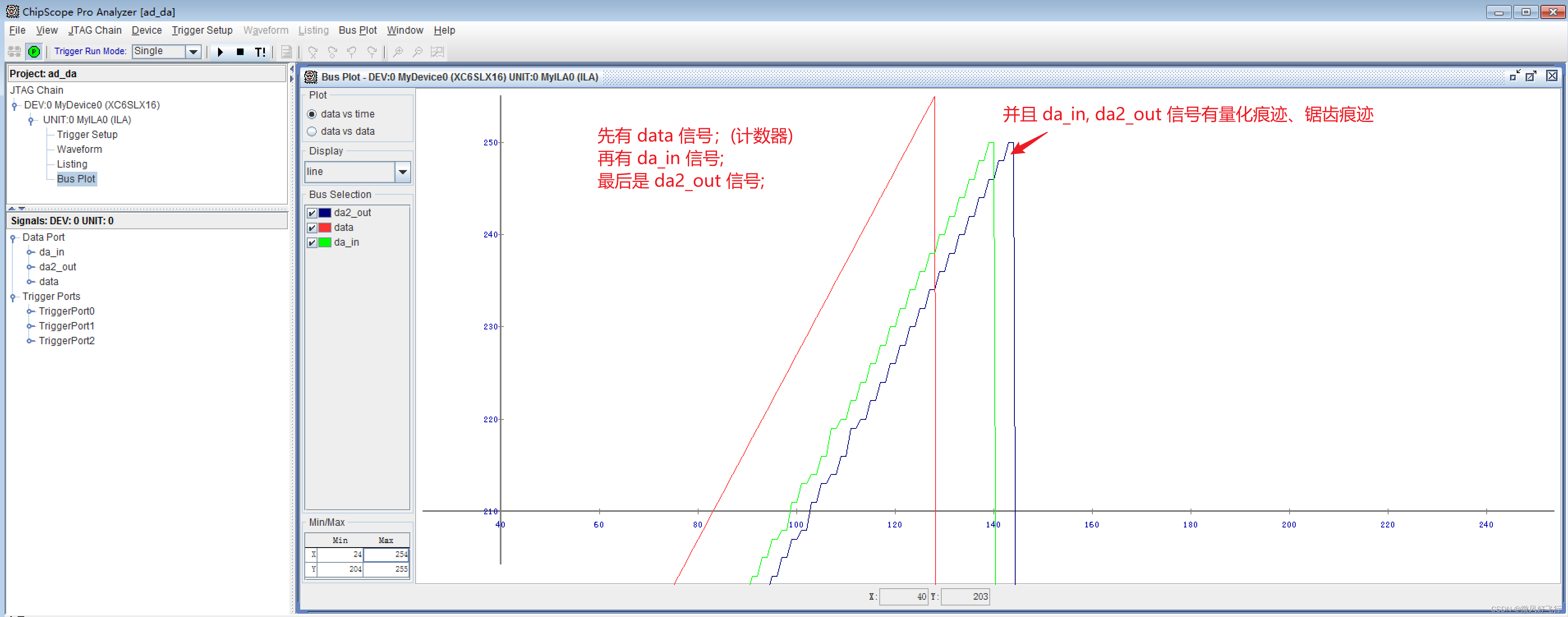

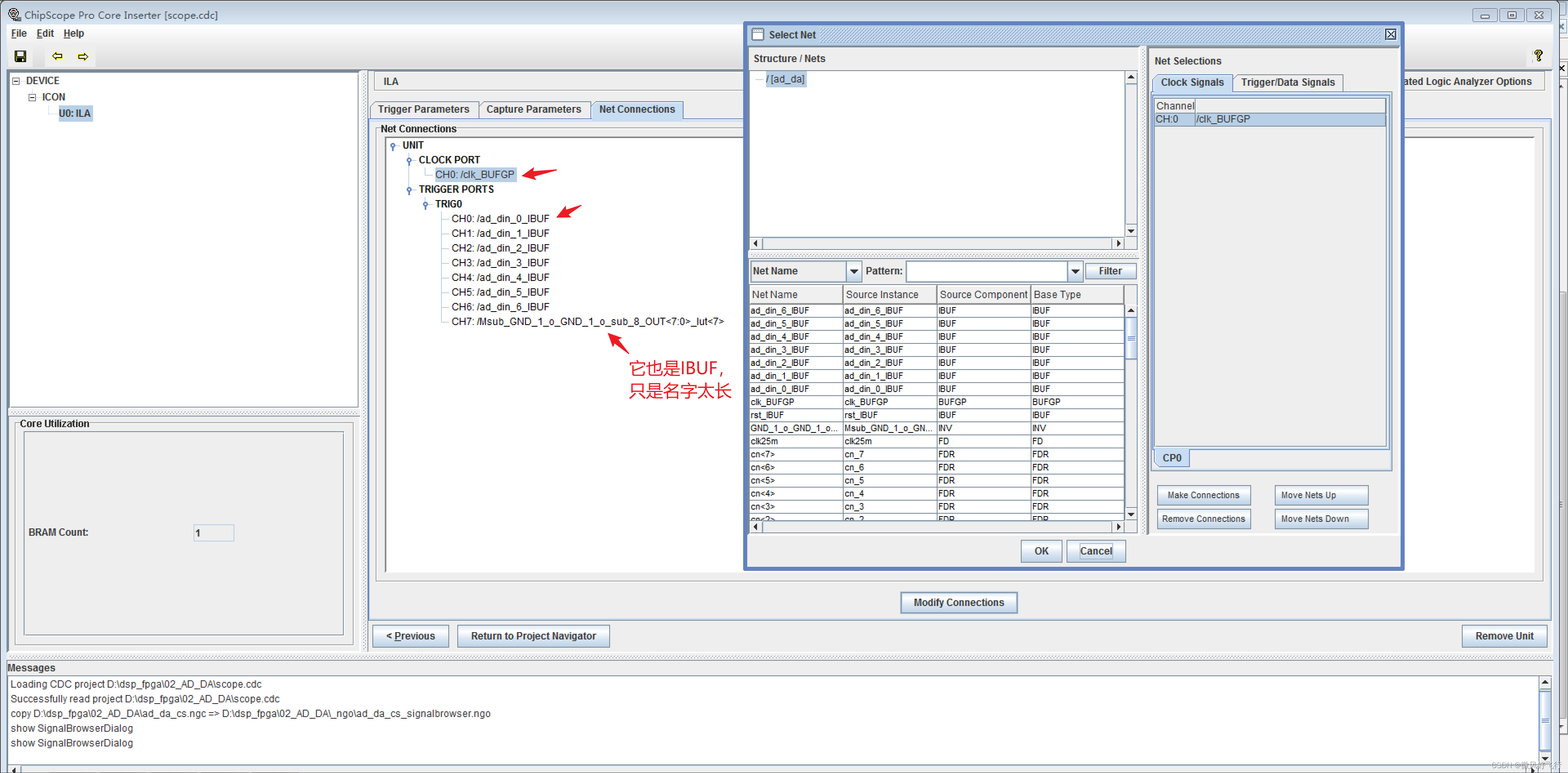

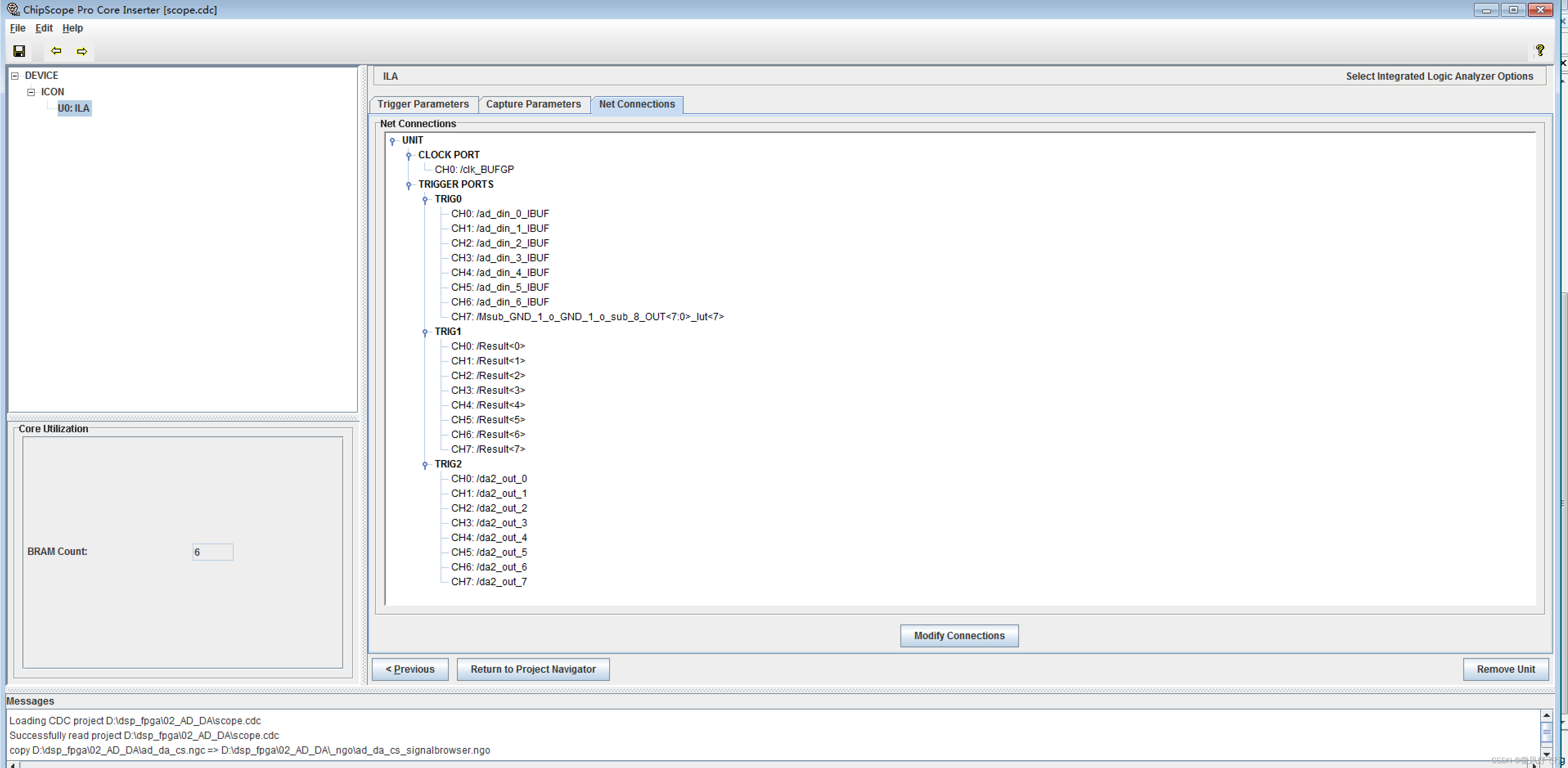

我最近在学习FPGA开发技术,用杜勇老师的《Xinlinx FPGA数字信号处理设计》一书,按照书中的例子,对 CXD301 开发板进行ADC、DAC示例的调试,使用 ChipScope 软件进行在线逻辑分析。遇到了下面的问题,并给出了解决办法。 问题1:项目不能放在虚拟机外部项目不能放在虚拟机外部,否则执行 Xilinx 的 chipscope 综合时,会报告错误,看具体原因是无法执行 mkdir 命令!导致mkdir失败的具体原因不明,可能和无法正常访问VirtualBox的共享目录有关。 可以从日志文件E:\projects\dsp_fpga\02_AD_DA\_ngo\cs_icon_pro\coregen.log中看到失败原因。 INFO:encore:314 - Created non-GUI application for batch mode execution. Wrote CGP file for project 'coregen'. INFO:sim:172 - Generating IP... Resolving generic values... Finished resolving generic values. Generating IP... Gathering HDL files for icon_pro root... Creating XST project for icon_pro... Creating XST script file for icon_pro... Creating XST instantiation file for icon_pro... Running XST for icon_pro... XST: HDL Parsing WARNING:coreutil - XST failed for icon_pro. ERROR:HDLCompiler:1091 - "Unknown" Line 0: Save failed due to mkdir failure ERROR:HDLCompiler:1091 - "Unknown" Line 0: Save failed due to mkdir failure ERROR:HDLCompiler:1091 - "Unknown" Line 0: Save failed due to mkdir failure ERROR:HDLCompiler:1091 - "Unknown" Line 0: Save failed due to mkdir failure invoked from within "runXST $ComponentName GenerationOptions $TopLevel" (procedure "deliverXSTNetlist" line 15) invoked from within "deliverXSTNetlist $ComponentName {} "root" $BaseIP " (procedure "components::icon_pro::generate" line 31) invoked from within "components::${ComponentName}::generate 1" (procedure "::xilinx::sim::generation::generatePsfCore" line 59) invoked from within "::xilinx::sim::generation::generatePsfCore {chipscope_icon_v1_06_a} {icon_pro} {ALL}"ERROR:sim - XST failed for icon_pro. ERROR:HDLCompiler:1091 - "Unknown" Line 0: Save failed due to mkdir failure ERROR:sim - Error found during generation. ERROR:sim - Failed to generate 'icon_pro'. XST failed for icon_pro. ERROR:HDLCompiler:1091 - "Unknown" Line 0: Save failed due to mkdir failure ERROR:sim:877 - Error found during execution of IP 'ICON (ChipScope Pro - Integrated Controller) v1.06.a'解决方案:将项目目录从外部的共享目录下,整个拷贝到虚拟机本机磁盘上,重新打开项目进行综合即可。 问题2:不会配置"网络连接"(Net Connections)导致实现(Implement)失败《Xinlinx FPGA数字信号处理设计》一书中没有详细说明如何将“通道(Channel)”与"网络(Net)"相连。如果将通道直接和"线(wire)"相连,则会出现警告,并且后续的实现过程会失败。 解决方案: Channel 必须和寄存器、BUF相连才可以。下面的连接方式才能成功。 这是因为 FPGA 中的信号具有时序特性,而 Chipscope 是一个异步的调试工具,它的输入端口也需要满足时序要求。如果将 channel 直接连接到 wire 端口,可能会存在时序不稳定的问题,导致 Chipscope 无法正确地读取信号。 因此,为了保证信号的时序稳定性,连接到 Chipscope 输入端口的信号通常需要通过寄存器进行缓冲。这样可以确保信号的时序满足要求,同时还可以避免信号冲突和干扰,提高调试的准确性和可靠性。 书中 ADC_DAC 示例程序的 ChipScope Net Connection 配置如下所示。

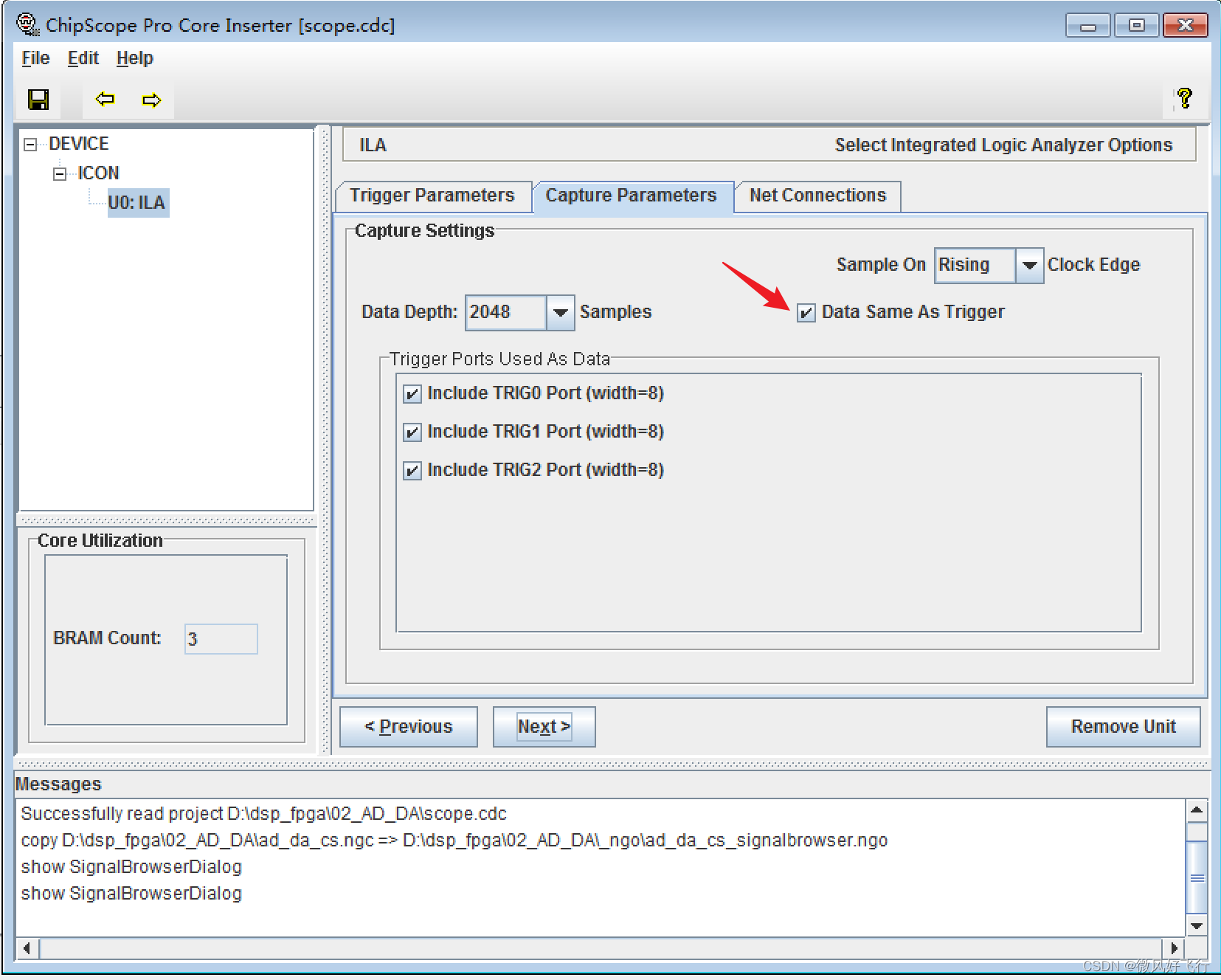

在 Chipscope 工具的 Parameters 选项卡下,有一个 Data same as Trigger 选项,它是一种触发器设置模式,它可以让用户选择在何时触发信号捕获和采样,以便进行调试和分析。也是将 Trigger Ports 作为 Data Ports 的意思。 在 Data as Trigger 模式下,用户可以选择一个数据信号作为触发器,当该信号发生特定的条件时,Chipscope 将自动触发信号的捕获和采样。例如,用户可以选择一个特定的数据值、一个数据范围、或者一个特定的时钟周期作为触发条件,这样当触发条件满足时,Chipscope 将自动捕获和采样信号。 Data as Trigger 的主要作用是帮助用户在复杂的电路中快速定位和分析问题,通过触发器的设置,可以精确定位信号的采样位置,从而更快地找到问题所在,加快调试和分析的速度。同时,Data as Trigger 也可以避免由于信号的随机性和不可预测性导致的调试困难,提高调试的准确性和可靠性。 配置 Channel 和 Net 的小技巧批量对应法:

|

【本文地址】

| 今日新闻 |

| 推荐新闻 |

| 专题文章 |

不能直接将 CH0 和 clk 信号相连。原因如下: 在配置 Chipscope 的时候,通常需要将各个模块的信号连接到 Chipscope 的输入端口,以便进行调试和分析。在连接的时候,需要将信号通过一个寄存器来缓冲,然后再将缓冲后的信号连接到 Chipscope 的输入端口。

不能直接将 CH0 和 clk 信号相连。原因如下: 在配置 Chipscope 的时候,通常需要将各个模块的信号连接到 Chipscope 的输入端口,以便进行调试和分析。在连接的时候,需要将信号通过一个寄存器来缓冲,然后再将缓冲后的信号连接到 Chipscope 的输入端口。 我是如何找到这些 Net 的呢?是看 RTL 电路图发现的,verilog 模块中的信号命并不一定在 Net 中都有,而且要找到信号连接的BUF模块的端口,用他们分配给ChipScope的Channel才可以。

我是如何找到这些 Net 的呢?是看 RTL 电路图发现的,verilog 模块中的信号命并不一定在 Net 中都有,而且要找到信号连接的BUF模块的端口,用他们分配给ChipScope的Channel才可以。