| 瑞芯微RK3528 4K影音专用芯片规格参数简介Datasheet | 您所在的位置:网站首页 › h618芯片参数 › 瑞芯微RK3528 4K影音专用芯片规格参数简介Datasheet |

瑞芯微RK3528 4K影音专用芯片规格参数简介Datasheet

|

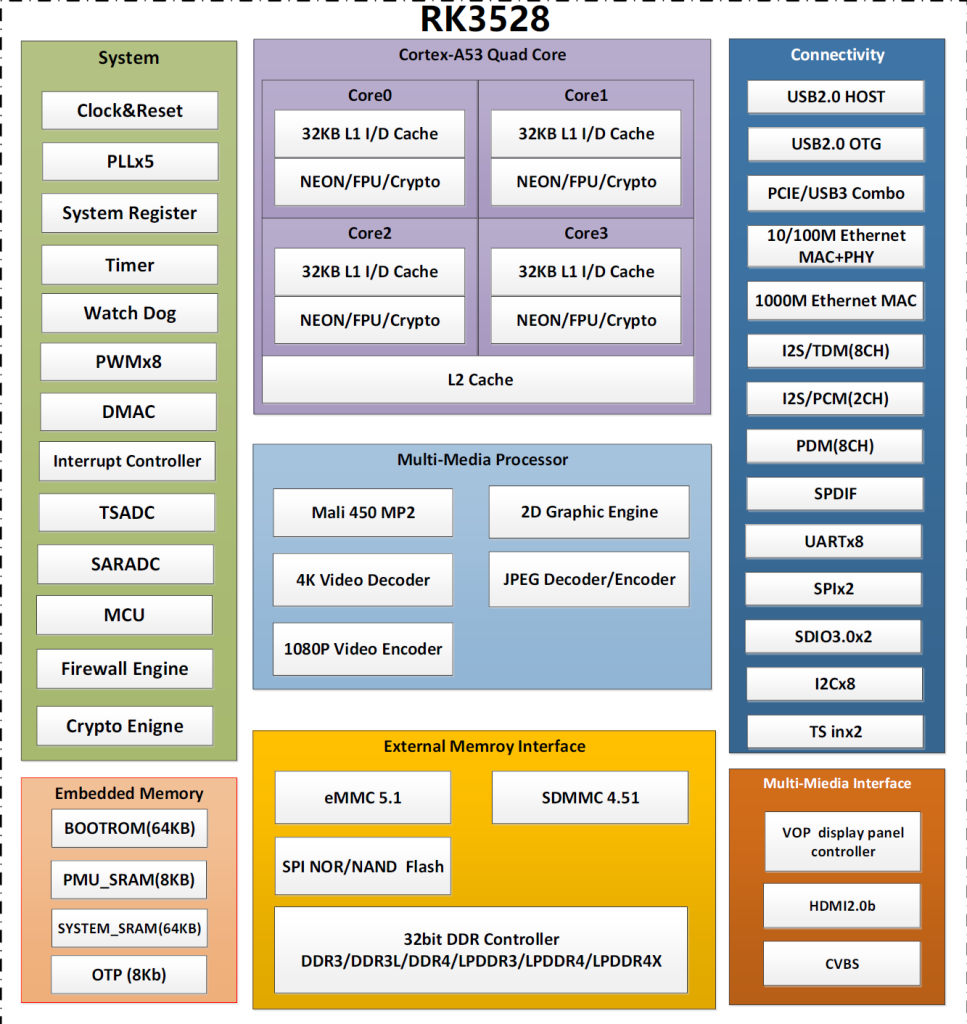

RK3528是一款高性能四核应用处理器,专为智能IPTV、OTT BOX、DBS和高端多媒体应用而设计,是一款适用于4K视频应用的高集成度、低成本的SoC。具有丰富的功能接口,可以用于行业产品定制。本文主要介绍RK3528的规格参数(datasheet),方便客户选型,定义产品。  RK3528功能框图 RK3528采用四核Cortex-A53处理器,集成了独立的Neon和FPU协处理器,还集成了共享的L2缓存,以提高系统性能。集成ARM Mali-450 GPU支,持高分辨率显示和游戏,它可以处理OpenGL ES1.1/2.0、OpenVG等图形程序。 基于ARM TrustZone的专用安全系统,用于处理视频和显示应用程序的安全管理。它包括加密、rng、防火墙引擎,以保证整个系统的安全。32位DRAM接口,提供高带宽DDR3(L)/LPDDR3/DDR4/LPDDR4(4X)支持。 高级视频解码器支持高达10位像素的4K超高清视频的60fps播放。它支持H.265、H.264、AVS2等视频标准。高级视频编码器还支持60fps的1080p高清视频捕获。它支持H.265和H.264编码。显示控制器支持灵活的表面和输出流。输出包括两个可在HDR、CEC、HDCP2.2支持的HDMI 2.0发射器和CVBS之间切换的输出。 除了这些主要元件外,RK3528处理器还具有广泛的外围接口,如pcie2、usb2、mac、i2s等,以实现与无线基带、其他通信外围设备、音频编解码器、电源管理和大容量存储的通信。 1.2.1 Application Processor Quad core ARM Cortex-A53 Full implementation of the ARM v8-A architecture. Separately Integrated Neon and FPU TrustZone Extension support One isolated voltage domain to support DVFS 1.2.2 Graphic Processor ARM Mali-450 GPU Concurrent multi-core processing Separate vertex(geometry) and fragment(pixel) processing for maximum parallel throughput OpenGL ES 1.1/2.0 and OpenVG 1.1 support One isolated voltage domain to support DVFS 1.2.3 Memory Organization Internal on-chip memory BootRom Support system boot from the following device: SPI interface eMMC interface SD/MMC interface Support system code download by the following interface: RK3528 Datasheet Rev 1.0 BY SCENSMART USB interface 64KB Share Memory 8KB PMU SRAM External off-chip memory eMMC Interface Fully compliant with JEDEC eMMC5.1 specification Support HS400, support CMD Queue Support three data bus width: 1bit, 4bits or 8bits SD/MMC Interface Compatible with SD3.0, MMC ver4.51 Data bus width is 4bits Flexible Serial Flash Interface (FSPI) Support transfer data from/to serial flash device Support 1bit, 2bits or 4bits data bus width Dynamic Memory Interface : DDR3(L)/LPDDR3/DDR4/LPDDR4(4X) Compatible with JEDEC standard DDR3/DDR3L/LPDDR3/DDR4/LPDDR4/LPDDR4X SDRAM Supports 32 Bits data width, 4GB addressing space 1.2.4 System Component MCU Cortex-M0 in PMU domain integrate 8KB TCM. Integrated Debug Controller with JTAG interface CRU (clock & reset unit) Support total 5 PLLs to generate all clocks One oscillator with 24MHz clock input Support clock gating control for individual components Support global soft-reset control for whole chip, also individual soft-reset for each component PMU (power management unit) Multiple configurable work modes to save power by different frequency or automatic clock gating control or power domain on/off control Lots of wakeup sources in different mode Support 4 separate voltage domains,,VDD_ARM,VDD_GPU,VDD_LOGIC,VDD_PMU. Timer Support 2 secure timers with 64bits counter and interrupt-based operation Support 6 non-secure timers with 64bits counter and interrupt-based operation Support 1 high precision timer. Support two operation modes: free-running and user-defined count for each timer Support timer work state checkable PWM Support 8 on-chip PWMs (PWM0~PWM7) with interrupt-based operation Programmable pre-scaled operation to bus clock and then further scaled Embedded 32-bit timer/counter facility Support capture mode Support continuous mode or one-shot mode Provides reference mode and output various duty-cycle waveform Optimized for IR application for PWM3, PWM7 Watchdog 32-bit watchdog counter Counter counts down from a preset value to 0 to indicate the occurrence of a timeout RK3528 Datasheet Rev 1.0 BY SCENSMART WDT can perform two types of operations when timeout occurs: Generate a system reset First generate an interrupt and if this is not cleared by the service routine by the time a second timeout occurs then generate a system reset One Watchdog for non-secure application One Watchdog for secure application One Watchdog for MCU Interrupt Controller Support 256 SPI interrupt sources input from different components inside RK3528 Support 16 software-triggered interrupts Input interrupt level is fixed, high-level sensitive or rising edge sensitive Support different interrupt priority for each interrupt source, and they are always software-programmable DMAC Micro-code programming-based DMA Linked list DMA function is supported to complete scatter-gather transfer Support data transfer types including memory-to-memory, memory-to-peripherals, peripherals-to-memory Totally three embedded DMA controllers for peripheral system Each DMAC features: Support 8 channels 32 hardware requests from peripherals 2 interrupt output Support TrustZone technology and programmable secure state for each DMA channel Secure System Embedded one cipher engines Support Link List Item (LLI) DMA transfer Support SHA-1, SHA-256/224, MD5,SM3 with hardware padding Support HMAC of SHA-1, SHA-256, MD5,SM3 with hardware padding Support AES-128, AES-192, AES-256 encrypt and decrypt cipher Support DES and TDES cipher Support AES ECB/CBC/OFB/CFB/CTR/CTS/XTS/GCM/CBC-MAC/CMAC mode Support SM4 ECB/CBC/OFB/CFB/CTR/CTS/XTS/GCM/CBC-MAC/CMAC mode Support DES/TDES ECB/CBC/OFB/CFB mode Support up to 4096 bits PKA mathematical operations for RSA Support SM2/SM3/SM4 cipher Support generating random numbers, one secure only engine, another one security configurable Support secure OTP Support secure debug Support secure OS Except CPU, the other masters in the SoC can also support security and non-security mode by software-programmable Some slave components in SoC can only be addressed by security master and the other slave components can be addressed by security master or non-security master by software-programmable System SRAM (share memory), security programmable. External DDR space can be divided into 16 parts, each part can be software-programmable to be enabled by each master Mailbox One Mailbox in SoC to service CPU and MCU communication Support four mailbox elements, each element includes one data word, one command word register and one flag bit that can represent one interrupt RK3528 Datasheet Rev 1.0 BY SCENSMART Provide 32 lock registers for software to use to indicate whether mailbox is occupied 1.2.5 Video CODEC Video Decoder Real-time video decoder of MPEG-1, MPEG-2, MPEG-4 H.263, H.264/AVC, H.265/HEVC, MVC VC-1 AVS, AVS+,AVS2 MMU Embedded Supports frame timeout interrupt, frame finish interrupt and bit stream error interrupt Error detection and concealment support for all video formats Output data format YUV420 semi-planar, YUV400(monochrome), YUV422 is supported by H.264 H.264/AVC BP/MP/HP profile @ level 5.1; H.264/AVC MVC; up to 4Kx2K @ 60fps H.265/HEVC Main/Main10 profile @ level 5.1 High-tier; up to 4Kx2K @ 60fps AVS2 4KX2K @60fps MPEG-1, Main profile, up to 1080P @ 60fps MPEG-2, SP@ML, MP@HL, up to 1080P @ 60fps MPEG-4, ASP profile @ level 5, up to 1080P @ 60fps AVS, Jizhun profile @ level 6.0; up to 1080P @ 60fps AVS-P16 (AVS+), up to 1080P @ 60fps H.263, up to 576P @ 60fps VC-1, SP@ML, MP@HL, AP@L0-3, up to 1080P @ 60fps Video Encoder Support video encoder for H.264, [email protected] H.264 maximum frame rate is up to 1920×1080 @60fps Capable of encoding HEVC Main Profile @ L4.1 High-tier H.265 resolution and frame rate are up to 1920×1080 @60fps JPEG encoder included 1.2.6 JPEG Decoder JPEG decoder Input JPEG file : YCbCr 4:0:0, 4:2:0, 4:2:2, 4:4:0, 4:1:1 and 4:4:4 sampling formats Output raw image : YCbCr 4:0:0, 4:2:0, 4:2:2, 4:4:0, 4:1:1 and 4:4:4 semi-planar Decoder size is from 48×48 to 8176×8176(66.8Mpixels) Support JPEG ROI(region of image) decode Maximum data rate is up to 76million pixels per second 1.2.7 Image Enhancement (VDPP module) Image format support Input data: YUV420/YUV422 Output data: YUV420/YUV422/YUV444 YUV swap UV SP/P BT601_l/BT601_f/BT709_l/BT709_f color space conversion YUV up/down sampling De-interlace 3×5 Y motion detection matrix Source width up to 1920 Configured high frequency de-interlace I4O2 (Input 4 field, output 2 frame) /I4O1B/I4O1T/I2O1B/I2O1T mode Post-Processing Support DMSR Support ZME(polyphaser filter based zoom in/zoom out) RK3528 Datasheet Rev 1.0 BY SCENSMART 1.2.8 2D Graphics Engine 2D Graphics Engine: Source formats: ABGR8888, XBGR888, ARGB8888, XRGB888 RGB888, RGB565 RGBA5551, RGBA4444 YUV420 planar, YUV420 semi-planar YUV422 planar, YUV422 semi-planar YUV 10-bit for YUV420/422 semi-planar BPP8, BPP4, BPP2, BPP1 Destination formats: ABGR8888, XBGR888, ARGB8888, XRGB888 RGB888, RGB565 RGBA5551, RGBA4444 YUV420 planar, YUV420 semi-planar YUV422 planar, YUV422 semi-planar Pixel Format conversion, BT.601/BT.709 Max resolution: 8192×8192 source, 4096×4096 destination BitBLT Two source BitBLT: A+B=B only BitBLT, A support rotate and scale when B fixed A+B=C second source (B) has same attribute with (C) plus rotation function Color fill with gradient fill, and pattern fill High-performance stretch and shrink Monochrome expansion for text rendering New comprehensive per-pixel alpha (color/alpha channel separately) Alpha blending modes including Java 2 Porter-Duff compositing blending rules, chroma key, pattern mask, fading Dither operation 0, 90, 180 and 270-degree rotation x-mirror and y-mirror rotation operation 1.2.9 Video OUT Display Interface Support HDMI 2.0b output up to 4K 10bit @60Hz TV interface: TV encoder 10bit out for DAC HDMI interface: 24 bit (RGB888 YCbCr444), 30 bit(RGB101010,YCbCr 420, YCbCr 444) Max output resolution 4K for HDMI, 480i/576i for CVBS Support 1 cluster layer, 4 smart layer Support HDR10, HLG HDR, Vivid HDR 1.2.10 HDMI Compliant HDMI 2.0b Support YUV420 4k x 2k @ 60fps Support for 4k x 2k and 3D video formats Support for up to 10.2bps bandwidth HPD input analog comparator Compliance HDMI compliance Test specification 1.4 and 2.x Support HDCP 1.4 and 2.2 1.2.11 Audio Interface I2S0/I2S2 with 2 channel Up to 2 channels for TX and 2 channels RX path Audio resolution from 16bits to 32bits Sample rate up to 192KHz RK3528 Datasheet Rev 1.0 BY SCENSMART Provides master and slave work mode, software configurable Support 3 I2S formats (normal, left-justified, right-justified) Support 4 PCM formats (early, late1, late2, late3) I2S and PCM cannot be used at the same time I2S0 connect to GPIO I2S2 connect to Audio CODEC, RX path not supported I2S1/I2S3 with 8 channel Up to 8 channels TX and 8 channels RX path Audio resolution from 16bits to 32bits Sample rate up to 192KHz Provides master and slave work mode, software configurable Support 3 I2S formats (normal, left-justified, right-justified) I2S1 connect to GPIO I2S3 connect to HDMI, RX path not supported PDM Up to 8 channels Audio resolution from 16bits to 24bits Sample rate up to 192KHz Support PDM master receive mode SPDIF SPDIF connect to HDMI and GPIO Audio CODEC 24bit DAC Support Line-out Support Mono, Stereo channel performance Integrated digital interpolation and decimation filter. Sampling rate of 8kHz/12kHz/16kHz/24kHz/32kHz/44.1KHz/48KHz/96KHz 1.2.12 Connectivity SDIO interface Compatible with SDIO 3.0 protocol 4bits data bus widths TS interface Supports 2 TS input channels. Supports 4 TS Input Mode: sync/valid mode in the case of serial TS input; nosync/valid mode, sync/valid, sync/burst mode in the case of parallel TS input. Supports 2 TS sources: demodulators and local memory. Supports 2 Built-in PTIs (Programmable Transport Interface) to process TS simultaneously, and Each PTI supports: 96 PID filters. TS descrambling with 8 sets of Control Word under CSA2.0 standard 32 PES/ES filters with PTS/DTS extraction and ES start code detection. 16 PCR extraction channels 96 Section filters with CRC check, and three interrupt mode: stop per unit, full-stop, recycle mode with version number check PID done and error interrupts for each channel PCR/DTS/PTS extraction interrupt for each channel Supports 1 PVR (Personal Video Recording) output channel. 1 built-in multi-channel DMA Controller. Support MMU Smart Card Support ISO-7816 RK3528 Datasheet Rev 1.0 BY SCENSMART Support card activation and deactivation Support cold/warm reset Support Answer to Reset(ATR) response reception Support T0 for asynchronous half-duplex character transmission Support T1 for asynchronous half-duplex block transmission Support automatic operating voltage class selection Support adjustable clock rate and bit (baud) rate Support configurable automatic byte repetition SPI Controller Support serial-master and serial-slave mode, software-configurable DMA-based or interrupt-based operation Embedded two 32x16bits FIFO for TX and RX operation respectively Support 2 chip-selects output in serial-master mode 2 on-chip SPI controller UART Controller 8 on-chip UART controller DMA-based or interrupt-based operation UART0/1/2Embedded two 64Bytes FIFO for TX and RX operation respectively Support 5bit,6bit,7bit,8bit serial data transmit or receive Standard asynchronous communication bits such as start, stop and parity Support different input clock for UART operation to get up to 4Mbps or another special baud rate Support non-integer clock divides for baud clock generation Support auto flow control mode I2C controller 8 on-chip I2C controller Multi-master I2C operation Support 7bits and 10bits address mode Software programmable clock frequency and transfer rate up to 400Kbit/s in the fast mode Serial 8bits oriented and bidirectional data transfers can be made at up to 100Kbit/s in the standard mode MAC 10/100/1000 Ethernet Controller Support 10/100/1000 Mbps data transfer rates with the RGMII interfaces Support 10/100 Mbps data transfer rates with the RMII interfaces Support both full-duplex and half-duplex operation Supports IEEE 802.1Q VLAN tag detection for reception frames Support detection of LAN wake-up frames and AMD Magic Packet frames Support checking IPv4 header checksum and TCP, UDP, or ICMP checksum encapsulated in IPv4 or IPv6 datagram Support for TCP Segmentation Offload (TSO) and UDP Fragmentation Offload (UFO) MAC 10/100M Ethernet controller and MAC PHY Support one Ethernet controllers Support 10/100-Mbps data transfer rates with the RMII interfaces Support both full-duplex and half-duplex operation USB 2.0 OTG interface Compatible Specification Universal Serial Bus Specification, Revision 2.0 Extensible Host Controller Interface for Universal Serial Bus (xHCI), Revision 1.1 Support Control/Bulk/Interrupt/Isochronous Transfer RK3528 Datasheet Rev 1.0 BY SCENSMART USB 2.0 Host interface Support one USB2.0 Host Compatible with USB 2.0 specification Supports high-speed(480Mbps), full-speed(12Mbps) and low-speed(1.5Mbps) mode Support Enhanced Host Controller Interface Specification (EHCI), Revision 1.0 Support Open Host Controller Interface Specification (OHCI), Revision 1.0a Multi-PHY Interface Support multi-PHYs with PCIe2.1/USB3.0 One USB3 Host controller One PCIe2.1 controller USB 3.0 xHCI Host Controller Support 1 USB2.0 port and 1 Super-Speed port Concurrent USB3.0/USB2.0 traffic, up to 8.48Gbps bandwidth Support standard or open-source xHCI and class driver Static USB3.0 Device Static USB3.0 xHCI host USB3.0/USB2.0 OTG A device and B device basing on ID PCIe2.1 interface Compatible with PCI Express Base Specification Revision 3.0 Support Root Complex(RC) mode Support 2.5Gbps and 5.0Gbps serial data transmission rate per lane per direction Support one lane 1.2.13 Others Multiple group of GPIO All of GPIOs can be used to generate interrupt to CPU Support level trigger and edge trigger interrupt Support configurable polarity of level trigger interrupt Support configurable rising edge, falling edge and both edge trigger interrup HDMI 5V IO 3.3V power supply, 5V voltage tolerance 4 IOs for HDMI HPD/CEC/DDC connection Temperature Sensor(TS-ADC) 10-bits ADC up to 50KS/s sampling rate -40~125℃℃ temperature range and 5℃℃ temperature resolution Successive Approximation ADC (SARADC) 10-bit resolution Up to 1MS/s sampling rate 4 single-ended input channels Current consumption: 0.5mA @ 1MS/s OTP Support 8192bits Support Idle, Read, Program operation Support boot function Support Bist function Package Type: WBBGA401L (body:13.3mm x 13.5mm ;ball size: 0.3mm ;ball pitch: 0.65/0.6mm) 点击查看更多产品的Datasheet。 |

【本文地址】

| 今日新闻 |

| 推荐新闻 |

| 专题文章 |